基于USRP的DVB-T接收机实现

陈为刚,赵 干,李 思,杨晋生

(天津大学电子信息工程学院,天津300072)

欧洲地面数字电视广播(DVB-T)标准采用编码正交频分复用(Coded Orthogonal Frequency Division Multiplexing,COFDM)技术,具备较高的频谱利用效率和强大的抗多径干扰能力[1]。依据该标准建立的地面数字电视系统正为全世界范围内的电视用户提供标清和高清电视节目传输服务。

目前用于DVB-T信号接收的设备多采用专用功能的硬件芯片实现,此种实现架构凭借运行效率高、性能稳定等优点得到了众多设备生产商的认可。但该实现架构存在如下缺点:首先,开发过程中较高的硬件制作成本导致不能充分对比不同设计方案的优劣性;其次,难以伴随数字电视传输标准的发展实现设备的快速更新。随着软件无线电概念的提出和发展,可通过模/数转换尽早实现信号数字化,并通过各种数字信号处理设备完成基带信号处理[2]。基于此方式可得到一种新的实现架构,即采用软件无线电架构实现DVB-T信号接收。采用软件无线电架构实现DVB-T接收机具有开发周期短和灵活度高的优点,可以快速实现对不同设计方案的验证和对比。意大利比萨大学研究小组利用通用软件无线电外设(Universal Software Radio Peripheral,USRP)实现 DVB-T 发射机,证明了采用软件无线电架构的可行性[3]。但是,考虑到接收端算法较发送端更为复杂,利用软件无线电架构实现有一定的困难,因此,本文依据欧洲地面数字电视广播标准,基于由USRP和通用计算机组成的软件无线电平台,实现DVB-T接收机。

1 软件无线电与USRP

软件无线电是指以通用、标准、模块化的硬件平台为依托,通过软硬件编程实现无线电处理的各种功能[4]。相比功能单一的硬件电路,软件无线电的一个显著特性是在软硬件方面都具备可重构性,即在不改变软硬件结构的情况下,可采用不同的参数配置和算法设计实现不同的无线电功能。

本文采用的软件无线电平台由USRP和通用计算机组成。USRP是一套基于数字中频架构的可配置软件无线电射频前端,由母板和覆盖不同频段的射频子板组成,结构如图1所示。在接收路径中,射频子板的功能是对天线接收的信号进行正交下变频,产生I、Q两路中频模拟信号。母板主要由12位模/数转换器(ADC)芯片、FPGA芯片和USB控制器芯片构成。ADC芯片完成I、Q路中频模拟信号的数字采样;FPGA芯片对ADC采样得到的中频信号进行数字下变频,并通过级联梳状滤波器对采样值进行可变速率的抽取,形成低速率的基带采样信号;USB控制器芯片用于控制USRP与通用计算机间的基带信号传输。通用计算机采用软件编程实现基带信号的后续处理。

图1 USRP结构

DVB-T标准在现有的甚高频(VHF)和特高频(UHF)频段提供地面数字电视信号的传输服务。本文采用WBX宽带子板,其频率覆盖50 MHz~2.2 GHz,满足基本频段要求。

2 接收机实现

2.1 实现架构

根据实现功能的不同,接收机可分为三个部分:USRP射频前端、内接收机和外接收机。接收机实现架构如图2所示。USRP射频前端实现接收信号的下变频、模/数转换和下采样处理,将天线接收的模拟信号转换为基带数字信号;内接收机完成基带数字信号的定时和频率同步,并实现对信道参数的估计和均衡处理;外接收机对同步均衡后的信号进行解调、信道译码和视频解码,实现接收视频流的实时播放。

图2 接收机实现架构

2.2 USRP 射频前端

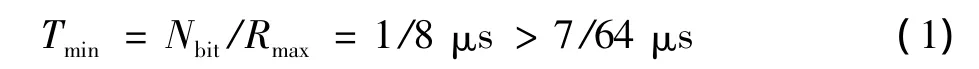

USRP为接收机的射频前端,可配置参数主要包括母板FPGA抽取系数和子板射频中心频率。DVB-T标准定义了6 MHz、7 MHz和8 MHz三种信道带宽模式。三种带宽模式编码映射方式、交织方式和帧结构完全相同,唯一不同的是采样周期Ts,分别等于7/48 μs、1/8 μs和7/64 μs。采用第一代USRP作射频前端时,受限于USB 2.0总线的传输速率(Rmax=32 Mbyte/s),在I、Q路复采样信号量化精度为Nbits=32 bit的情况下,最小采样周期为

不满足8 MHz信道带宽模式对采样周期的要求。接收机实现中针对7 MHz信道带宽模式,在USRP模/数转换器芯片AD9862固定采样速率为64 MSample/s(兆采样/s)情况下,FPGA抽取系数设置为8,即满足该模式对采样周期的要求。在射频中心频率配置方面,选择与DVB-T固定频道中心频率一致。

2.3 内接收机

国内外学者已针对DVB-T信号的接收提出了众多同步和信道估计方案,本文在考虑算法性能和复杂度的基础上,选择恰当算法实现内接收机各信号处理模块。整个同步过程分为捕获阶段和跟踪阶段。捕获阶段完成定时、频率偏差值的大致捕获;跟踪阶段完成剩余偏差值的估计和跟踪校正。接收机进入稳定跟踪状态之后,再进行信道估计和频域均衡。

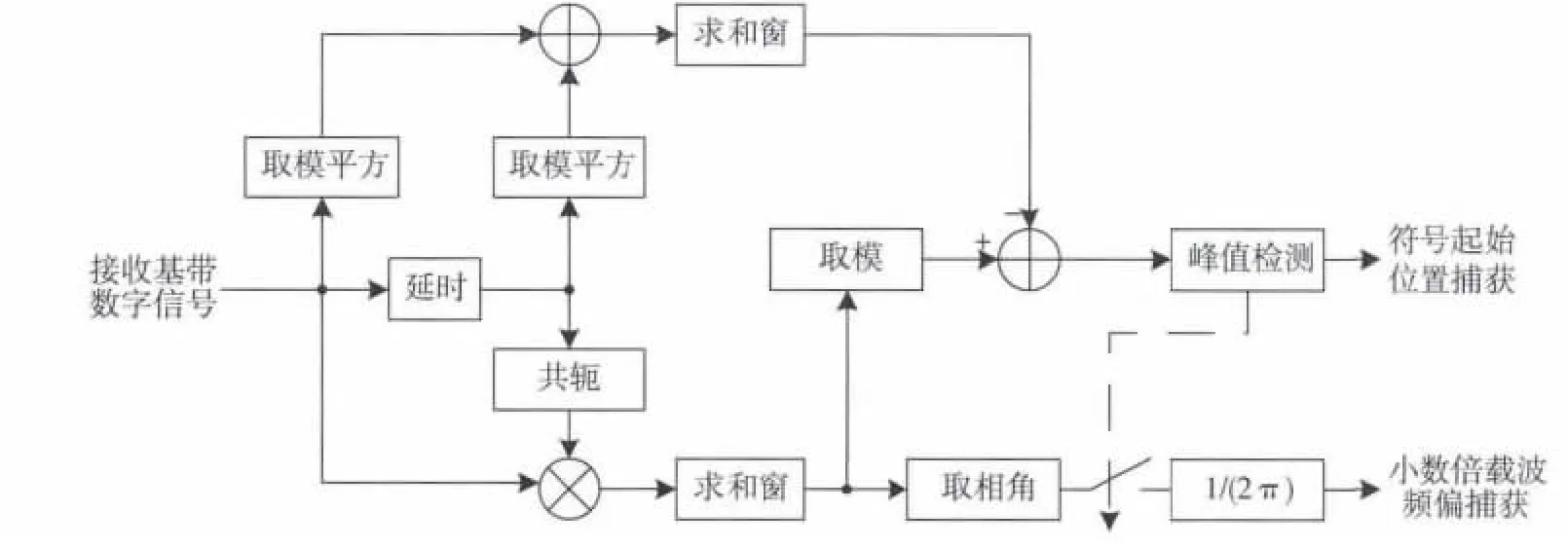

1)符号定时与小数倍载波频偏捕获

内接收机运行过程中,首先需要完成对OFDM符号起始位置的捕获。内接收采用基于OFDM符号循环前缀的最小均方误差估计算法,同时实现对OFDM符号起始位置和小数倍载波频偏值的捕获[5]。该算法不需要对接收信噪比进行估计,可有效降低捕获的实现复杂度,实现结构如图3所示。

图3 符号定时与小数倍载波频偏捕获实现结构

2)整数倍载波频偏捕获

接收机与发射机晶振频率的差别,可能造成较大的载波频率偏差。若传输过程中存在整数倍载波频偏,则FFT变换后OFDM符号中所有子载波产生整体移位,导致解调数据完全错误。DVB-T标准中连续导频在每个OFDM符号中占用固定子载波,内接收机基于连续导频采用频域相关算法,实现对整数倍载波频偏值的捕获[6]。采用频域相关算法,运算复杂度与使用连续导频的数目成正比。DVB-T标准2K模式共有45个连续导频,内接收机实现中使用直流载波附近的15个连续导频,完成整数倍载波频偏值的捕获。

3)符号定时精同步

完成对OFDM符号起始位置的捕获后,剩余符号定时偏差主要有两部分:一部分是符号起始位置捕获值与实际值的差值;另一部分是采样偏差导致的符号定时漂移。DVB-T标准中离散导频在每个OFDM符号中等间隔分布,内接收机采用基于相邻离散导频相位差的估计算法,实现对OFDM符号定时偏差值的精确估计[7]。

4)剩余载波频偏估计

剩余载波频偏导致接收星座点发生相位旋转并具有累加效应。内接收机基于相邻OFDM符号连续导频相位差,采用最小平方准则估计算法,实现对剩余载波频偏值的估计[8-9]。内接收机实现中预先建立最小平方准则系数矩阵,并存储为查找表,可有效避免重复运算。此外,为减小估计抖动,首先将剩余载波频偏估计值通过环路滤波器进行平滑滤波,然后再进行反馈和补偿。

5)信道估计与均衡

衰落信道下各子载波信号会产生不同程度的相位旋转和幅度畸变,需要进行信道估计和均衡,保证相干解调的正确进行。内接收机基于每个OFDM符号中等间隔分布的离散导频信号,首先在频域内采用最小二乘算法估计导频位置的信道响应值;然后,采用频域线性插值方法预测非导频位置处的信道响应值;最后,在频域内采用相除方式实现对全部子载波信号的均衡处理。

2.4 外接收机

外接收机根据DVB-T标准定义的发射信号生成方式,反向处理恢复原始传送流(Transport Stream,TS)。为正确提取系统信息,同时保证RS码译码器的输入为完整RS码码字,外接收机首先需要实现超帧同步。超帧同步利用本地存储的同步字序列与差分解调后传输参数信令(Transmission Parameter Signaling,TPS)中的同步字序列进行滑动相关,若相关结果大于预设阈值且帧号序列为“00”,则可确定超帧的起始位置。

超帧同步后,对每个OFDM符号中的数据子载波进行硬判决解调和解内交织,并将解交织比特序列送入卷积码译码器。卷积码译码器采用硬判决维特比译码算法进行译码。译码完成后,将译码信息比特序列转换为字节序列,并采用移位寄存器法实现基于字节的解卷积交织[10]。卷积交织/解交织产生的总延时为11个RS码码字,因此RS码译码器在接收11个RS码码字后启动。数据解扰是在检测到取反同步字节(0xB8)后,将接收数据与DVB-T标准定义的伪随机序列进行异或运算。最后,借助开源多媒体音视频处理工具FFmpeg,对接收TS流进行解码和播放。

3 软件实现

接收机实现中,USRP的参数配置以及内接收机和外接收机对基带信号的处理全部在通用计算机中完成。选择恰当的信号处理方式并设计合理的软件流程,对提高接收机程序运行效率尤为重要。同时,为实现接收视频的实时播放,需完成视频显示界面的开发。

3.1 软件流程

在通用计算机中实现基带信号处理的方式有两种:借助软件开发工具如GNU Radio、LabVIEW等,通过构建流图并创建信号处理模块实现;调用USRP应用程序编程接口(Application Programming Interface,API)函数读取基带信号,并编写信号处理函数实现。本文采用第二种方式,该方式不必使用其他软件,可实现对各运算单元输入/输出数据的完全控制,因此通用性更强。

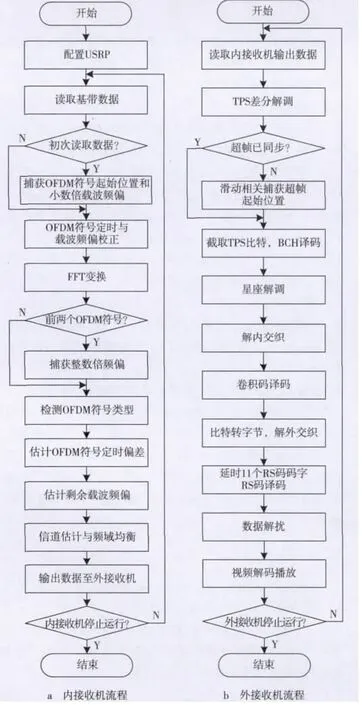

内接收机和外接收机流程如图4所示,各运算单元采用封装的C++函数实现,封装函数的接口参数为本运算单元的输入、输出数据。接收机主程序通过控制函数调用,实现各运算单元的连接,保证数据处理的连续性。

图4 接收机流程

3.2 多线程处理

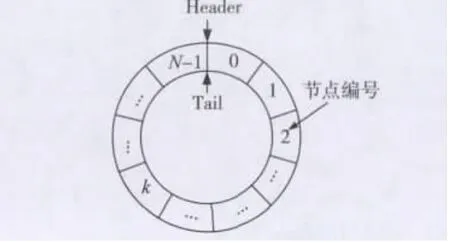

为提高程序运行效率,接收机编程实现中采用多线程模式。根据实现复杂度,将整个接收机划分为3个线程:内接收机线程、外接收机线程和视频解码播放线程。各线程独立运行,并通过循环阻塞队列实现线程间的数据交互,循环阻塞队列结构如图5所示。

图5 循环阻塞队列结构

接收机程序启动后,首先申请能够存放N×M_BYTES byte的内存,其中N为队列节点数目,M_BYTES表示每个节点的字节长度。读写线程通过调用get函数和put函数,实现队列数据的读取和写入操作。若队列空,则get函数阻塞;若队列满,则put函数阻塞。接收机实现中,需要建立两个循环阻塞队列,分别用于实现内接收机线程与外接收机线程、外接收机线程与视频解码播放线程间的数据交互。各线程并行运行,可较大程度提高程序运行效率,保证接收机实时稳定运行。

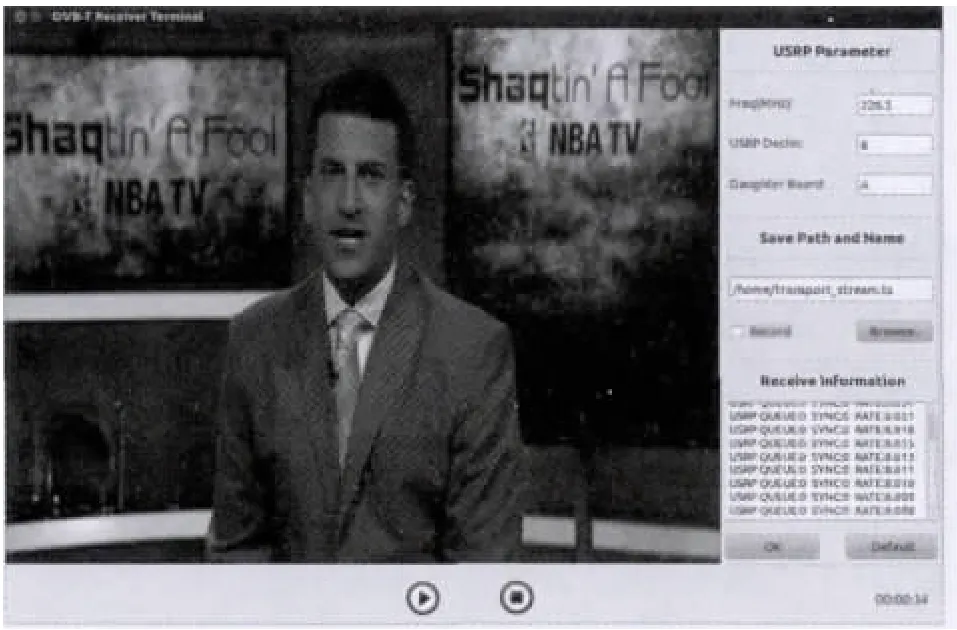

3.3 视频显示界面

在实现接收机的基础上,进一步采用QT用户图形化界面开发工具,开发了视频显示与配置界面,如图6所示。通过该界面可对USRP母板FPGA抽取系数和子板射频中心频率进行配置,启动后可实现接收视频流的实时播放。

图6 接收机视频显示界面(截图)

4 测试与验证

针对所实现接收机,利用标准调制信号验证其接收功能的正确。发射端采用荷兰DekTec公司生产的调制卡DTA-115产生符合DVB-T标准的调制信号;接收端采用主频3.4 GHz,Intel Core i7-3770 CPU的通用计算机作为宿主机运行接收机程序。经验证,接收机可实现对7 MHz信道带宽、2K模式、内码码率1/2、QPSK映射、1/4保护间隔模式信号的实时稳定接收,接收TS流比特速率为4.354 Mbit/s。

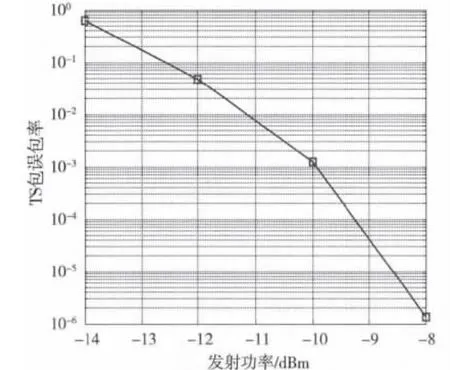

进一步,在室内场景下对接收TS包的误包率进行了测试。实际测试中,射频中心频率为226.5 MHz,收发天线距离为3.5 m,测试结果如图7所示。发射端通过设定功率参数改变发射功率的大小,接收机根据RS码译码结果,对接收TS包的误包率进行统计。可以看出,在发射功率为-8 dBm时,TS包误包率降低至1.3×10-6。该系统被用于海洋上综合业务通过TS流的传输,具有良好的扩展性和较低的成本。

图7 TS包误包率测试结果

5 小结

本文依据欧洲地面数字电视传输标准,选择合适的信号同步和信道估计算法,基于由通用软件无线电外设和通用计算机组成的软件无线电平台实现了DVB-T接收机。测试表明,接收机可实现对固定模式DVB-T信号的稳定接收和视频实时播放。

[1]ETSI EN 300 744 V1.6.1,Digital Video Broadcasting(DVB):framing structure,channel coding and modulation for digital terrestrial television[S].2009.

[2]MITOLA J.Software radios:survey,critical evaluation and future directions[J].IEEE Aerospace and Electronic Systems Magazine,1993,8(4):25-36.

[3]PELLEGRINI V,BACCI G,LUISE M.Soft-DVB:a fully-software GNURadio-based ETSI DVB-T modulator[EB/OL].[2013-07-10].http://tvlivre.org/sites/tvlivre/files/PellegriniBacciLuise_WSR08_CR.pdf.

[4]陶玉柱,胡建旺,崔佩璋.软件无线电技术综述[J].通信技术,2011,44(1):37-39.

[5]LEE D,CHEUN K.Coarse symbol synchronization algorithms for OFDM systems in multipath channels[J].IEEE Communications Letters,2002,6(10):446-448.

[6]HAN D S,SEO J H,KIM J J.Fast carrier frequency offset compensation in OFDM systems[J].IEEE Trans.Consumer Electronics,2001,47(3):364-369.

[7]AI B,YANG Z X,PAN C Y,et al.On the synchronization techniques for wireless OFDM systems[J].IEEE Trans.Broadcasting,2006,52(2):236-244.

[8]SPETH M,FECHTEL S,FOCK G,et al.Optimum receiver design for OFDM-based broadband transmission-Part II:A case study[J].IEEE Trans.Communications,2001,49(4):571-578.

[9]周加铳.DVB-T COFDM接收系统中关键技术研究与设计[D].上海:同济大学,2007.

[10]陈庆旭,孙曼,植涌.基于FPGA的DVB-C系统编码器的设计[J].电视技术,2012,36(3):4-6.