基于OR1200 的SoC 设计软硬件协同仿真验证

罗秋娴,张 贺,罗国成

(南京航空航天大学 电子信息工程学院,江苏 南京 210016)

片上系统(System on Chip,SoC)一般包括可配置的通用IP 核和用户自行设计的专用IP 核组成的系统。系统完成后,需要对芯片进行验证,为提高芯片投片的成功率并缩减验证时间,提出了软硬件协同验证[1]。但国内大部分研究对软硬件协同仿真介绍较少,更多关注在软硬件划分算法的研究上。对基于OR1200(OpenRISC 1200)的片上系统设计,软件的开发与仿真,主要在GNU 工具链中通过编译器、调试器(Debugger)和处理器虚拟原型仿真器来实现,将开发的应用程序编译生成二进制的仿真向量,然后将仿真向量在仿真器中运行。本文针对基于OR1200 处理器的片上系统开发,软硬件协同设计的仿真验证进行介绍,利用GNU 工具链和仿真器,对搭建的系统实例进行软件开发、仿真和综合验证,最终利用FPGA 开发板资源,进一步对系统进行板上验证。

1 OR1200 简介

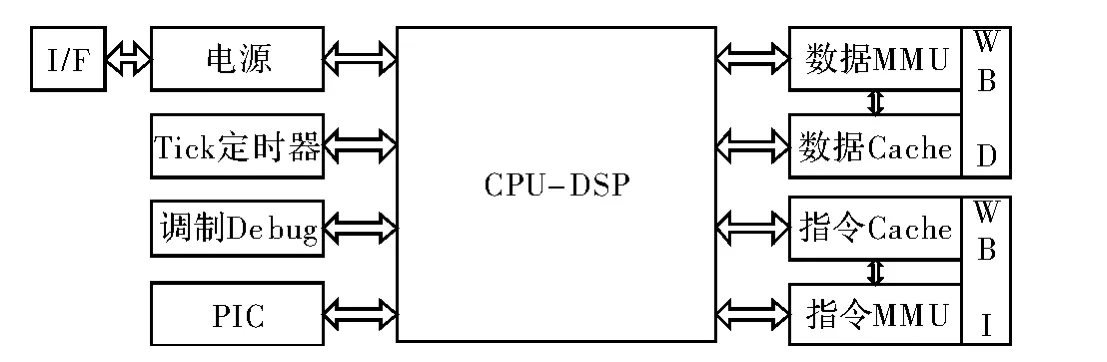

OR1200 是OpenRISC 处理器簇的一款32 位实现,完全开放源码的处理器,主要结构如图1 所示,其执行特征包括32 位整数指令、DSP 浮点指令和高速或虚拟内存等[2]。

图1 CPU 基本架构

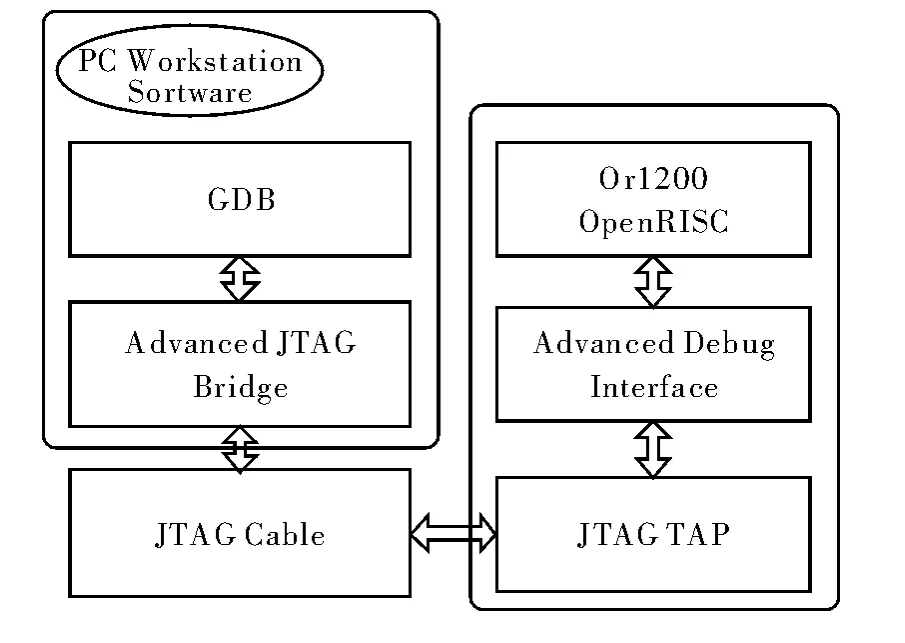

OR1200 的外部数据和地址总线接口符合开源总线WishBone 标准,且提供了专门的调试模块进行片上调试,包括OR1200 本身的调试单元和JTAG 调试接口模块。调试接口提供外置的JTAG 到处理器的接口,由电脑终端调试器GDB(GNU Debugger)控制的外部接口模块,通过寄存器控制调试接口,从而产生控制处理器工作信号,完成在FPGA 开发板上的片上调试[3],验证体系如图2 所示。

图2 软硬件协同验证体系

2 硬件系统搭建

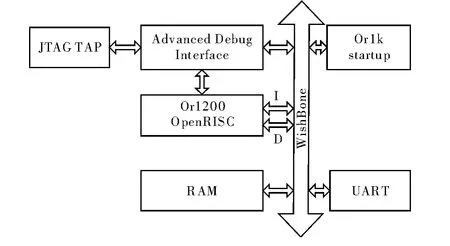

文中用于搭建硬件实例的主要为通用IP 核,包括:RISC 处理器OR1200、开源总线WishBone、串口UART 16550(Universal Asynchronous Receiver/Transmitter,UART)、高级调试接口(Advanced Debug Interface)以及JTAG 等,硬件结构如图3 所示。总线选择WishBone开源总线。该总线是“轻量级”规范,接口简单紧凑,需要互联的逻辑少,适合用于搭建硬件。高级调试接口主要用于带有处理器的片上系统设计代码的下载和源代码级调试,适用于OR1200 处理器和WishBone 总线的目标系统,并支持多种下载器类型。JTAG 核包含测试访问接口(Test Access Port,TAP)及其控制器、指令寄存器、数据寄存器。本文利用JTAG 接口访问处理器的调试模块,进行软件程序的加载与执行,并通过串口测试程序将系统运行的结果在电脑终端显示,实现软硬件在FPGA 平台上的验证。

图3 硬件系统模块图

硬件系统在Quartus II 中搭建,由于要在Altera 的器件中实现验证,并对OR1200 处理器核的源代码进行适当的剪裁和修改。

OR1200 源码到FPGA 的移植:(1)OR1200_define.v 定义所需要子模块的配置,以及内存等所使用的资源类型,从而使得整个设计合理地占用FPGA 的资源。(2)对于串口控制器,数据接收和发送FIFO 都调用了内存模块,需要一个双口内存。该双口RAM 可以用Quartus II 的Mega wizard 生成。(3)由于FPGA 的时钟晶振是50 MHz,与OR1200 的工作频率不同,因而需要插入PLL 将时钟频率通过倍频/分频调整到所需值。同样可以用Mega wizard 生成[2]。

3 软件设计

3.1 建立交叉编译工具链

软件平台包括编译器合集GCC(GNU Complier Collection,GNU)、编译测试软件Binutils 和调试工具GDB。Binutils 工具是一组二进制工具集,主要包括汇编器,连接器,拷贝目标文件的内容并进行格式转换等[4-5]。OR1Ksim 是OpenRISC 处理器系列专用的仿真器,提供了主要外围设备和系统控制器的模型,且具有可拓展性,可以仿真后缀名为.or32 的程序。本文使用搭建好的软件开发平台OpenRISC_Ubuntu。

源代码到可执行程序需要经过预处理、编译、汇编和链接这4 个阶段。执行过程:(1)在复位向量上开始执行。(2)设置适当的寄存器,如处理器的时钟频率,禁止终端和高速缓存,初始化内存控制器,内存芯片和高速缓存单元,初始化总线接口,初始化板级外设等。(3)执行应用程序与目标机系统硬件通信[6]。

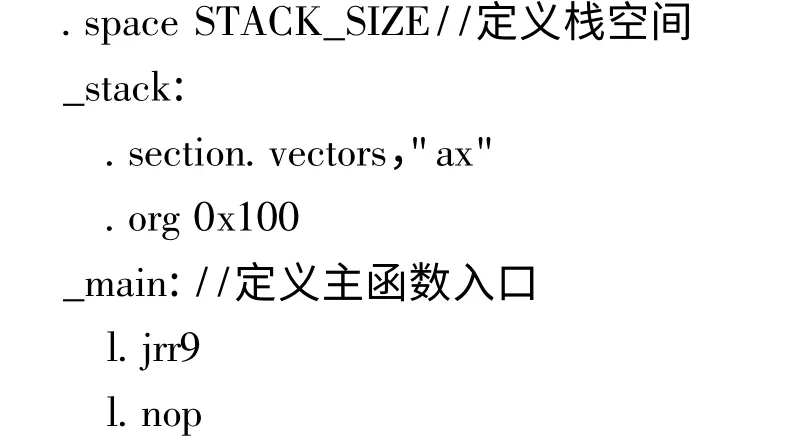

3.2 软件程序编写

主要包括启动程序及软件文件编写。启动程序中,需要定义验证所用的DE2-115 开发板参数;完成处理器本身寄存器的必要初始化工作、栈空间预留、异常的入口处理工作,以及跳转到C 语言的入口函数;制定了链接器的工作方式。部分初始化文件代码如下:

对串口测试主要包含对串口的读和写。编辑uart.c 定义初始化函数、数据发送和接收函数、打印字符函数,完成硬件初始化和实现串口的数据收发。在系统仿真中,即利用串口测试软件,发送“Hello World.”字符,并打印来验证系统设计的正确性。

4 协同仿真验证

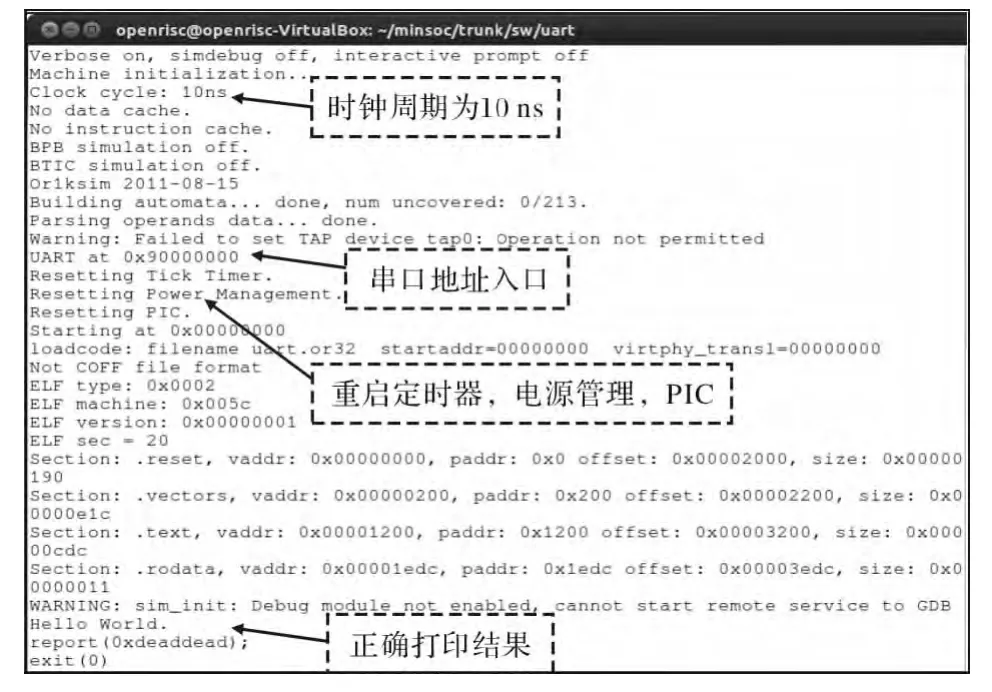

本文采用GNU make 解释器处理文件,对编写的软件代码执行make all 命令,得到编译链接后的二进制文件等,启动仿真器对uart.or32 进行仿真结果如图4所示。可以看出,当前仿真器的状态及运行结果:时钟周期为10 ns,串口地址为0x90000000。信息表明程序正确执行主函数下初始化、通过串口接收并打印所给字符函数。从而完成了针对OR1200 的片上系统设计的软件仿真验证,也为接下来的板上验证做好了前期工作。

图4 软件仿真结果

进一步实现系统在FPGA 开发板的上在线仿真验证:将硬件设计下载到开发板上。在软件开发平台下建立JTAG 调试接口连接[7]。

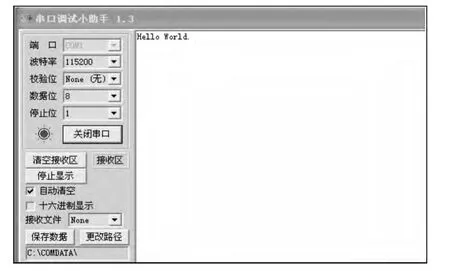

信息表明JTAG 连接的器件型号为EP4CE115F29,即本文中使用开发板芯片型号;JSP(JTAG Serial Port,JTAG 串口接口)待命于软件调试端,调试通道连接成功。启动GDB 调试器,输入远程同步目标命令,建立连接后,将软件加载到已经烧写上硬件设计的开发板中并运行,电脑终端的串口调试助手可以看到软件的运行结果,如图5 所示。正确显示程序打印的字符“Hello World.”,至此完成了基于OR1200 片上系统设计的软硬协同仿真与验证。

图5 串口输出

5 结束语

介绍了基于OR1200 的SoC 设计的软硬件协同验证方法。以通用IP 核搭建的硬件系统模型,使用GNU工具链设计软件并进行仿真,最终在FPGA 开发板上实现软件与硬件交互,完成系统的在线调试与验证。对于基于开源处理器OR1200 的SoC 设计,本文介绍的方法可以普遍用于系统的仿真与验证。

[1] GRIFFITH A.GCC 技术参考大全[M].胡恩华,译.北京:清华大学出版社,2004.

[2] 倪继利,陈曦,李挥.CPU 源代码分析与芯片设计及Linux移植[M].北京:电子工业出版社,2007.

[3] 张琳.基于OR1200 的软件开发平台设计[D].济南:山东大学,2011.

[4] EDELSOHN D,GELLERICH W,HAGOG M,et al.Contributions to the GNU compiler collection[J].IBM Systems Journal,2005,44(2):259-278.

[5] 马晓涛,李波.Linux 系统下嵌入式系统交叉编译链搭建[J].成功:教育,2010(7):290.

[6] 李京波,董利民,吴武臣.SoC 软硬件协同验证中的软件仿真[J].电子工程师,2007,33(1):14-17.

[7] 郑晓光,白国强.一种基于JTAG 的SoC 测试电路设计及实现[J].微电子与计算机,2009,26(1):187-192.