高性能通用数字信号处理器指令分配

(中国电子科技集团公司第三十八研究所集成电路设计中心,安徽合肥230088)

0 引言

目前数字信号处理芯片[1]已经成为高速自动控制、图像处理[2]、通信技术、雷达及各种信号处理中的核心部件。国内可编程超大规模DSP集成电路芯片的研制还处在初步尝试阶段,而针对具有复杂指令集的超大规模集成电路芯片内部指令分配,以及执行单元和总线通道占用调度的电路设计还是个尚待解决的难题。

国际上目前应用最广泛的是美国TI公司的TMS系列和ADI公司的TS系列DSP芯片。ADI公司的两款高性能数字信号处理芯片ADSP TS101S[3]、ADSP TS20XS[4]更具有代表性。

在ADSP TS20XS芯片内有双运算模块,每个运算模块包含1个算数逻辑单元(ALU)、1个乘法器、1个移位器、1个寄存器组和1个通信逻辑运算单元(CLU)。1个指令行中最多有4条运算块指令。

由于ADSP TS20XS芯片在每个运算核内的各类运算单元只有一个,不存在单条运算指令对应多个可执行运算单元的情况,因此与本文所涉及的一个指令行中存在多条指令,每条指令对应一个或多个运算执行单元,且指令可以自动分配运算单元或者可以指定其中的任意一个运算单元的情况有所不同。其指令与运算单元一对一的分配与本文所实现的多对多的自动化分配及存在优先级的指定分配难度是不可比拟的。

这里要解决的是多条同类型指令自动分配或者指定分配至多个运算执行单元的分配难题,其中指定执行的情况又存在多条指令抢占同一个执行单元的情况。这些都将是本文所要解决的重点所在。

1 设计实现

本文项目BWDSP100芯片[5-6]中包括4个运算执行核(X,Y,Z,T),每一个运算执行核包含4个乘法器、8个ALU运算单元、2个移位器、1个特定运算单元和1组64字的寄存器组。1个指令行中最多有16条运算指令。

为达到高效、快速、合理的分配目的,本文提出的分配技术主要包括指令分核模块、指令分类模块、指令分配模块和多核指令分配集成模块等。这些模块共同组合,完成了BWDSP100芯片所有指令的分配任务,实现了可编程超大规模DSP集成电路芯片运算执行资源占用及传输通道调度的完整功能。另外指令分配模块又包括自动分配模块、指定分配模块、优先级选择模块、组合选择模块和输出模块。这些模块以流水的方式协同完成了指令行各种类型指令的分配工作,不同类型指令的分配工作均可以由指令分配模块完成。在指令分类模块后,通过多次例化指令分配模块并设置不同类型指令分配的参数即可完成不同种类指令的分配工作。

高性能通用信号处理器指令分配的具体实施方式主要包括4类:指令分配、单核运算指令分配集成、访存指令分配集成和多核指令分配。

1.1 指令分配

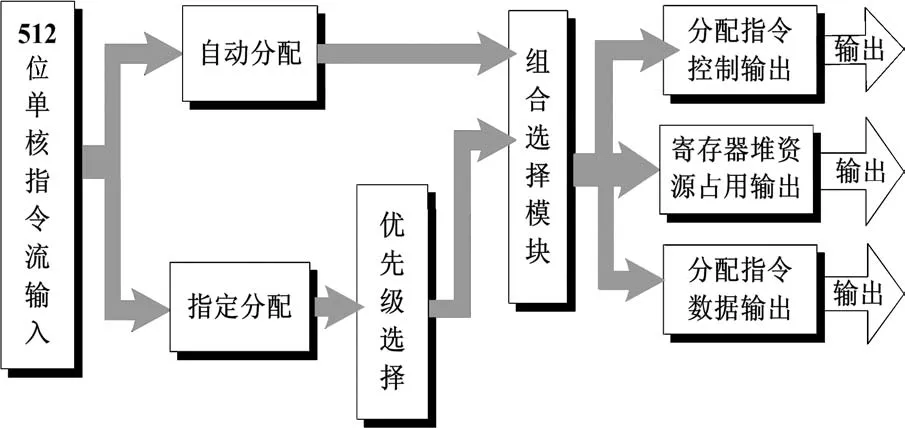

指令分配模块主要解决多条同类型指令对应多个执行单元的分配问题,同时存在指令指定占用1个或者多个执行单元的情况,并包括多条指令抢占同一个运算执行单元的问题。该指令分配模块可适用于各种不同种类指令的分配,其内部的分配电路结构类似,如图1所示。

图1 指令分配结构图

指令分配主要包括以下步骤:

步骤1 将分类后的指令及对应的类别编码分别输入到指定分配和自动分配模块。

步骤2 自动分配模块根据指令类别和指令特征码填写该类指令自动分配标识。根据指令占用运算单元的个数情况,经过自动选择分配单元模块,输出自动分配对应的运算单元编码。其中运算单元占用的数目可以是1~8个不等,根据具体指令类型而定。

步骤3 指定分配模块根据指令类别和指令指定分配特征码填写指令指定分配标识。根据指令指定的运算单元编号,输出该类指令指定分配对应的运算单元编码。其中指定运算单元的数目可以是1~8个不等,并且可以指定相邻2个或者相邻多个运算单元,由指令集的对应指令及相应的标志位确定。

步骤4 指定分配模块输出的结果通过优先级选择模块按照指定优先级排序输出。具有优先指定权的指令经过该选择模块后会优先抢占其指定的运算单元。

步骤5 将指定分配和自动分配的结果输入到组合选择器。指定输出具有对运算单元的优先选择权,在指定分配确定的情况下,选择空闲运算单元的编码按照自动分配模块的分配要求对其余指令自动分配。

步骤6 经过组合选择器的分配编码输入至“寄存器堆资源占用输出”模块、“分配指令控制输出”模块和“分配指令数据输出”模块,得到指令行中该类指令的分配执行结果。

1.2 单核运算指令分配集成

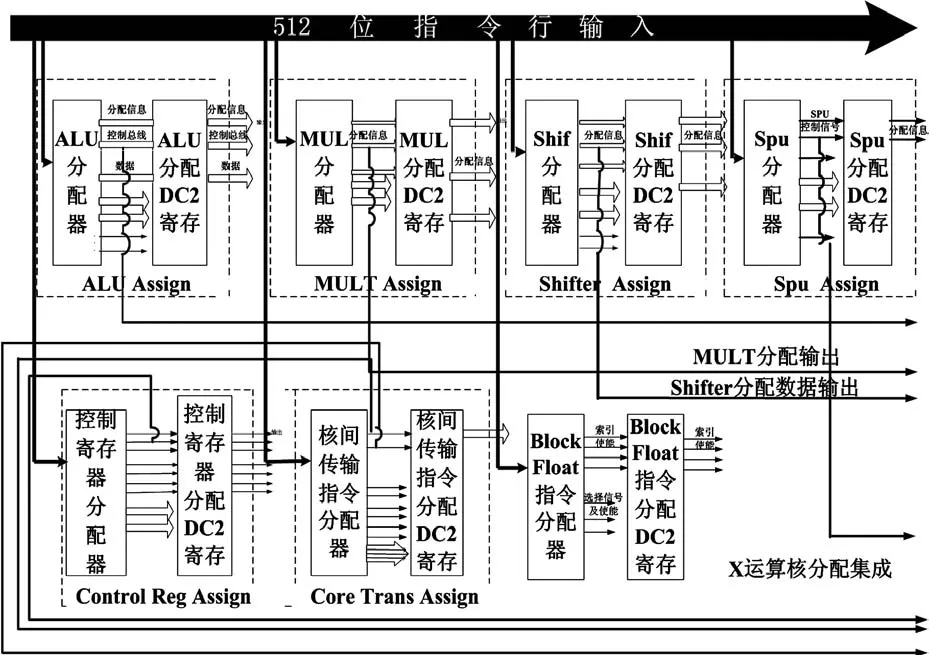

通过指令分配模块得到的是单类指令的分配输出。将运算执行核内所有类型的运算指令分配模块综合集成为一个单核分配模块,如图2为X运算核指令分配集成,主要包括:ALU(加/减法)指令分配器、MULT(乘法)指令分配器、SHIFT(移位)指令分配器、SPU(特殊运算)指令分配器、控制寄存器指令分配器、核间传输指令分配器、块浮点指令分配器以及所有分配输出的时钟寄存器。

图2 X运算核指令分配结构图

1.3 访存指令(数据通道)分配集成

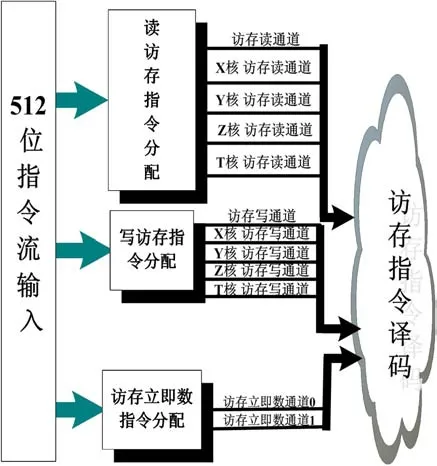

访存指令分配的内部实施步骤与上述情况类似,所不同的是数据通道分配需要按照读、写、立即数操作三种情况进行通道分配,以避免读写冲突。因此数据通道分配相应以上三种类别分别设置了三种不同的通道分配模块(如图3所示):

(1)读访存指令分配 主要实现读访存指令由数据存储器到寄存器堆之间“读”数据通道的占用分配。

(2)写访存指令分配 主要实现写访存指令由数据存储器到寄存器堆之间“写”数据通道的占用分配。

(3)立即数访存指令分配 主要实现立即数访存指令对数据存储器的立即数操作通道占用分配。

图3 访存指令分配结构

1.4 多核指令分配

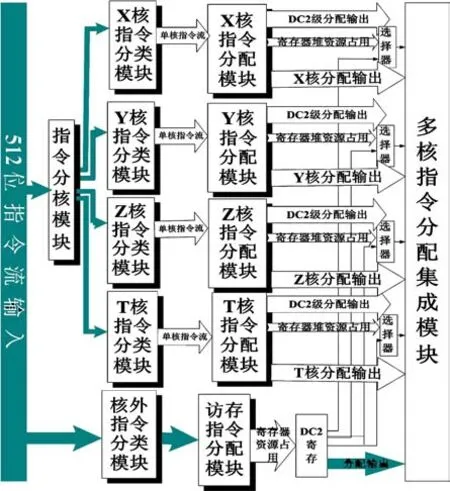

如图4所示,多核指令分配主要包括以下几个步骤:

步骤1 BWDSP100处理器的指令位宽为512位,主要包括执行核外指令和执行核内指令。执行核内指令首先经过指令分核模块,该模块接收到512位指令流,通过对指令核标志位的判断,将指令分成4个512位宽的单核指令,其中4个执行核分别命名为X核、Y核、Z核和T核。

步骤2 指令经过指令分核模块即进入到指令分类模块。并通过对指令特征位的辨识,将指令所属类别进行编码。输出一个与指令行指令逐条对应的类别码。如果指令行某条指令为空,则对应的类别码约定为0。指令分类模块又包括核外指令分类和核内指令分类。其中核外指令分类主要针对访存指令的读、写及立即数指令进行操作;核内指令的分类模块所分类的指令主要有算数逻辑单元(ALU)、乘法器(MULT)、移位器(SHIF)、特殊运算单元(SPU)、控制寄存器、核间传输指令和块浮点运算指令等。

步骤3 经过上述处理后的指令进入到指令分配阶段,相应地将经过步骤2处理后的两路分支——执行核内的单核指令分类结果和执行核外的访存指令分类结果,分别输入到X/Y/Z/T单核指令分配模块或者执行核外的访存指令分配模块,从而得到指令分配的输出结果,包括控制输出、数据输出和寄存器堆资源占用标志输出。

步骤4 每个执行核内设置一个选择器,将所有单核指令分配集成模块、核外指令分配模块、数据通道(访存指令)分配模块的输出经过相应的时钟寄存器并综合输入核间分配选择器,实现核间传输通道交叉占用以及核内外的寄存器堆资源占用的标志选择输出。

步骤5 最后将选择器的输出结果与指令分配输出结果经过多核指令分配集成模块输出整个高性能通用信号处理器芯片的综合分配输出结果。

图4 多核指令分配集成框图

2 实验结果

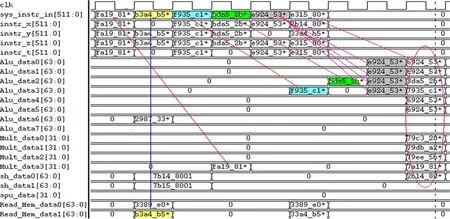

以下利用本文所述的分配技术进行了硬件实现和波形仿真,图5是硬件RTL设计的部分实验仿真结果。分配电路的输入信号是512 bit指令行sys_instr_in,instr_x/y/z/t是指令分核模块的输出,Read_Mem_data0/1是访存数据通道的读指令分配结果,其余信号是X运算核的指令分配输出。

图5 硬件RTL设计仿真结果

从图中可以看到第一个指令fa19_81c8指定分配到第3号乘法器Mult_data3;第二条指令b3a4_b587指定分配到第2个读访存通道Mult_data3;第三条指令f935_c1cc指定分配到第3号ALU运算部件Alu_data3;第四条指令bda5_2b1d指定分配到第3号ALU运算部件Alu_data2;第五条指令e924_5398是可以自动占用4个运算部件的复数运算指令,由图中可以看到该指令自动指定分配到前面4个ALU运算单元上:Alu_data0/1/2/3;第六条指令是多个指令的联合分配,值得说明的是,当Alu2和Alu3分别被指定分配的指令3da5_2b1d和7935_c1cc占用后,占用4个ALU运算部件的指令6924_5398会自动跳过被指定占用的运算部件,分别分配到Alu0、Alu1、Alu4和Alu5。

由仿真波形可见该技术实现了指令指定任意一个运算单元的指定分配,以及指令不指定运算单元时的自动分配。真正实现了存在优先级的指定分配和多对多的自动化分配电路。解决了超大规模集成电路芯片内部指令分配的难题。

3 结束语

本文针对高性能通用数字信号处理器内部的指令分配问题提出了一种解决方法,对该技术的实现步骤进行了详细阐述,可以适用于加、减、乘、除、移位、访存和跳转等各种运算指令,也适用于逻辑运算、选大或选小处理、数据传输、控制寄存器读写指令、核间传输等指令。每种指令对应一个或多个运算执行单元,既可以自动分配也可以指定分配。解决了超大规模集成电路芯片内部指令分配,以及执行单元和总线通道占用电路设计的难题。

[1]Texas Instruments.TMS320C6671 Fixed and Floating Point Digital Signal Processor Data Manual[M].US:Texas Instruments,2012:105-120.

[2]BATEMAN A.DSP算法应用与设计[M].北京:机械工业出版社,2003:1-14.

[3]Analog Devices Inc.ADSP-TS201 Tiger-SHARC Embedded Processor[M].US:Analog Devices Inc,2006:1-80.

[4]刘书明,罗勇江.ADSP TS20XS系列DSP原理与应用设计[M].北京:电子工业出版社,2007:30-31.

[5]中国电子科技集团公司第三十八研究所.BWDSP100软件用户手册[M].合肥:中国电子科技集团公司第三十八研究所,2011:1-20.

[6]史鸿声,穆文争,刘丽.基于“魂芯一号”的雷达信号处理机设计[J].雷达科学与技术,2012,10(2):161-164.SHI Hong-sheng,MU Wen-zheng,LIU Li.Design of Radar Signal Processor Based on HunXin-1 Chip[J].Radar Sciecne and Technology,2012,10(2):161-164.(in Chinese)