基于FPGA的以太网接口设计与实现

李 勋 ,刘文怡

(1.中北大学 电子测试技术国家重点实验室,太原 030051;2.中北大学 仪器科学与动态测试教育部重点实验室,太原 030051)

随着互联网硬件和软件的迅猛发展,以太网接口成为目前使用最广泛的网络接口,具有接口简单、通信速度高、传输距离远、通信协议完善和工作性能稳定等优点,能够实现远程高速数据通信系统[1]。传统以太网常采用主控芯片内部编写以太网协议或在ARM等高性能处理器上运行操作系统,通过操作系统完成TCP/IP等复杂的通信协议,从而实现以太网通信[2],这两种解决方案开发周期长、难度较大、成本较高。然而利用硬件协议栈芯片,只需要通过简单的配置和外部线路连接就可以实现以太网的数据传输功能,这种方法开发难度小、集成度高且运行稳定,已成为实现以太网数据传输的首选方案[3]。

本文设计了一种利用FPGA控制硬件协议栈芯片W5300实现初始化配置、数据传输的以太网接口,并利用上位机UDP调试助手对其进行测试,实现了FPGA和上位机之间通信。

1 硬件设计

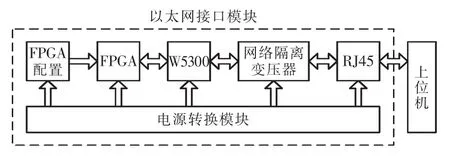

本文设计的以太网接口以FPGA为核心控制器,采用Xilinx公司Spartan-3系列XC3S400芯片,该芯片具有丰富的逻辑资源,易于配置;以太网接口协议芯片使用WIZnet公司生产的硬件协议栈芯片W5300。硬件结构如图1所示,其工作原理:FPGA通过逻辑程序控制W5300数据总线、地址总线及读写、数据位选择信号,通过编程控制这些信号实现对W5300的初始化配置、数据读写及上位机通信。上位机通过UDP调试助手软件设置与接口模块相对应的IP地址,通过发送“数据发送”和“数据接收”命令实现上位机与接口模块中FPGA通信。

图1 以太网接口硬件结构图Fig.1 Ethernet interface hardware structure

硬件协议栈芯片W5300内部集成了10/100 M以太网控制器,MAC和TCP/IP协议栈,所以CPU不需要编写复杂的TCP/IP协议,能够大大地减小硬件接口设计和网络编程的工作量,降低产品的开发难度和缩短开发周期,能够实现可靠稳定的远程数据通信系统。支持8个独立端口同时连接,通信速率最高可达到80 Mb/s;与主机接口支持8/16 bit数据总线,支持2种主机接口模式;内部有128 KB TX/RX存储器,可根据端口通信数据吞吐量动态调整其分配[4]。

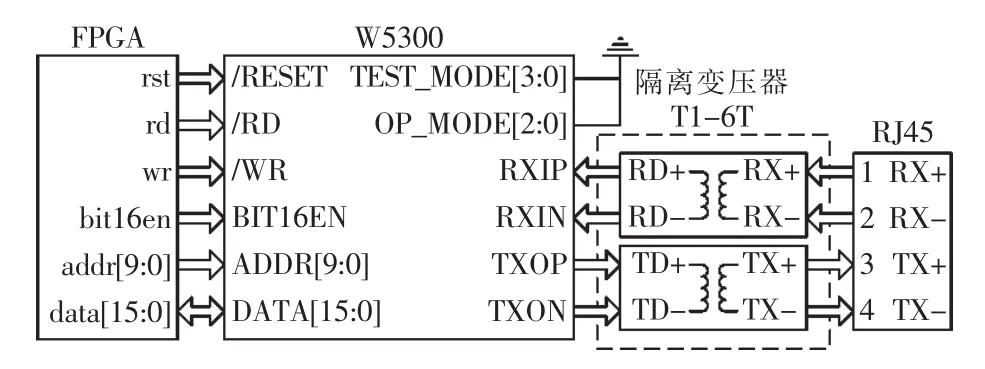

本文设计的接口主要是通过FPGA设置BIT16EN信号为高电平,实现16位数据总线工作模式,并采用直接寻址模式来实现数据的高速访问,物理层使用W5300内部的PHY,并配置为全功能自动握手运行模式,即TEST_MODE[3:0]引脚和OP_MODE[2:0]引脚均接地。在以太网的设计中,外部接口的设计不可忽视,它关系到数据传输的抗噪声能力和稳定性以及传输距离;在数据传输过程中为了增强W5300的差分信号抗干扰能力,防止不同电平通过网线传输损坏设备(在工作过程中,W5300需要3.3 V、1.8 V两种不同电平),W5300与 RJ45之间采用网络隔离变压器T1-6T连接,其支持频率高达300 MHz,既能满足高速以太网的频率要求,又能有效地保护接口电路。W5300芯片设有外置指示灯输出,当网络连接成功时,LINKLED引脚输出低电平;当有数据包发送时,发送端TXLED输出低电平,接收端RXLED输出高电平,通过观察外置指示灯,可以实时显示以太网的数据传输动态。W5300以太网接口主要硬件连接原理如图2所示。

图2 W5300以太网接口硬件连接原理图Fig.2 Connection schematic diagram of W5300 Ethernet interface hardware

2 逻辑程序设计

以太网接口逻辑程序设计部分主要通过Xilinx ISE12.1软件平台,选用硬件描述语言VHDL编写状态机程序,实现FPGA对W5300的配置及数据发送、接收控制,最终实现上位机与W5300的数据通信。

(1)W5300 配置模块

FPGA对W5300的配置模块主要包括W5300初始化、对应SOCKETn端口配置。W5300的初始化主要分为三个步骤:主机接口设置,网络信息设置和内部TX/RX存储器的分配。在本文设计中,主要通过对26个不同寄存器的配置来完成W5300初始化。为了节省FPGA逻辑资源和灵活配置这些寄存器,FPGA逻辑控制程序调用了FPGA内部的IP核,通过构建深度为64B,位宽为16位的只读单口块ROM,将需要配置的寄存器的地址和其对应的寄存器值依次写入初始化文件(.coe),并将该文件加载到BLOCK ROM中。在单口块ROM中,当读使能EN为高电平时有效,时钟源CLK上升沿时,配置的数据从ROM端口输出,写进W5300数据线和地址线,其示意图如图3所示。

图3 单口块ROMFig.3 Single port block ROM

W5300只支持软件复位,所以FPGA在上电后对W5300进行软件复位。FPGA完成对W5300软件复位之后就调用该IP核实现对W5300的初始化。本文选用SOCKET1进行数据通信,初始化完成之后 FPGA主要对 S1_MR、S1_PORT、S1_CR寄存器写入对应地址和寄存器值实现对SOCKET1的端口配置,然后打开SOCKET1,并将其设置为UDP单道通信模式。FPGA完成对W5300配置之后,读取S1_SSR寄存器值,判断其是否处于UDP模式,若是则进入数据通信;反之,将该端口关闭,返回重新对W5300配置。

(2)W5300 通信控制模块

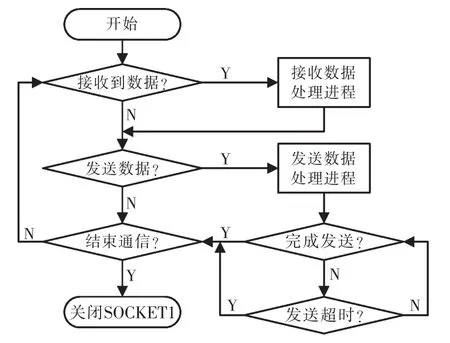

以太网接口与上位机通信包括数据接收和发送。W5300工作在UDP模式,UDP是一种报文通信协议,接收和发送数据不需要像TCP那样建立SOCKET连接,就可以达到较高的传输速度[5],其通信流程如图4所示。

图4 UDP模式通信流程图Fig.4 UDP mode communication flow

逻辑控制程序按照图4通信流程编写状态机,首先读取S1_RX_RSR寄存器,查询W5300是否接到数据,若该寄存器接收数据字节长度大于0,则表明接收到数据,进入接收数据处理进程中。该进程主要负责处理内部RX存储器中接收到的UDP数据,并将其读取到FPGA中,数据全部读取完后,执行RECV命令,即完成数据接收。数据接收完成之后跳转到数据发送查询,若S1_TX_FSR有足够剩余空间时,将待发送的数据通过S1_TX_FIFOR依次写入到TX存储器中,并将发送数据字节数写入到S1_TX_WRSR寄存器,然后运行SEND命令发送数据,判断并清除发送完成、超时中断,即完成数据发送。最后判断是否结束通信任务,若结束任务,则将S1_CR寄存器设置为 “0x10”,W5300状态变为SOCK_CLOSED,关闭SOCKET1端口;反之,返回开始查询。

在通信过程中,程序的主要负责对W5300寄存器的读写控制、UDP传输协议的实现。当实时传输数据量较大时,对时序要求就非常严格,若时序不正常,将会导致数据的错误或丢失。为了满足时序要求,本设计中FPGA程序利用控制状态机数量来产生读写时序,硬件设计中FPGA选用40 MHz基准时钟,并将W5300使能信号CS直接接地,一直保持有效状态,每写一次就控制/WR信号保持4个周期低电平,即100 ns,该时间大于芯片W5300写时序最低要求50 ns;读信号控制要求低电平有效时间大于65 ns,状态机控制程序和写信号一样。

图5 发送数据图Fig.5 Sending data

图6 读取数据Fig.6 Reading data

3 实验验证

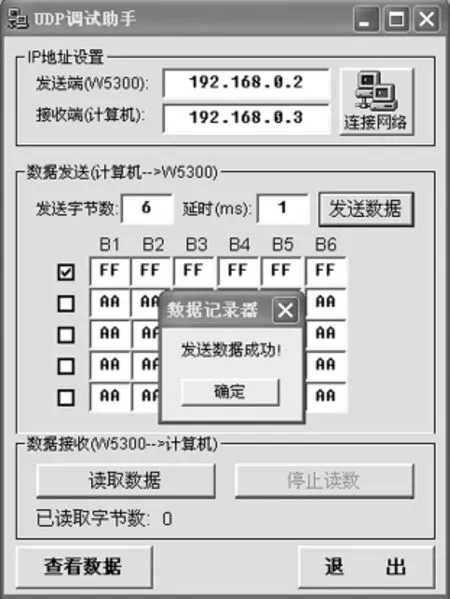

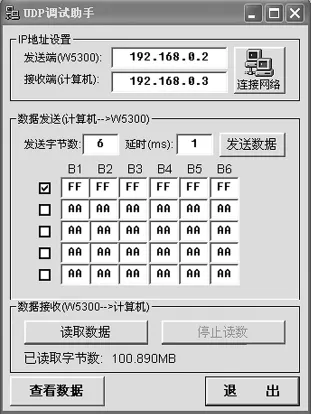

本文上位机使用UDP调试助手软件,实现对FPGA控制的W5300以太网接口通信测试。该软件采用VB编程,能够实时显示数据传输动态,易于可视化界面操作。如图5、6所示,测试软件设置W5300(发送端)的 IP 地址为:192.168.0.2,PC 机(接收端)的IP地址为192.168.0.3,连接网络成功之后,就可以点击“发送数据”或“读取数据”发送命令给W5300,并通过W5300外置网络LED指示灯亮灭情况判断以太网连接、数据传输情况,进而实时观察上位机与FPGA通信动态。

上位机UDP调试助手通过W5300以太网接口向FPGA下发“发送数据”命令,并设置发送字节数和延时时间,将6个字节的固定数“FF”下发给FPGA,如图5所示;上位机发送“读取数据”命令时,FPGA首先判断接收到的数据是否为固定数“FF”,若接收到上位机发送的数据为固定数“FF”,则通过程序设置W5300,循环将32个字节的递增数通过W5300接口上传给上位机,如图6所示。上位机软件查看数据,导出FPGA通过W5300接口上传的数据如图7所示,分析数据,结果是循环的32个字节递增数,与FPGA程序设置的上传数据一致。通过UDP调试助手对本文设计的基于FPGA控制的W5300以太网接口进行数据传输测试,实验结果表明该接口能够可靠的实现上位机与FPGA之间的通信。

图7 上位机接收数据图Fig.7 PC receives data diagram

4 结语

本文介绍了一种基于FPGA控制的W5300以太网接口设计方案,并通过实验验证了其通信的可靠性和准确性。该接口结合了FGPA逻辑资源丰富,易于调用IP核,控制灵活的优点和W5300内部集成高速以太网控制器、TCP/IP协议栈等特性,通过简单的配置和外部线路连接实现了以太网的数据传输功能,这种方法较于以太网通信传统解决方案开发周期更短,难度更小,集成度更高,运行更稳定,该接口可以应用到以太网数据采集、检测等领域,具有很高的实用性。

[1] LAN/MAN Standards Committee.IEEE Std.802.3-2005/Cor1-2006 Part 3:Carrier Sense Multiple Access with Collision Detection (CSMA/CD)Access Method and Physical Layer Specifications Corrigendum 1[S],2006.

[2] 雒珊,尹岗.基于ARM的以太网通信控制器的设计[J].电子测量技术,2009,32(10):133-135.

[3] 谢希仁.计算机网络[M].北京:电子工业出版社,2008.

[4] WIZnet Device,Inc.High-performance internet connectivity solution-W5300[EB/OL].(2008).http:www.wiznet.co.kr.

[5] 张勇,甄国涌,王丽莉,等.基于W5300的以太网数据传输硬件设计及优化[J].化工自动化及仪表,2011,38(8):2-4.