基于FPGA的数字语音通信系统设计

曾舒雅,黄 成,范 龙,张 卅

(江苏理工学院电气信息工程学院,江苏 常州 213001)

0 引言

近年来随着DSP或FPGA技术的飞速发展,嵌入式语音处理系统中也越来越多的使用了FPGA芯片。语音信号的数字化主要利用A/D、D/A转换芯片完成,还可以采用专用PCM编解码芯片实现[1-3]。本文介绍一种利用FPGA实现PCM编解码芯片接口的设计方案,针对PCM编解码芯片MC14LC5480设计FPGA接口电路,同时引入红外发射和接收电路,实现语音信号的实时无线传输。

1 系统硬件结构

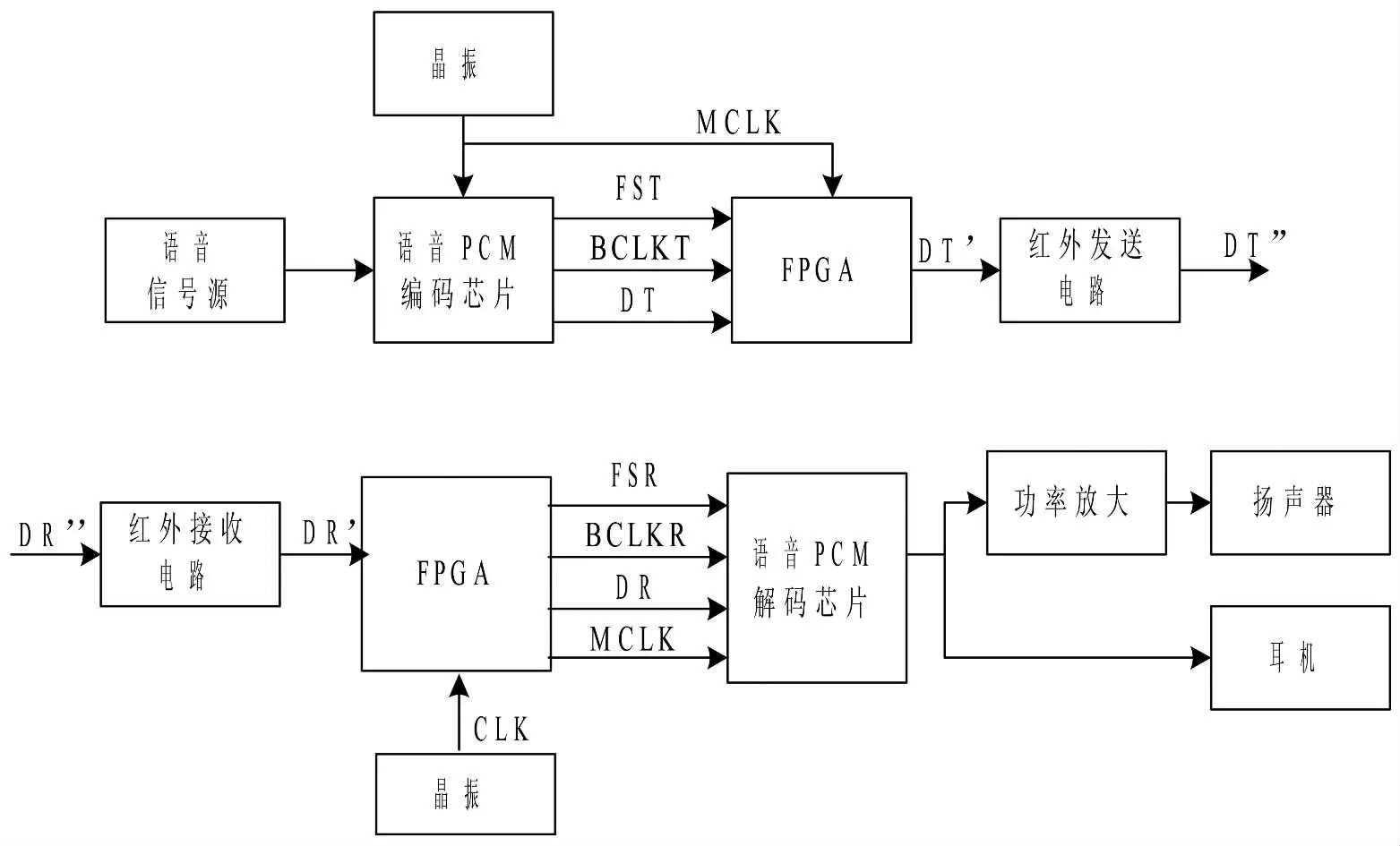

本文设计的PCM编解码芯片接口主要应用于红外无线语音传输系统。系统采用“FPGA+音频编解码芯片”的硬件结构。FPGA主要采用Altera公司的低成本CycloneII系列芯片EP2C8Q208C8;音频编解码芯片采用Motorola公司的MC14LC5480,主要用于对语音信号的A/D、D/A转换,可实现8位单声道语音信号的PCM编解码,该芯片具有低功耗、低噪声等特点,片内全差分模拟电路设计,集成发送带通滤波器和接收低通滤波器,具有RC预/后滤波器,μ/A律可选[2]①。系统硬件结构框图如图1所示。

在发送端,语音信号源提供相应的语音信号,通过语音PCM编码芯片MC14LC5480将模拟的语音信号转换为数字信号形成PCM编码格式,产生数据帧同步信号FST、位时钟信号BCLKT、语音数据信号DT,经FPGA加入同步头,最后将每一个编码信号前加同步头传输到红外线发送电路,通过发送电路将语音数据DT”发送出去。为了保证数字化传输的同步,需要在PCM编码格式中加入同步头,本文采用固定同步头的方式,即采用巴克码序列信号“01110010”。发送端采用有源晶振产生2.048MHz的主时钟信号,供给FPGA和MC14LC5480,通过FPGA产生128 kHz和8kHz位同步时钟和帧同步时钟供给MC14LC5480。

接收端通过S5821高速红外接收管接收到数据[5],送到接收端FPGA通过数字锁相环PLL恢复128 kHz的位时钟、8kHz的帧同步时钟,通过分频产生2.048MHz的主时钟信号;同时将帧同步头从数据信号中去除。然后将三路时钟及数据信号送到PCM语音编解码芯片MC14LC5480解码并转换为模拟音频信号,经耳机插孔送入耳机,另外一路接LM386功放电路驱动8欧姆扬声器。

图1 系统硬件结构框图

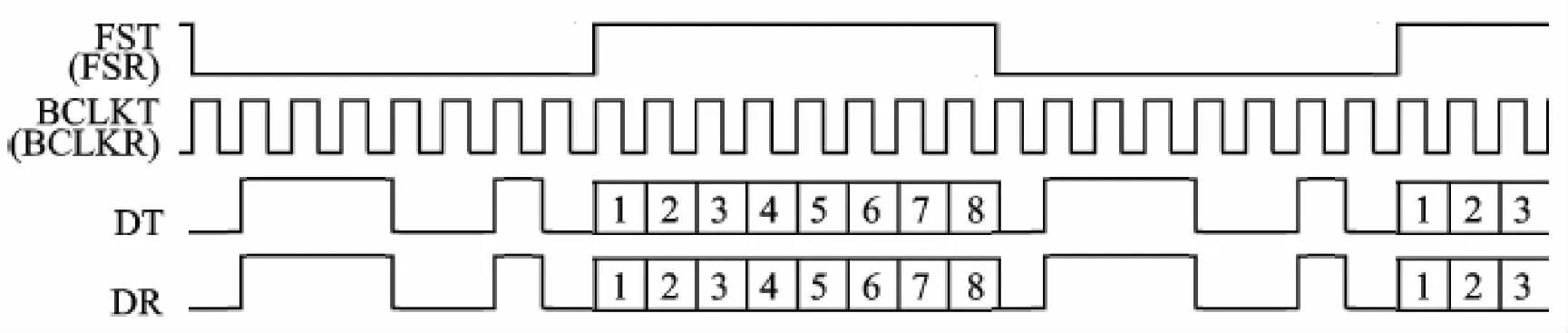

加入同步头的语音数据结构如图2所示。将MC14LC5480接成长帧模式。MC14LC5480使用采样率为8kHz,量化精度为8位时,其数据比特速率为64Kbps。图2中发/收帧同步(FST/FSR)时钟频率固定为8kHz,发/收位同步(BCLKT/BCLKR)时钟频率可选择为128kHz。由于采用单向红外传输,仅传送数据信号而不传送时钟信号。因此,在接收端需要产生帧同步时钟和位时钟,且发送端需要加入同步信号以解决数据信号自同步的问题,以保证数据的正确传输。一个周期内帧同步时钟的高电平宽度等8个位同步时钟周期,其上升沿驱动8位PCM语音数据的收/发,数据为8位;一个周期内帧同步时钟的低电平宽度等8个位同步时钟周期,对应数据帧同步头“01110010”。

图2 语音数据结构

2 软件设计

2.1 发送端软件

发送端程序的总体结构如图3所示。发送端程序流程如图4所示。发送端程序包括三个底层模块采用VHDL语言编写,分别为:CNT4——巴克码产生模块;CNT25——分频模块,用来产生帧同步信号FST和位时钟BCLKT;MUX21A——用来在语音数据信号中加入同步头数据。顶层模块采用原理图设计,程序与硬件电路的接口如下:

·PCM 码流输入端DATAIN——DT输入

·2.048MHz的时钟信号输入端MCLK——语音芯片时钟MCLK

·加同步头的PCM码流输出端PCM——DT输出

·帧同步信号输出端FST8K——FST

·位时钟输出端BCLK128K——BCLKT

图3 发送端程序的总体结构

图4 发送端程序流程

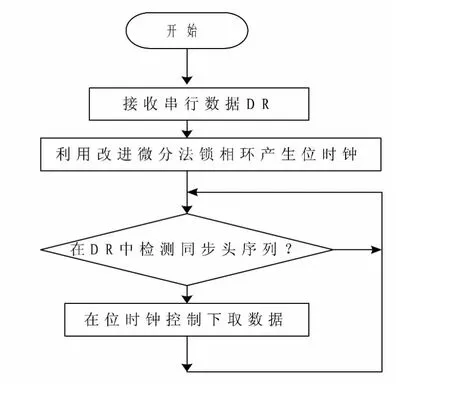

图5 接收端程序流程

2.2 接收端软件

接收端程序流程如图5所示。接收端程序的总体结构如图6所示。接收端程序包括四个底层模块采用VHDL语言编写,分别为:ZONG——位时钟锁相环,用来产生位时钟FSR;CNT25——分频模块,用来产生语音芯片时钟;JianMaQi——用来在语音数据信号中检测出同步头数据,以便后续电路去除同步头数据;ZHENGTONG——用来去除同步头数据。顶层模块采用原理图设计,程序与硬件电路的接口如下:

·50MHz的时钟信号输入端CLK——主时钟

·接收PCM码流输入端DATA——DR输入

·2.048MHz的时钟信号输出端CLK2M——语音芯片时钟输出MCLK

·PCM 码流输出端DOUT——DR输出

·帧同步信号输出端FSR——FSR输出

·位时钟输出端BCK——BCLKR

图6 接收端程序的总体结构

3 仿真波形

利用QURATUS II软件对上述程序进行波形仿真。输入MCLK时钟信号和DATAIN数据信号,由图7可看出,在FST8K低电平处对应数据为“01110010”,在高电平处对应数据为DATAIN数据,和图2语音数据结构基本一致,说明发送端程序可正常工作。

图7 发送端波形

输入CLK时钟信号和DATA数据信号,由图8可看出,在FSR低电平处对应数据为全“0”,在高电平处对应数据为DATA数据延迟一个周期,和图2语音数据结构基本一致,说明接收端程序也可正常工作。

图8 接收端波形

4 结束语

采用“FPGA+音频编解码芯片”的硬件结构设计一个数字语音通信系统,具备红外通信模块,可无线传输语音信号。使用硬件描述语言设计FPGA控制程序,采用原理图和VHDL文本相结合的编程方式,直观性好;通过软件波形仿真,功能实现后再下载到FPGA硬件上,编程速度快,并且修改方便。实验表明:该系统工作稳定,传输语音听不出失真。增加大红外发射功率或者使用光学透镜系统,可增加发射接收距离。由于红外线方式的最大优点是不受无线电干扰,这一方案可用于无线电干扰比较严重的场合实现远程无线语音通信。

注释:

①Motorola,Inc.Datasheet:MC14LC5480,1996.

[1]沈佐峰,陈曦.一种多路音频编解码系统的设计与实现[J].通信技术,2012,45(03):79-81.

[2]方子樵.用P89LPC932A1驱动PCM 语音芯片MC14LC5480[J].单片机与嵌入式系统应用,2007(11):41-43.

[3]王杰玉,杜炜,潘红兵.基于FPGA的音频编解码芯片接口设计[J].现代电子技术,2009(5):179-181.

[4]钱敏,曹云鹏,章敏,等.基于FPGA/HDL的红外遥控接收信号解码器设计[J].通信技术,2009,42(08):219-221.