An Overview of Non-Volatile Flip-Flops Based on Emerging Memory Technologies

J. M. Portal, M. Bocquet, M. Moreau, H. Aziza, D. Deleruyelle, Y. Zhang, W. Kang, J.-O. Klein, Y.-G. Zhang, C. Chappert, and W.-S. Zhao

An Overview of Non-Volatile Flip-Flops Based on Emerging Memory Technologies

(Invited paper)

J. M. Portal, M. Bocquet, M. Moreau, H. Aziza, D. Deleruyelle, Y. Zhang, W. Kang, J.-O. Klein, Y.-G. Zhang, C. Chappert, and W.-S. Zhao

—Low power consumption is a major issue in nowadays electronics systems. This trend is pushed by the development of data center related to cloud services and soon to the Internet of Things (IoT) deployment. Memories are one of the major contributors to power consumption. However, the development of emerging memory technologies paves the way to low-power design, through the partial replacement of the dynamic random access memory (DRAM) with the non-volatile stand-alone memory in servers or with the embedded or distributed emerging non-volatile memory in IoT objects. In the latter case, non-volatile flip-flops (NVFFs) seem a promising candidate to replace the retention latch. Indeed, IoT objects present long sleep time and NVFFs offer to save data in registers with zero power when the application is idle. This paper gives an overview of NVFF architecture flavors for various emerging memory technologies.

IndexTerms—Emergingmemorytechnology, ferroelectric RAM, low power, magnetic RAM, non-volatile flip-flops, phase change RAM, resistive RAM

1. Introduction

With the development of data center related to cloud services and the Internet of Things (IoT), low power consumption becomes a major issue in nowadays electronics systems. In all application domains, memories remain a major contributor to power consumption. On one hand, server nodes are based on a classical memory hierarchy going from the register and cache in high performance central processing unit (CPU), through the dynamic random access memory (DRAM) as the primary memory to the hard disk drive (HDD) for massive storage. On the other hand, IoT autonomous objects are built around the micro controller unit (MCU), where the memory hierarchy is divided in the core memory (register), memory for data (static random access memory (SRAM)), and instruction (electrically erasable programmable read-only memory (EEPROM), flash).

In this context, emerging memory solutions could open the way to new design architectures with full or partial replacement of existing memories. A clear target to bring emerging memories in the memory hierarchy is lowering the systems power. This assumption is based on [1] for emerging technologies. Indeed technologies like the phase change RAM (PCRAM), spin-transfer torque magnetic RAM (STT-MRAM), and resistive RAM (ReRAM) or ferroelectric RAM (FeRAM) present performances (programming time, voltage, and current and/or endurance and retention) that could bring significant advantages versus dynamic RAM (DRAM) or flash.

Server consumption could be lowered with the introduction of the flash as a bridge between DRAM and HDD, this trend could be even improved with the introduction of PCRAM[2]. In the same way, non-volatile (NV) flash memories embedded in MCU can be replaced by emerging memories such as FeRAM[3]or MRAM[4]for the low power purpose.

Regarding IoT autonomous objects, power consumption is a key point for their deployments. The introduction of emerging memories offers the capability to bring non-volatility memories through distributed memories in logic. This concept allows to completely power down the system, while saving the MCU state and data in the non-volatile memory point. In this context, the aim of this paper is to give an overview of the non-volatileflip-flops (NVFFs) architecture flavors based on emerging non-volatile memory technologies.

The remainder of this paper is composed as follows. Section 2 summarizes the emerging memory technologies. Section 3 introduces the classical retention flip-flop solution used to save data through power gating techniques. Section 4 is devoted to the presentation of the general architecture and operating phase of NVFF. Section 5 presents several architectures based on different technologies. Finally, Section 6 concludes the paper.

2. Emerging Memory Technologies

This section is devoted to the overview of the emerging memory technologies[5],[6]used to develop NVFF architectures.

2.1 FeRAM Technology

FeRAM is the most mature technology among the emerging memory technologies. This technology is widely used for embedded applications requiring low power since its main feature is low-voltage and low-current programming. FeRAM memory cells are based on a ferroelectric capacitor (1C) structure, which limit the scaling below the 65 nm or 45 nm node. FeRAM utilizes the positive and negative polarization directions corresponding to “1” and “0” states for stored data. The memorization mechanism is based on the hysteresis loop of the polarization versus the applied voltage. To change the state of the FeRAM capacitor, a bipolar voltage needs to be applied to switch domains from a positive remnant polarization to a negative remnant polarization. Positive and negative remnant polarizations are defined when the linear polarization is equal to 0, i.e., the applied voltage is null.

2.2 PCRAM Technology

PCRAM, also known as the PCM or PRAM technology, is used mainly for stand-alone memories and is seen as a potential candidate to be introduced in the memory hierarchy as the mass-storage memory. The memory cell is based on a capacitor like (1C) structure, where chalcogenide alloys are sandwiched between two metal electrodes. The memorization mechanism is based on the resistance change between a low resistance state (set operation) and a high resistance state (reset operation). The low resistance state corresponds to the crystal phase of the chalcogenide alloys whereas the high resistance state corresponds to the amorphous phase. The phase change is obtained by applying a high current through the cell from the bottom electrode to the top, to heat the chalcogenide alloys above the melting temperature (amorphous phase) or between the melting point and crystallization temperature (crystal phase). Thus programming is a unipolar process (set and reset operations are performed with the positive voltage pulse). Reset current reduction and temperature stability still have to be enhanced for this technology.

2.3 ReRAM Technologies

In its simplest form, the ReRAM device relies on metal/insulator/metal (MIM) structures whose conductivity can be electrically switched between high and low resistive states. Regarding the polarity of the programming voltage, a classification can be drawn with unipolar memories and bipolar memories. In unipolar oxide resistive RAM (OxRAM), reversible switching is achieved thanks to reproducible formation/dissolution of conductive filaments within the resistive oxide. A typical resistive switching based on a thermal effect shows a unipolar current-voltage characteristic. During the set operation, a partial dielectric breakdown occurs in the material and conductive filaments are formed. In contrast, they are thermally disrupted during the reset operation because of the high power density generated locally, similar to a traditional house fuse. Bipolar technologies are the conductive bridge RAM (CBRAM) and programmable metallization cells (PMC) or the bipolar OxRAM. CBRAM and PMC belong to“nanoionic” memories. MIM-like memory elements consist of an inert electrode (W, Pt, etc.), an ionic conductor used as the solid electrolyte (WO3, MoO3, GeSe, AgGeSe, etc.), and an active electrode (Ag, Cu, etc.), through an electrochemical reaction, ions (Ag+, Cu+, etc.) diffusing within the electrolyte. In bipolar OxRAM, the memory effect occurs in specific transition metal oxides (TiOx, HfOx) due to a migration of ions (oxygen ions), which are typically described by the motion of the corresponding vacancies.

2.4 MRAM Technologies

MRAM is one of the most promising technologies for the future logic and memory applications[7]. It is built in a hybrid architecture composed of basic storage elements and complementary metal-oxide-semiconductor transistor (CMOS) parts. The basic storage element of MRAM is generally referred to the magnetic tunnel junction (MTJ) nanopillar that is mainly based on the “sandwich” structure: a thin oxide barrier separated by two ferromagnetic layers. As the consequence of the tunnel magneto resistance (TMR) effect, the MTJ resistances, Rpand Rap, depend on the relative magnetization orientation of two ferromagnetic layers. With respect to the array architecture, there are two basic types: one transistor with one MTJ (1T-1MTJ) and the cross point[7],[8]. The 1T-1MTJ architecture is the most easy-understanding form where each MTJ is connected in series with an MOS transistor that operates the selecting function. However, its density potential is limited. The cross-point array architecture is able to provide prominentdensity efficiency; however, it also involves a lot of performance challenges, such as the low data access speed and sneak currents, which lead to write/read performance degradation. According to the different switching mechanisms, MRAM can be classified into diverse categories or generations, for example, field induced magnetic switching (FIMS) MRAM[9], thermally assisted switching (TAS) MRAM[10], spin transfer torque (STT) MRAM[11], and TAS-STT MRAM[12]. Among them, STT-MRAM is considered as the most promising one due to its high power efficiency and high switching speed. As it only requires a bi-directional spin polarized current, the switching process can be greatly simplified[13]. Recent material progress demonstrates perpendicular magnetic anisotropy (PMA) structures (e.g. CoFeB/MgO) allow the higher energy barrier than in-plane anisotropy, which can overcome the thermal stability issue[14],[15].

3. Retention Flip-Flop and Power Gating Technique

The mainstream of power reduction has been driven for many years by transistor downscaling and concomitant voltage reduction. A side effect of this reduction is the increase of leakage current in the sub-threshold regime with more than 40% of active mode energy dissipation due to the power leakage of idle transistors[16],[17]. To overcome this issue, solutions based on process changes have been proposed, such as the high-κ oxide associated with a metal gate[18]. Another well-known solution to save power is to power down sub-circuits of system on chip (SoC) during the idle state. However, when sub-circuits are power-down, the data saved in the flip-flops are lost and a subsequent high power budget is required for saving/restoring their content with the sub-threshold leakage current.

Numerous design solutions have been proposed to maintain flip-flop contents, such as multi-threshold voltages MOS transistors used with power gating techniques[19]. The basic principle to save the flip-flop’s content during the power-down relies on a retention circuit also known as a balloon circuit[20]. The scheme of a retention flip-flop with a balloon latch is reproduced in Fig. 1. By using this technique, the master-slave flip-flop is connected either to the virtual ground or VDDwhile a balloon latch is connected to the real ground and VDD. During the power-down, the data of the slave latch in the flip-flop is memorized in the balloon latch while the flip-flop is disconnected from the ground or VDDthanks to a switch inserted between the real and the virtual ground line. The data is restored from the balloon latch to the slave stage of the flip-flop after power up.

In conclusion, the retention flip-flop with power-gating technique is a massively deployed solution, but leakage power remains a real challenges.

Fig. 1. Architecture of a classical balloon latch used with powergating technique[20].

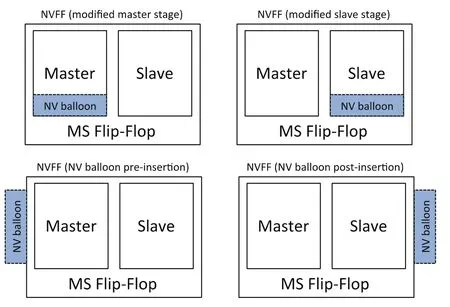

Fig. 2. NVFF are designed around four architecture flavors (modified master stage, modified slave stage, and pre/post NV balloon insertion).

4. NVFF General Architecture

In power-down applications, the flip-flop with the NV capability might be an alternative solution to power gating technique. The main idea relying on this solution is to replace the balloon latch with an NV balloon. Doing so, the virtual ground or VDDis not any longer necessary, while the flip-flop state is saved in an NV memory. During power-down, the flip-flop content is stored in the NV balloon while the real ground or VDDis disconnected (store phase). The flip-flop content is restored from the NV balloon after power up (restore phase). Thus, the use of NV balloon allows achieving zero power consumption at the flip-flop level during the idle state.

NVFF solutions are often defined for a given NV memory technology. However, some common architecture features can be summarized. As presented in Fig. 2, a classification of NVFF can be established regarding the connection of the NV balloon to the flip-flop.

Fig. 3. Schematic of NV balloon based on four elements: connection switches, writing block, sensing block, and NV block.

Fig. 4. Flip-flop architecture with an NV balloon based on FeRAM memory for energy harvesting application[21].

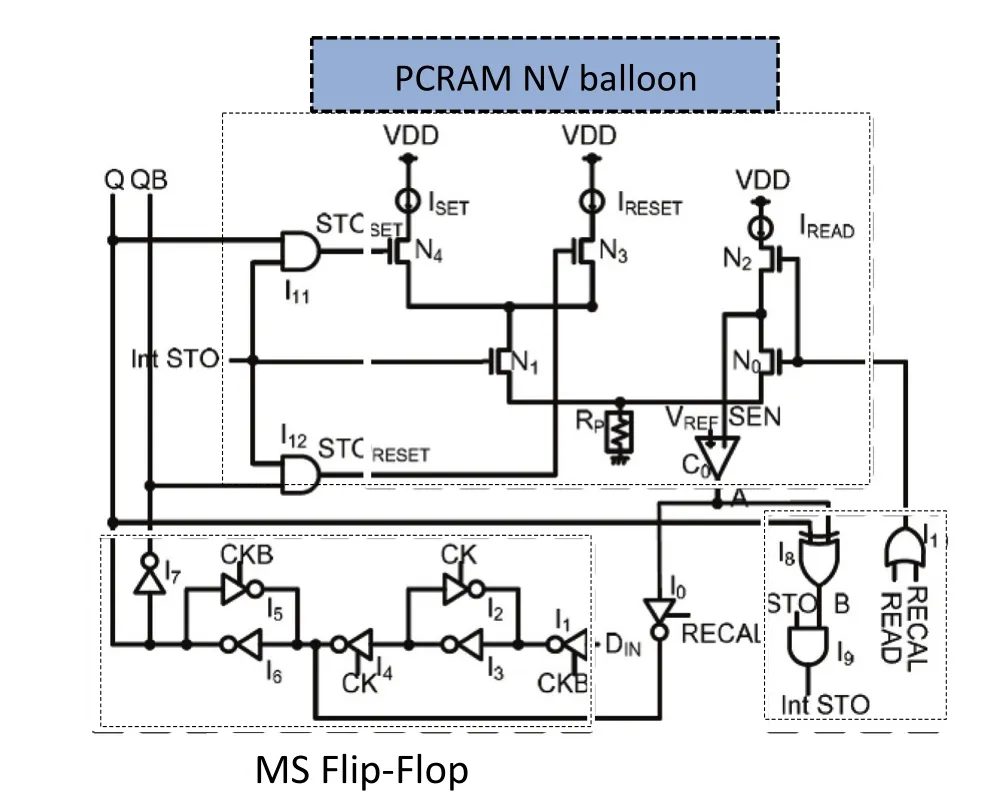

Fig. 5. Flip-flop architecture with an NV balloon based on PCRAM memory[24].

In the same way, the architecture of the NV balloon presents some common features whatever the memory technology involved. Fig. 3 presents a schematic view of the NV balloon with usually four parts: the NV block, sensing block, writing block, and connection switches. The connection switches allow to connect the NV balloon to the flip-flop during the store/restore phase and to disconnect the NV balloon during the normal operation mode. Depending on the memory technology, the writing circuit might be necessary to program or erase the NV block when the flip-flop state is stored in the NV balloon. During the restore phase, a sensing block is used to read the NV block and restore the state in the flip-flop. Finally, the NV block is built around the NV cell that keeps the state of the flip-flop during the power-down.

5. Example of Demonstrated NVFF Solutions

NVFF solutions have been demonstrated by using several architectures and memory technologies. The aim of this section is to give an example of a solution developed with each architecture flavor. Moreover, the presented examples cover also the different NV technologies, namely FeRAM, PCRAM, STT-MRAM, and ReRAM (unipolar and bipolar).

5.1 NVFF with Post-Insertion NV Balloon Based on FeRAM Technology

An NVFF has been demonstrated using a back-up module inserted post flip-flop using a FeRAM technology to store the flip-flop state[21]-[23]. The scheme of the FeRAM based NVFF is given in Fig. 4.

The FeC NV balloon is connected to the outputs Q and QBof the slave stage of the flip-flops. The connection switch is presented to isolate the NV block during the normal operation mode and to connect the two FeRAM cells during the store/restore operation. None writing block is necessary, since the FeRAM technology used in this solution is compatible with CMOS voltages. Finally, a differential voltage-sensing scheme is used assuming that the two FeRAM cells store complementary values. The voltage difference on the two FeRAM cell is amplified by the slave latch feedback loop. The proposed structure is successfully implemented in a checkpoint processor by using a 0.18 µm CMOS core process. Since the ferroelectric material lifetime remains a great challenge with the endurance about 1012cycles to 1014cycles, an additional circuit that check the FeRAM state might be added to only program FeRAM cells in case of state change. The last point is the limited shrinking capability of the FeRAM capacitor, which could limit the introduction of this solution for the CMOS node bellow 65 nm.

5.2 NVFF with Post-Insertion NV Balloon Based on PCRAM Technology

An NVFF has been demonstrated using an NV balloon inserted post flip-flop using a PCRAM technology to store the flip-flop state[24]. The scheme of this solution is illustrated in Fig. 5.

Here also, the PCRAM NV balloon is connected at the output Q and QBof the master-slave flip-flop during the store phase and to the input of the slave stage during the restore phase, through a tri-state buffer (I0). NV connection switches are designed with an AND gate connected to Q and QBand tri-state inverters connected to the master stage input. A single PCRAM cell is used in the NV block. The PCRAM cell is unipolar, so a writing scheme is necessary to apply different current levels to perform the set or reset operation on the PCRAM cell. The sensing circuit compares the voltage on the PCRAM for a given read current with a reference voltage, depending on the PCRAM resistor value, a logic ‘0’ or a logic ‘1’ is obtain on the comparator output. The proposed structure is simulated by using 180 nm, 90 nm, and 45 nm CMOS core processes respectively to study the minimal sleeping time allowed to save power versus the programming current. Indeed, the PCRAM technology needs high currents to change the resistor state through set and reset processes. In the proposed architecture, Rreset=200 kΩ is achieved with a writing current of 1250 µA and Rset=7 kΩ with a writing current of 600 µA, respectively. This large amount of writing current limit the store process to a single NV balloon at a time, this is why a circuit is added to the structure to select in which NV flip-flop the state has to be saved.

5.3 NVFF with Master-Stage NV Balloon Based on STT-MRAM Technology

An NVFF has been proposed using a modified master-stage flip-flop with a STT-MRAM technology to store the flip-flop state[25]-[27]. The scheme of this solution is illustrated in Fig. 6.

The NV balloon, based on a couple of complementary STT-MRAM cells, is introduced in the master latch of the flip-flop. By doing so, since the master latch relies completely on MTJ elements, connection switches can be avoided. Configuring a state in the MTJ elements of the master stage is controlled by an extra logic gate to set properly A and B inputs. Depending on the CLK, data in (IN), and EN signals, a current can flow in a bidirectional manner through both MTJ elements, setting one MTJ and resetting the other. The sensing operation is performed with the master-stage latch in two phases. In the first phase, CLK is equal to ‘1’ for pre-charging both MTJ nodes to the same potential. In the second phase, when CLK is equal to‘0’, potentials are discharged and the master latch switches depending on the resistance values of the right and left MTJ elements, while the logic value is captured in the slave latch. Unlike FeRAM or PCRAM solutions, STT-MRAM stores all the data during the normal mode of operations, thanks to STT-MRAM’s nearly infinite endurance, writing voltage compatibility with the CMOS process, and fast writing time.

The proposed NVFF is simulated by using a 65 nm technology node under 1.2 V, which exhibits fast writing time (100 ps) and does not impact significantly the flip-flop delay (set-up time, hold time, and propagation delay). However, the writing current remains important for this emerging technology (few hundreds µA) and the tunnel magneto-resistance (120%) remains low, making this technology prone to variability.

5.4 NVFF with Pre-Insertion NV Balloon Based on ReRAM Unipolar Technology

In [28], an NVFF has been shown by using a pre-inserted NV balloon in front of a flip-flop based on a unipolar ReRAM technology. The scheme of this solution is illustrated in Fig. 7.

The NV balloon is connected at the input of the flip-flop through a multiplexer and to the data input by a tri-state inverter. The tri-state inverter is activated during the store phase, whereas the multiplexer allows to by-pass the NV-balloon in the normal operation mode and to select the NV balloon during the restore phase. The ReRAM being unipolar, so a writing circuit is mandatory to reset the memory cell through a resistor bridge divider. The set is performed using the tri-state inverter when necessary. The ReRAM value is sensed by using the resistor bridge divider which is also used for reset. Considering that the output multiplexer may be mixed with a scan multiplexer, the area overhead introduced by the structure is one tri-states inverter and a 2T/1R branch.

Fig. 6. Flip-flop architecture with a modified master-stage to introduce NV capability based on STT-MRAM[25].

Fig. 7. Flip-flop architecture with an NV balloon based on unipolar ReRAM memory for power-down application[28].

Fig. 8. Flip-flop architecture with a modified slave stage based on bipolar ReRAM memory for power-down application[29].

The proposed NVFF is simulated on a 65 nm CMOS core process under 1.2 V. It is important to note that the set and reset voltages are compatible with CMOS voltages and the write process can be performed with currents around a few tens of µA in less than 10 ns. A remaining issue when dealing with this technology is the forming step that requires high voltages regarding set/reset voltages. Knowing that this technology is still in its infancy, the development on forming free devices could overcome this problem.

5.5 NVFF with Modified Slave Stage Based on ReRAM Bipolar Technology

An NVFF has been proposed by using a modified slave stage based on a unipolar ReRAM technology[29]-[31]. The scheme of this solution is illustrated in Fig. 8.

The NV balloon is introduced in the slave stage of the flip-flop on the foot node of both latch inverters. The NV block is composed of two ReRAM cells that store opposite states. The write circuit is designed with tri-state inverters connected to the flip-flop outputsthat are only activated during the store phase. The restore phase is performed using a differential current sensing on the both branches of the latch. Sensing is performed in two phases: one phase consists in pre-charging the internal nodes of the slave latch to VDDand during the second phase internal nodes are discharged to the ground through the resistive cells, with the slave latch performing the amplification. It is important to note that forming, programming, and reading voltages are handle with a dynamic VDD.

The proposed solution is simulated on a 180 nm CMOS core process with a 1.8 V nominal voltage. Forming and programming voltages are achieved rising VDDto 2.4 V, whereas read and normal operations can be performed under the nominal voltage of 1.8 V and can be reduced to 0.8 V or 0.4 V. Programming current compliance is set to 10 µA.

The application of this solution to the advanced CMOS process node may need: for this ReRAM technology features, some design adaptation since CMOS nominal voltage is around 1 V; for this design architecture, the improvement of the ReRAM technology to reduce the forming and programming voltages below 1.5 V.

6. Conclusions

In this paper, an overview of NVFFs based on emerging memory technologies is presented. The features of FeRAM, PCRAM, MRAM, and ReRAM memory cells are summarized. The different possible architectures of NVFFs are discussed depending on the balloon latch position and balloon latch structure. The architectural review is proposed in a context of power-down applications, where the content of the flip-flop is saved in an NV balloon before power down and is restored after power up. The use of such structure does not require any biasing during the power-off in comparison to the retention flip-flop employing a volatile balloon latch. The development of such solutions could be of the prime interest for deploying IoT.

Acknowledgment

Authors thank all participants of the project “Design and Demonstration of Digital IP Based on Emerging Non-Volatile Memories” (Agence Nationale de la Recherche funding) for fruitful discussions on the distributed emerging memory in logic concept.

[1] International technology roadmap for semiconductors. [Online]. Available: http://www.nist.gov/pml/div683/ conference/upload/Diebold_final.pdf.

[2] D. Roberts, T. Kgil, and T. Mudge, “Using non-volatile memory to save energy in servers,” in Proc. of the Conf. on Design, Automation and Test in Europe, Nice, 2009, pp. 743-748.

[3] M. Zwerg, A. Baumann, R. Kuhn, M. Arnold, R. Nerlich,M. Herzog, R. Ledwa, C. Sichert, V. Rzehak, P. Thanigai, and B. O. Eversmann, “An 82μA/MHz microcontroller with embedded FeRAM for energy-harvesting applications,” in Digest. of Solid-State Circuits Conf. Technical Papers, San Francisco, 2011, pp. 334-336.

[4] M. Natsui, D. Suzuki, N. Sakimura, R. Nebashi, Y. Tsuji, A. Morioka, T. Sugibayashi, S. Miura, H. Honjo, K. Kinoshita, S. Ikeda, T. Endoh, H. Ohno, and T. Hanyu, “Nonvolatile logic-in-memory array processor in 90 nm MTJ/MOS achieving 75% leakage reduction using cycle-based power gating,” in Digest. of Solid-State Circuits Conf. Technical Papers, San Francisco, 2013, pp. 194-195.

[5] Y. Fujisaki, “Review of emerging new solid-state non-volatile memories,” Japanese Journal of Applied Physics, doi: 10.7567/JJAP.52.040001.

[6] C. Mullerr, D. Deleruyyelle, and O.Ginez, “Emeerging memoryconcepts,”in DesignTechnologyfor Heterogeneeous Embeddded Systems,G. Nicolescuu, I. O’Connor,C. Piguet, Edd. Dordrecht:Springer, 20122, pp. 339-364.

[7] C. Chappeert, A. Fert, andd F. Dau, “Thee emergence off spin electronicss in data storage,” Naturre Materials,doi: 10.1038/nmmat2024.

[8] W.-S. Zhaoo, S. Chaudhuri, C. Accoto, J.Klein, C. Chapppert, and P. Maazoyer, “Cross-point architectuure for spin traansfer torque maggnetic randomaccess memorry,” IEEE Tranns. on Nanotech.,, 2012, vol. 11,no. 5, pp. 907--917.

[9] S. Wolf, DD. D. Awschalomm, R. A. Buhrmman, J. M. Daugghton, S. von Moolnár, M. L. Rouukes, A. Y. Chhtchelkanova, annd D. M. Treger,, “Spintronics:A spin-based eelectronics visioon for the future:Magnetism annd materials,”Science, 2001, vol. 294, no. 166, pp. 1488-14995.

[10] I. L. Prejbbeanu, M. Kerrekes, R. C. Soousa, H. Sibueet, O. Redon, B.Dieny, and J.. P. Nozières,“Thermally asssisted MRAM,”Journal off Physics: CCondensed MMatter, doi:10.1088/0953-8984/199/16/165218.

[11] Y. Huai annd P. P. Nguyenn, “Magnetic ellement utilizingg spin transfer annd an MRAM ddevice using thee magnetic elemment,”U. S. Patennt 6920063, 20005.

[12] W.-S. Zhaao, J. Duval,J. Klein, andd C. Chappertt, “A compact mmodel of magneetic tunnel juncttion (MTJ) swiitched by thermaally assisted sppin transfer toorque (TAS+STTT),”NanoscaleResearch Letteers, vol. 6, no. 11, pp. 368, 20111.

[13] J. C. Slonnczewski, “Currrent-driven exccitation of maggnetic multi-layerrs,” Journalof Magnetissm and Maggnetic Materials,vol. 159, no. 1--2, pp. L1-L7,1996.

[14] S. Ikeda, KK. Miura, H. Yaamamoto, K. MMizunuma, H. DD. Gan, M. Endo,S. Kanai, J. HHayakawa, F.Matsukura, annd H. Ohno, “Aperpendicular-anisotropy CoFFeB-MgO maggnetic tunnel juncction,” Nature MMaterials, vol.9, pp. 721-7244, Apr. 2010.

[15] Y. Zhang,W.-S. Zhao, YY. Lakys, J.-O. KKlein, J.-V. Kimm, D. Ravelosona, and C. Chhappert, “Commpact modelinng of perpendicuular-anisotropyCoFeB/MgOO magnetic ttunnel junctions,”” IEEE Trans. oon Electron Devices, vol. 59, nno. 3, pp. 819-8226, 2012.

[16] V. Kursunn and E. G.Friedman, MMulti-Voltage CCMOS Circuit Dessign, Chichesteer: Wiley, 2006.

[17] G. Sery, S. Borkar, and VV. De, “Life isCMOS: Whychase life after??” in Proc.of the IEEE//ACM Int. DDesign Automationn Conf., doi: 100.1109/DAC.20002.1012598.

[18] J. Robertsoon, “High dielectric constant ggate oxides formetal oxide Si trransistors,” Repports on Progrress in Physicss, vol. 69, no. 2, ppp. 327-396, 20006.

[19] H. Jiao andd V. Kursun, “LLow-leakage annd compact reggisters with easy-sleep mode,” JJournal of Loww Power Electroonics, vol. 6, no.2, pp. 263-2799, 2010.

[20] S. Shigemmatsu, S. Mutohh, Y. Matsuya,, Y. Tanabe, aand J. Yamada, ““A 1-V high-sppeed MTCMOSS circuit schemme for power-dowwn applicationn circuits,”IEEE Journaal of Solid-Statee Circuits, vol. 332, no. 6, pp. 8661-869, 1997.

[21] J. Wang,Y.-P. Liu, HH.-Z. Yang, aand H. Wangg, “A compare-annd-write ferrooelectric nonvoolatile flip-flopp for energy-harvessting applicatioons,” in Proc.of Int. Conf.on Green Circuitts and Systems,Shanghai, 2010, pp. 646-650.

[22]M. Ueda,“A novel noon-volatile fliip-flop usinga ferroelectriccapacitor,” inProc. of the13th IEEE IInt. Symposiumon Applicatiions of Ferrroelectrics, ddoi: 10.1109/ISAFF.2002.11958933

[23]S. Masui, W.Yokozeki, M.Oura, T. Ninommiya, K. Mukaiida, Y. Takayama, and T. Terammoto, “Design annd applicationsof ferroelectric nnonvolatile SRAAM and flip-floop with unlimitted read/programcycles and sttable recall,” inn Proc. of IEEEE Custom Integgrated Circuitts Conf., doi:: 10.1109/CICCC. 2003.12494288

[24]J.-M. Choi, CC.-M. Jung, andd K.-S. Min, “PPCRAM flip-fllop circuits withh sequentialsleep-in contrrol scheme aand selective write latch,” Journaal of Semicondductor Technoloogy and Science, vvol. 13, no. 1, ppp. 58-64, 20133.

[25]W.-S. Zhao, EE. Belhaire, andd C. Chappert,“Spin-MTJ bassed non-volatileflip-flop,” inProc. of IEEEE Int. Conf.on Nanotechnoloogy, Hong Kongg, 2007, pp. 3999-402.

[26]D. Chabi, W.--S. Zhao, E. Deeng, Y. Zhang,N. B. Romdhanne, J.-O. Klein, aand C. Chappeert, “Ultra lowpower magneetic flip-flop bassed on checckpointing/powwer gating aand self-enable mmechanisms,” IIEEE Trans.on Circuits aand Systems I:Regular Papers, doi: 10..1109/TCSI.20113. 2295026

[27]Y. Lakys, W..-S. Zhao, J.-O. Klein, and C.. Chappert, “Loow power, highreliability mmagnetic flip-fllop,” Electroniics Letters, vol. 446, no. 22, pp. 11493-1494, 20110.

[28]J. M. Portal,M. Bocquet,D. Deleruyellee, and C. Mulller,“Non-volatilee flip-flop baased on unippolar reram ffor power-downapplications,”” Journal oof Low Powwer Electronics, vvol. 8, no. 1, pp. 1-10, 2012.

[29]I. Kazi, P. Meeinerzhagen, P.-E. Gaillardon,, D. Sacchetto,A. Burg, and G. De Micheli,“A ReRAM-bbased non-volattile flip-flop withh sub-VT readand CMOS vooltage-compatibble write,” in Prroc. of IEEE thhe 11th Int. NNew Circuits aand Systems Conff.., Paris, 2013, ppp. 1-4.

[30]S. Onkaraiahh, M. Reybozz, F. Clermidyy, J. Portal, MM. Bocquet, C. MMuller, H. Hraaziia, C. Angheel, and A. Amaara,“Bipolar ReeRAM basednon-volatileflip-flops ffor low-power arrchitectures,” iin Proc. of IEEEE the 10th IInt. New Circuitss and Systemss Conf., Monntreal, 2012, ppp. 417-420.

[31]W. Robinett, MM. Pickett, J. BBorghetti, Q.-F.Xia, G. S. Snidder, G. Medeiros--Ribeiro, and RR. S. Williamss, “A memristoorbased nonvolaatile latch circuuit,” Nanotechnology, vol. 21,no. 23, pp. 2352003-235203-6.

Jean-MichelPortalwas born in Francein 1972. He reeceived his MMaster and Ph..D. degrees in 19995 and 1999, rrespectively, booth from Universiity Montpellierr 2. From 1999to 2000, he waas a temporarry researcherat University Moontpellier 2 in tthe field of FPGGA design and teest. From 2000to 2008, he wwas an assistant pprofessor at thhe Universityof Provvence, Polytechh’Marseille (mmicroelectronic design and tee st)

You-Guang Zhangwas born in China in 1963. He received the M.S degree in mathematics from Peking University, Beijing, China in 1987 and the Ph.D. degree in communication and electronic systems from BUAA, China in 1990, where he is currently a professor and director. His current research interests include microelectronics and wireless communication. He has participated in several projects of NSF and 973 and published a number of papers. In particular, he recently focuses on the wireless channel capacity and network coding using the advanced mathematics. He is also an expert on system-level algorithm and architecture design for storage and computing systems.

ClaudeChappertreceived his“Docteurd’Etat” diploma in 1985 from University of Paris-Sud 11, after graduating from the “Ecole Normale Supérieure de Saint Cloud”. He is now the research director at The French National Center for Scientific Research (CNRS), with over 30 years experience in research on magnetic ultrathin films and nanostructures, and their applications on ultra high density recording. One year was spent as a visiting scientist at the IBM Almaden Research Center, San José, USA. He then started a research group on “Nanospintronics” within IEF, University of Paris-Sud 11 and CNRS. His major interests have been on perpendicular interface anisotropy materials, oscillating interlayer interaction, magnetization reversal in ultrathin films and dot arrays, ion irradiation patterning of magnetic materials, and now spin transfer induced GHz magnetization dynamics of MRAM cells and magnetic logic circuits. He has co-authored more than 250 papers, co-holds 6 patents, and was awarded in 2000 the Silver Medal of CNRS for his research achievements. After being the director of IEF in 2010, he is now the executive manager of the foundation that is in charge of the Paris-Saclay Excellence Initiative.

Wei-Sheng Zhaowas born in China in 1980. He received the Ph.D. degree in physics from the University of Paris-Sud 11, France in 2007. From 2004 to 2008, he investigated spintronic logic circuits and designed prototypes for hybrid spintronic/CMOS chips in cooperation with STMicroelectronics and French Atomic Agency (CEA). From 2009 to 2014, he led the group of spintronics integration as a tenured CNRS research scientist and his interests include the hybrid integration of nano-devices with CMOS circuits and new non-volatile memories (40 nm technology node and below) like MRAM circuits and architecture design. Since 2014, he has been a professor at Beihang University and leads spintronics research programs. Dr. Zhao has authored or co-authored more than 100 scientific papers (e.g. Nature Communications, Advanced Materials, Nanotechnology, APL, and IEEE/ACM Transactions) and he is a senior member of IEEE.

Manuscript received March 3, 2014; revised May 13, 2014. This work was supported by the ANR project DIPMEM under Grant No. ANR-12-NANO-0010-04.

J. M. Portal, M. Bocquet, M. Moreau, H. Aziza, and D. Deleruyelle are with Aix-Marseille University and Institut Matériaux Microélectronique Nanosciences de Provence, CNRS UMR7334, Marseille, France (Corresponding author e-mail: jean-michel.portal@polytech.univ-mrs.fr).

Y. Zhang, J.-O. Klein, C. Chappert, and W.-S. Zhao are with Institut d’Electronique Fondamentale, University Paris-Sud 11 and CNRS UMR8622, Orsay 91405, France.

W. Kang and Y.-G. Zhang are with Electronics and Information Engineering School, Beihang University, Beijing 100191, China.

W.-S. Zhao is also with with Electronics and Information Engineering School, Beihang University, Beijing 100191, China.

Digital Object Identifier: 10.3969/j.issn.1674-862X.2014.02.007

Journal of Electronic Science and Technology2014年2期

Journal of Electronic Science and Technology2014年2期

- Journal of Electronic Science and Technology的其它文章

- Guest Editorial TTA Special Section on Terahertz Spectroscopy

- Guest Editorial Special Section on the Energy-Efficient Technologies

- Analysis of Partial Volume Effects on Accurate Measurement of the Hippocampus Volume

- A Matrix Formulation of Discrete Chirp Fourier Transform Algorithms

- De-Duplication Complexity of Fingerprint Data in Large-Scale Applications

- Adaptive Robust Waveform Selection for Unknown Target Detection in Clutter