DVB-T中Viterbi译码器的设计及FPGA实现*

薛伟宏,宋春林,兰利宝,刘成强

(1.同济大学电子与信息工程学院,上海200092;2.中国航天科工四院红峰控制公司,湖北孝感432000)

DVB-T中Viterbi译码器的设计及FPGA实现*

薛伟宏1,宋春林1,兰利宝2,刘成强2

(1.同济大学电子与信息工程学院,上海200092;2.中国航天科工四院红峰控制公司,湖北孝感432000)

Viterbi作为一种最大似然译码算法广泛应用在数字地面视频广播中,但由于其较高算法复杂程度,对实现高速低功耗时延小且逻辑结构简单的译码器带来了挑战。首先为了实现高速的Viterbi译码器,ACSU采用全并行结构,度量值的溢出控制采用取模归一化方法,并简化比较器。其次为了实现低功耗时延小且控制逻辑简单的Viterbi译码器,SMU采用改进的前向追溯结构,只用一组单口的RAM实现译码输出。该译码器在Xilinx Virtex6上实现并验证通过,并具有较好的译码性能。

数字地面视频广播 Viterbi 全并行 前向追溯结构

0 引 言

由于地面情况的复杂性,无线信道的多径干扰现象非常明显,这直接导致了地面电视广播受多径干扰影响严重。目前能克服多径干扰的数字地面标准有ATSC,DVB-T,ISDB-T和DTMB。DVB-T中引入了OFDM处理方式,信号经过OFDM的处理后,接着采用QPSK或QAM的调制方式,最后再通过上变频发送到发射天线。这种方案,在信道编码上采用以RS为外码,卷积码为内码的级联码实现。OFDM系统的接收端内码解码模块采用应用非常广泛的Viterbi译码器,它是整个系统的核心部件,也是最复杂和耗费资源的模块。

以往关于Viterbi译码器大多都从速度、功耗方面进行研究,为追求译码速度,文献[1]针对Radix-2,Radix-4和改进的Radix-4加比选单元进行研究。文献[2]采用流水线的加比选结构。文献[3]使用寄存器交换的方式实现高速的译码器但功耗较大。以上这些研究都是为了提高译码速度但资源消耗大,功耗方面没有优势。为了使译码器拥有较低的功耗,文献[4]在幸存路径单元使用了回溯方法但用了4块存储空间,逻辑复杂。文献[5]虽然应用了前向追溯的方法但是同时又采用了Radix-4结构使译码器变得复杂。文献[6]系统的介绍了(2, 1,7)译码器各个功能模块,但未对高速和低功耗进行深入的研究。

从上述的文献可以看出,多数只针对速度或者只针对功耗进行专门的研究,因此在DVB-T系统中,针对能同时实现高速、低功耗且拥有较小时延、简单逻辑结构的(2,1,7)Viterbi译码器的研究是十分必要的。文中针对这方面进行了系统的研究,采用全并行加比选单元Radix-2结构实现高速的Viterbi译码器,同时在幸存路径管理单元采用改进的前向追溯结构,只用一组单口的RAM实现低功耗且控制逻辑简单、较小延时的Viterbi译码器。

1 DVB-T发射机系统

DVB-T标准的信道传输核心技术是OFDM调制技术,即正交频分复用技术,该技术是适用于宽带系统的多载波数字调制技术,它能克服恶劣的地面信道性能,有效的传输码流。采用OFDM调制技术的DVB-T在信道编码上采用以RS为外码,卷积码为内码的级联码实现。Viterbi译码是卷积码的一种最大似然译码算法。图1为DVB-T发射机系统功能框图。

图1 DVB-T发射机系统功能框Fig.1 DVB-T transmitter system functional block

2 Viterbi译码器的设计

Viterbi译码器结构框图如图2所示,包含3个基本单元:分支度量单元(BMU),加比选单元(ACSU),幸存路径管理单元(SMU)。

图2 Viterbi译码器结构框Fig.2 Viterbi decoder structure

2.1 分支度量单元的设计

分支度量单元的功能是根据解映射器输出的软信息计算所有可能码字的分支度量,作为加比选(ACS)单元的输入。Viterbi译码器的软判决比硬判决能得到额外的2~3 dB增益,因此文中设计的Viterbi译码器使用3比特8电平量化的软判决进行译码。

将各状态分支度量0和1量化成0和7,使得计算分支度量值变得相对简单。在本设计中,分支度量计算模块并不计算所有状态的分支度量值,而是只计算4个可能的分支度量值bm_00,bm_01, bm_10,bm_11并存储到寄存器中,以备不同状态的加比选模块选用,大大减少了计算量和FPGA的资源消耗。通过分析又可知,7-x与x按位取反相等,则可得简化后的分支度量,由于每个无符号数的最大值为7,所以最大分支度量值是14,可以用4比特的数值来表示。若接收码为xy,则分支度量如表1所示。

表1 分支度量Table 1 Branch metric

2.2 加比选单元的设计

加比选运算就是在每一时刻,把进入同一状态的各分支度量值和其相关的累积路径值相加,比较这些结果,选择其中最小的一个作为该状态的幸存路径。因此,加比选模块由加法器、比较器和选择器组成。实现方法有:全并行、串行和串并结合。全并行是需有相同状态数的ACS单元在一个时间周期内完成全部状态的路径度量值的更新。串行是在一个周期内只完成一个ACS单元更新。串并结合是介于两者之间。为了提高速度采用全并行结构。译码器中Radix-2结构是每个时钟处理一级网络图转移信息,而Radix-4结构是每个时钟处理两级网络图转移信息,如文献[7]采用Radix-4结构提高速度,但其结构较复杂,资源消耗大且随约束长度成指数增加,因此文中采用的是全并行的Radix-2加比选架构,一次可以完成(2,1,7)卷积码全部64个状态的更新。

加比选模块通过迭代累加更新路径累积值。当路径累积值超出了有限位长所能表示的最大值时,就会发生溢出错误。因此,就必须要对度量值进行归一化运算,以防止在累加过程中发生数据溢出.解决溢出问题的传统的归一化技术有以下几种:复位归一化;减最小路径累积值归一化;定点归一化;取模归一化[8]。文中归一化算法采用是取模归一化运算。

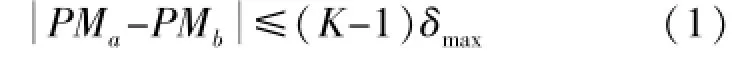

其中PMa、PMb是任意两个状态的路径累积值,K是卷积码的约束长度,δmax是分支度量值的最大值。

分支度量值的最大值为14。根据式(1)设置了任意两个路径度量之间的最大距离,其理论值为84,说明在硬件设计过程中,路径度量的最小存储宽度不能小于7比特.考虑硬件实现的复杂度和Viterbi译码性能,文中将该宽度设置为8 bit。假设

取模归一化法不需要额外溢出的硬件开销,只需把加比选模块中的比较器换成减法器并适当加大路径累积值位长即可消除溢出的影响。文中将取模归一化方法简化,比较器无需使用减法器。硬件结构如图3所示,其中D17,D27分别表示D1,D2的符号位,D16…0,D26…0则表示去掉符号位之后的数值部分。

图3 加比选单元比较器Fig.3 ACS unit comparator

2.3 幸存路径管理单元的设计

幸存路径管理单元负责在网格图中搜索最佳路径并以正常的顺序输出相应的译码数据,传统的方法主要有寄存器交换法和回溯法。寄存器交换法会产生的大量电平跳变非常不利于Viterbi译码器的低功耗设计。而回溯法基于RAM实现,能较大程度的减小功耗,但有一定延时,回溯算法包含3个主要的操作:写入、回溯和译码。要提高回溯的效率减小延时,最根本的方法就是提高回溯3个操作的并发性。可采用前向追溯结构[9],如图4所示。寄存器交换法和回溯法相结合,写入和回溯操作同时进行。文中采用改进的前向追溯结构,只用一组单口的128×128RAM来实现SMU,回溯深度是τ(64),译码延时是3τ。相比文献[10]同样使用前向追溯结构操作5个RAM,逻辑更加简单,资源利用率更高。

图4 前向追溯结构Fig.4 Trace forward architecture

下面就写入、前向追溯、译码的设计分别就图5进行介绍:例举4个时间段来说明,每个时间段又分两个小时间段,每个小时间段有τ=64个时间长度,时间轴附近列出的是每个时间段内地址正常累加的顺序,在文中为了控制方便将RAM的地址重新分配如图5的中间一列所示,RAM的写入、读出地址随时间变化,第2和第4时间段逆序。地址这种分配方式是只采用一组单口128×128RAM,数据会连续不断的写入、读出(通过对RAM中的we信号进行高低判断,使得在RAM的奇偶地址中进行轮换读写操作),同时追溯到译码的开始状态值,最终译码的结果也会连续不断的输出。

2.3.1 写入操作

在第1个时间段内奇地址1,3,5…3d,3f(正序)写入的是ACS单元输出的幸存路径判决信息,每个地址位宽为128 bit,在奇地址时刻将128 bit存入,此时刻RAM中的we信号为高。当we信号为低时,进行RAM的读操作,读的是偶地址的128 bit数据(实现了读写连续操作),128 bit数据的组合情况:当前时钟下64个幸存路径判决信息与上一时钟下64个幸存路径判决信息的组合。

在第2时间段内偶地址3e,3c…0,7e,7c…40 (以3f为分界点逆序)写入幸存路径信息。读的是奇地址的128 bit数据,其中3f,3d,3b…3,1为一组, 7f,7d,7b…43,41为一组,逆序是为了译码输出考虑。

第3,4时间段的写入与读出操作与第1,2时间段一样,以后的时间段操作以此类推。

2.3.2 前向追溯操作

前向追溯操作与写入操作是并行进行的,在写入64个数据的同时,根据幸存路径的判决信息选择最小的累积路径度量值,通过寄存器不断交换当前时刻与前一时刻的状态值,找到了译码开始的初始状态,然后直接可以从这个译码块的初始状态开始回溯并译码,译码器的吞吐率也能得到提高。文中每隔64个时钟将所有状态重新置位。

图5 改进的前向追溯结构中写入、回溯、译码的设计Fig.5 Design of writing traceback and decode in trace forwarding

2.3.3 译码输出操作

译码输出操作也是回溯译码操作。根据找到的译码初始状态值开始进行译码,具体做法是:当前的状态左移一位,后面补上幸存路径信息0或者1,得到一状态值,此时的状态值为前一时刻的状态值。每一时刻找到的状态值取最高位即为译码结果,将其存储在128 bit的输出寄存器中以便连续输出结果。在第2个时间段中的a小时间段开始存储,真正的译码输出在第2个时间段中的b小时间段开始进行。由此也可以得到译码延迟是3τ。

3 Viterbi译码器的FPGA实现

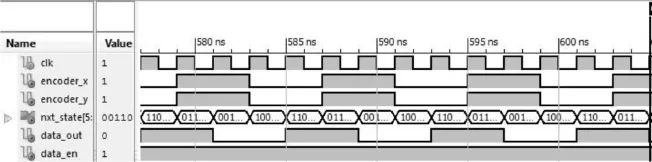

以上这些操作采用Verilog语言编写代码,仿真验证是利用ISE13.2中的ISim完成,如图6所示。并在Xilinx Virtex6 FPGA上完成了硬件验证。生成了如图7的译码器RTL框图。主时钟频率可以达到250 MHz,与文献[10-11]相比如表2所示,资源消耗大大减少。回溯深度是τ(64),译码延时只有3τ。

图6 Viterbi译码器仿真波形Fig.6 Viterbi decoder simulation waveform

图7 译码器RTL框Fig.7 RTL schematic

表2 资源消耗对比Table 2 Comparator of resources

4 结 语

文中探讨了数字地面视频广播(DVB-T)通信系统中内码Viterbi译码器的设计及FPGA实现问题。详细并且深入研究了各个模块,采用软判决8电平量化实现分支路径度量模块,加比选单元采用全并行Radix-2结构实现高速的Viterbi译码器,同时在幸存路径管理单元采用改进的前向追溯结构,只用一组单口的RAM进行译码输出,实现低功耗且控制逻辑简单、较小延时的Viterbi译码器。在Xilinx公司的FPGA上利用Verilog语言实现上述Viterbi译码器。具有较好的性能且符合DVB-T通信标准。

[1] VESTIAS M,NETO H,SARMENTO H.Design of High-Speed Viterbi Decoders on Virtex-6 FPGAs[C]//2012 15th Euromicro Conference on Digital System Design.Izmir,Turkey:IEEE Computer Society,2012:938-945.

[2] YANG Min.Design optimization of FPGA based viterbi decoder[C]//Electric Information and Control Engineering(ICEICE).Wuhan,China:IEEE Computer Society,2011:4129-4131.

[3] ABDELLATIF A A,ISMAIL S M,KORZEC D.FPGA Implementation of a Multi-Rate Punctured Viterbi Decoder Compatible with the DVB-T Standard[C]//2008 IEEE International Symposium on Signal Processing and Information Technology.Sarajevo:IEEE,2008:100-105.

[4] WANG Leou,LI Zheying.Design andImplementation of a Parallel Processing Viterbi Decoder Using FPGA[C]// Artificial Intelligence and Education(ICAIE).Hangzhou,China:[s.n.],2010:77-80.

[5] NARAYANASAMY P,GOPALAKRISHNAN S.FPGA Implementation of Less Area Overhead radix-4 Threshold Viterbi Decoder with Trace Forwarding for OFDM based Cognitive Radio[C]//2013 1st International Conference on E-merging Trends and Applications in Computer Science(ICETACS).Shillong:IEEE,2013:236-241.

[6] 郭勇,杨欢.(2,1,7)卷积码编译码器的FPGA实现[J].通信技术,2011,44(01):22-23,26. GU0 Yong,YANG Huan.Implementation of(2,1,7) Convolutional Coder/Decoder in FPGA[J].Communications Technology,2011,44(01):22-23,26.

[7] SANTHI M,LAKSHMINARAYANAN G,SUNDARAM R,et al.Synchronous pipelined two-stage radix-4 200MbpsMB-OFDM UWB Viterbi decoder on FPGA [C]//SoC Design Conference(ISOCC).Busan,Korea:IEEE Computer Society,2009:468-471.

[8] SHUNG C,SIEGEL P,UNGERBOECK G,et al.VLSI architectures for metric normalization in the Viterbi algorithm[C]//IEEE ICC'90.Atlanta,USA:IEEE, 1990:1723-1728.

[9] BLACK P J,MENG T H Y.Hybrid Survivor Path Architectures for Viterbi Decoders[C]//Proc.of ICASSP’93. Minnesota,USA:[s.n.],1993:433-436.

[10] 欧阳淦,刘亮,叶凡,等.超宽带系统中维特比译码器的设计与实现[J].计算机工程,2010,36(17): 260-263.

OUYANG Gan,LIU Liang,YE Fan,et al.Design and Implementation of Viterbi Decoder for Ultra-Wide Band System[J].Computer Engineering,2010,36(17): 260-263.

[11] 李明阳,柏鹏,屈鹏,等.基于FPGA的卷积码Viterbi译码器实现方法[J].科学技术与工程,2013,13 (18):5371-5375.

LI Ming-yang,BAI Peng,QU Peng,et al.FPGA-based Realization Scheme of a Viterbi Decoder[J].Science Technology and Engineering,2013,13(18):5371-5375.

XUE Wei-hong(1981-),female,graduate student,mainly engaged in digital communication and information processing.

宋春林(1973—),男,副教授,硕士生导师,博士,主要研究方向为移动通信、数字图像处理;

SONG Chun-lin(1973-),male,associate professor, master tutor,Ph.D.,principally working at mobile communications,digital image processing.

兰利宝(1982—),女,工程师,硕士,主要研究方向为计算机控制技术;

LAN Li-bao(1982-),female,engineer,M.Sci.,majoring in computer control technology.

刘成强(1983—),男,工程师,硕士,主要研究方向为计算机测试。

LIU Cheng-qiang(1983-),male,engineer,M.Sci.,majoring in computer test.

Design and Implementation of Viterbi Decoder for DVB-T

XUE Wei-hong1,SONG Chun-lin1,LAN Li-bao2,LIU Cheng-qiang2

(1.College of Electronics and Information Engineering,Tongji University,Shanghai 200092,China;2.Hong Feng Control Company,China Aerospace Science and Industry,Xiaogan Hubei 432000,China)

Viterbi decoding is widely used in DVB-T communication system as a kind of maximum likelihood algorithm.For its high algorithm complexity,it brings many challenges to the realization of decoder with high speed,low power-consumption,little delay and simple logic structure.Firstly,in order to implement high-speed Viterbi decoder,the structure is parallel in the ACS Unit,and the measurement of overflow control is done with modulus normalization method,and meanwhile the comparator is simplified.Secondly,in order to implement low power-consumption Viterbi decoder with simple control logic,SMU adopts the improved trace forward architecture and only a single RAM is used for decoding output.The decoder is simulated and tested on Xilinx Virtex6 FPGA development board,and has good performance.

DVB-T;Viterbi;parallel;trace forward architecture

TN919.3

A

1002-0802(2014)03-0324-06

10.3969/j.issn.1002-0802.2014.03.018

薛伟宏(1981—),女,硕士研究生,主要研究方向为数字通信及信息处理;

国家科技重大专项(No.2012ZX03001033);中央高校基本科研业务费专项资金资助(No.0800219174)

Foundation Item:National Science and Technology Major Project(No.2012ZX03001033);the Fundamental Research Funds for the Central U-niversities(No.0800219174)