新型多通道宽带接收激励器设计*

马力科

(中国西南电子技术研究所,成都 610036)

新型多通道宽带接收激励器设计*

马力科**

(中国西南电子技术研究所,成都 610036)

为满足机载综合前端宽带数据高速射频采样和激励合成的要求,以及解决传统接收激励器平台方案中接收激励与信号处理未分离和传输数据带宽不足两大问题,提出了新型多通道宽带接收激励器设计方案。该方案不仅实现了多通道500 Msample/s高速模数、数模转换,还通过对接收激励通道及高速数据接口逻辑巧妙设计实现了在接收端完美复原传输端数据流信号,实现了FPGA的4x高速吉比特传输接口与后端信号处理FPGA之间最高可达10 Gb/s的高速点对点数据通信,实现了真正意义上的多通道宽带接收激励功能,具有推广意义。

机载前端设备;宽带接收激励器;信号复原;高速接口;多通道

1 引言

中频信号采样和信号合成是数字信号处理机的模拟前端,随着系统综合化和软件无线电理论的发展,宽带高速采样和高速信号处理的要求越来越高,射频采样概念也被提及,同时,软件无线电要求软件可重构。因此,人们提出了将传感器及数字前端与信号处理在硬件上分离,前者作为接收激励器单独存在的实现方案。此外,将传感器和高速采样、发射放在一起,通过高速电信号或光信号还可实现接收激励与信号处理机的长距离通信的需求。

最早实现的接收激励功能与信号处理是作为一个模块存在于机架内[1],将模数转换器(AD)、数模转换器(DA)与含有调制解调算法的现场可编程门阵列(FPGA)采用并行数据互联。互联信号线多,传输距离短,需完成并行信号同步。接收激励功能与信号处理功能并没有分离。

文献[2]提到的传统接收激励器在收发两端都添加串行并行转换芯片,在发射端实现并行数据转化为串行LVDS数据流再进行传输,在接收端同步解串化,恢复并行数据。它的采样带宽一般在几兆赫到几十兆赫之间,数字信号处理板与接收激励器之间通过数字中频LVDS信号接口,将并行信号转换为串行LVDS数据流信号,通过高速背板进行互联,实现接收激励与数字信号处理的分离。采用串行数据流方式传输数据的优势在于:首先,远距离传输对串行信号的影响不如对并行信号的同步影响大;其次,高速数据串行传输取代低速并行传输,可以节约数据通道。但此类接收激励器只能传输几兆到几十兆采样数据,数据传输速率小于1 Gb/s。

由于传统接收激励器仍然满足不了采样数据几百兆、传输速率达10 Gb/s的要求,新型多通道接收激励器平台在传统接收激励方案的基础上进行了改进,不仅在硬件上选用采样率1 Gsample/s的高速AD、500 Msample/s的DA芯片,实现L频段直接射频采样,还抛弃传统方案中采用专用芯片串并转换的方式,直接采用FPGA的4x高速吉比特收发器GTX 通过 FPGA 程序实现 Aurora协议[3-4],与后端信号处理的FPGA实现点对点高速互联,不仅解决了传统接收激励器传感器和信号处理没有完全分离的问题,也解决了数据传输带宽不足的问题。此外,由于采样的流数据携带相位信息,在传输过程中不能损失,因此在收发端添加双口存储器进行数据缓存,通过时序匹配、两端时钟同步,实现了连续采样流数据的完美复原。

2 硬件平台设计

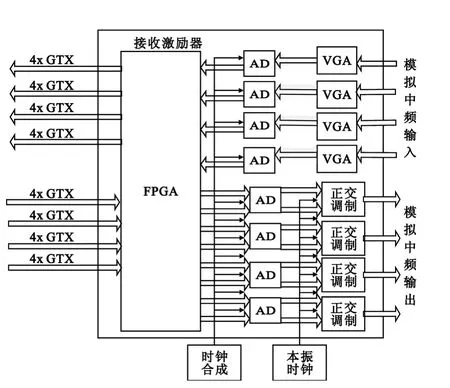

多通道宽带接收激励器平台可实现4个接收通道、4个发射通道的接收激励功能。硬件设计主要芯片包括采样率为1 Gsample/s高速AD芯片和用采样率为500 Msample/s高速DA芯片。由于多通道要求,综合考虑高速接口数量、性能和功耗的要求,选择Xilinx最新7系列的FPGA。

多通道宽带接收激励器平台电路框图如图1所示。接收通道实现1.5 GHz中频、200 MHz带宽的高速射频直接采样,采样速率500 Msample/s;发射通道实现200 MHz带宽信号产生,采样速率500 Msample/s。每一对接收激励AD、DA对应FPGA的一个4x的吉比特高速端口,构成一个接收激励通道,接收数据和激励数据在FPGA内进行全双工的传输,且互不干扰,从而实现多通道接收激励。

图1 多通道宽带接收激励器平台组成框图Fig.1 Block diagram of multi- channel wideband transceiver platform

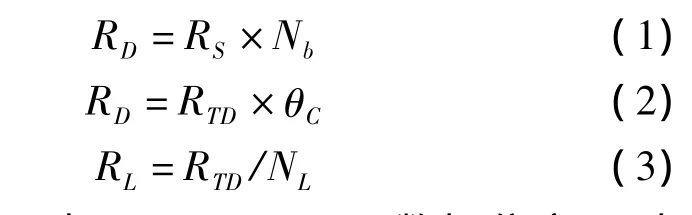

FPGA的高速吉比特端口与后端信号处理模块之间数据互联,数据速率关系由如下公式计算:

以采样率 Rs为500 Msample/s,数据位宽 Nb为16位进行计算,需要传输的数据速率RD为8 Gb/s,经过编码效率θC为80%的8b10b编码后,在高速总线上传输的数据总速率RTD达到10 Gb/s。当采用4x模式,即使用4对差分线进行传输时,每对差分线上数据速率为2.5 Gb/s。

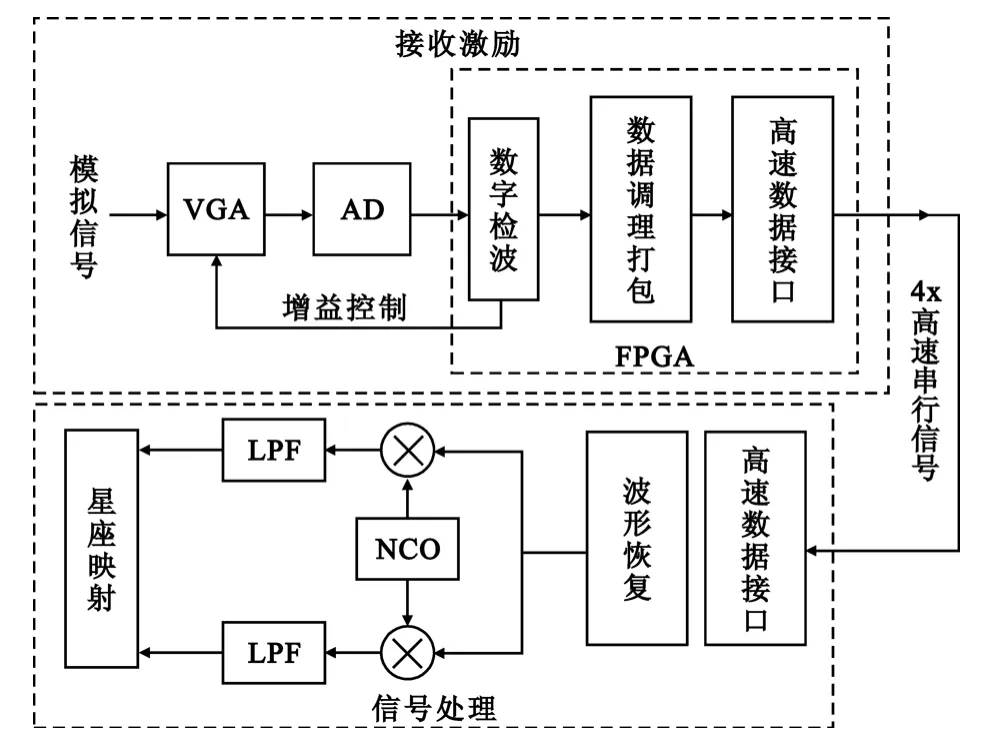

3 接收通道数据流程设计

接收激励器平台接收通道数据流程为:模拟信号进入可变增益放大器(VGA),通过AD采样变为数字信号,FPGA对信号进行检波,同时通过反向控制VGA的增益控制管脚实现环路,可认为是自动增益控制(AGC)功能。采样信号数据调理打包,送给高速吉比特数据接口,将数据发送给后端信号处理。信号处理部分通过高速接口接收数据进行波形恢复,复原采样信号,实现数据长距离无损传输,再通过正交下变频解调,星座映射得到解调码流。数据流程框图如图2所示。

图2 接收通道数据流程框图Fig.2 Flow diagram of receiver channel

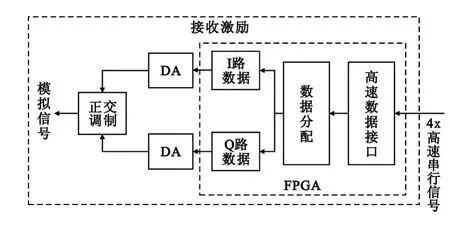

4 激励通道数据流程设计

接收激励平台激励通道信号流程为:从高速GTX接口接收需调制的数据,通过数据复原,数据分配为I、Q路调制数据,通过双路DA转换为基带信号,通过低通滤波和正交调制,产生1.5 GHz射频信号。数据流程框图如图4所示。

图3 激励通道数据流程框图Fig.3 Flow diagram of transmission channel

由于采用正交调制体制,I路和Q路具有同样的数据量,若要实现双路500 Msample/s采样率、16位宽的信号变换,需要后端高速串行信号带宽为接收通道的两倍,对背板传输信号完整性压力很大。从工程化考虑,对调制信号,适量降低采样分辨率对通信影响不明显,因此,采用将I路、Q路各使用其高8位,并成一个16位数据进行传输。这样,在传输速率保持不变的前提下,在没有牺牲太多信号质量的情况下,还能保证数字通信正常进行。

5 高速数据接口逻辑设计

高速总线的传输能力可由硬件设计保证,但宽带接收激励器设计的难点在于数据流的无损连续复原。宽带接收激励器软件逻辑代码设计的关键在于数据打包和数据复原的过程。对连续采样信号而言,它与帧信号不同,是连续的数据流,流数据携带有频率相位信息,因此数据必须是均匀且无误地传输,在发送和接收端需通过缓存,恢复为连续数据流。

FPGA的GTX的接口采用Aurora协议,它是一种适合点对点传输、轻负载的协议。由于Aurora协议简单,在链路质量不佳的情况下不会像Rapid IO之类协议一样产生大量重传,而是直接丢包,因此,一般认为Aurora协议的可靠性并不优,但从另一个角度来讲,Aurora协议可避免链路拥塞,适合流式数据传输。在链路质量有保证的前提下,Aurora协议的可靠性也是能得到保证的。

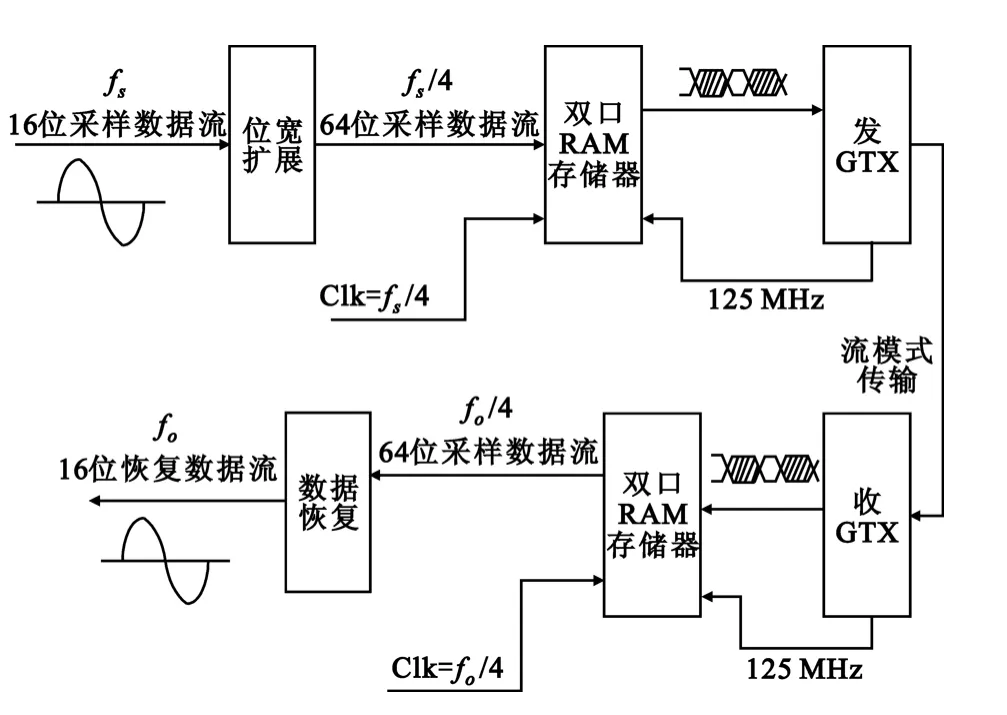

高速数据接口设计原理如图4所示,AD采样信号扩展为16位,以采样速率fs送人FPGA高速接口,为降低访问速率,采用4并1的方式,通过位宽扩展16位数据为64位数据,同时接口时钟速率降低为fs/4,数据写入双口RAM存储器,双口RAM有乒乓机制,当存储数据半满,激活GTX取数。当读完一半时停止读取,等待下一半数据写满再激活GTX取数。

图4 高速数据接口设计原理框图Fig.4 Diagram of high speed data interface design

设置GTX总线速率为4x 2.5 Gb/s,按流模式进行传输。在GTX发射端,GTX接口反向输出时钟即为125 MHz,即发GTX以125 MHz读时钟反向读取双口RAM中数据,进行发送。同时,接收端也设置双口RAM存储器,收GTX以125 MHz速率将数据写入双口RAM。接收端已知恢复采样钟速率为fo=fs,以fo/4速率64位方式读取双口RAM中数据,并通过并串转换将数据恢复成为速率fo、16位宽的连续数据流信号。

由于采样速率不恒为500 MHz,GTX的接口速率也不恒为125 MHz,GTX接口总会出现写满或读空的情况,因此,双口RAM存储器起到了平滑收发两端数据的作用。

当采样速率 fs<500 MHz,fs/4 <125 MHz,GTX读取发端双口RAM的数据需要读一段停一段,收GTX写入双口的数据也是写一段停一段,但只要fs=fo,可保证数据无损传输,且完美复原传输流信号。又当 fs=500 MHz,fs/4=125 MHz,与 GTX 读双口RAM的时钟一致,此时在总线上信号有效传输率最大,总线上传输速率达到10 Gb/s。

此外,为实现收发两端数据的连续恢复,足够深的数据缓存和两端时钟的同步是必需的。

6 实现和测试

对多通道宽带接收激励器平台的测试的主要指标包括高速总线传输能力测试、接收激励通道传输误码率指标测试以及采样数据波形恢复功能测试。

(1)高速总线传输能力指标测试

测试条件:在4×2.5 Gb/s的条件下,测试数据量大于1013,时间大于30 min,测试传输误码率。

测试方法:使用 FPGA的误码测试功能(IBERT)的IPCORE,可对FPGA底层的高速数据端口进行误码测试,此测试是物理层及链路层测试,不包含传输协议,可直接证明高速总线具备10 Gb/s的传输能力。

测试结果:4个通道传输误码率均为0。

(2)接收激励通道传输误码率指标测试

测试条件:在4x 2.5 Gb/s的条件下,测试时间大于2 h,测试传输误码率。

测试方法:在激励端发送顺序数和PN码数据进行误码比对,通过位宽扩展,双口RAM缓存,GTX发送,在接收端GTX接收数据,双口RAM缓存,到数据恢复。在数据恢复端进行比对,测试统计传输误码,可证明接收激励通道实现了高速无损传输。

测试结果:在4x 2.5 Gb/s的条件下,测试时间大于2 h,误码率均为0。

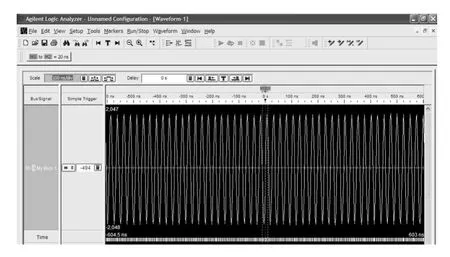

(3)采样数据波形复原功能测试

测试条件:在接收通道注入1.2 GHz射频信号,AD 分别使用100 Mb/s、300 Mb/s、500 Mb/s采样速率对中频信号进行采样,测试是否能够实现波形复原。

测试方法:FPGA将采样信号传输到后级信号处理并进行信号波形恢复,查看采样波形,将波形的16位数据线和时钟信号接入安捷伦逻辑分析仪,可看到恢复后的数据波形,可证明采样数据波形复原功能运行正常。

测试结果如图5所示,可实现连续数据流波形完美复原。

图5 复原后的采样数据波形图Fig.5 Recovery sampling wave of receiver channel

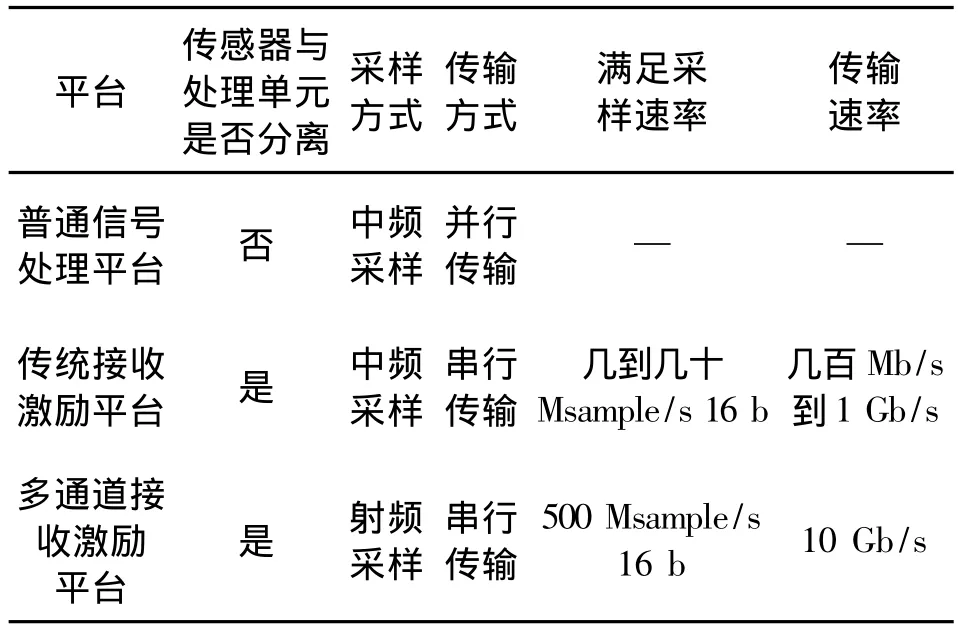

表1给出了本文多通道接收激励器平台与传统接收激励器的指标对比情况。

表1 新型多通道接收激励器平台与传统接收激励器的指标对比Table 1 Comparison between novel multi-channel transceiver and traditional transceivers

以上测试可知,多通道宽带接收激励器可满足最高达10 Gb/s的高速数据无损传输,且可完美复原采样数据流波形。

7 结束语

与传统的接收激励器相比,本文提出的新型多通道宽带接收激励器平台实现方法可解决传统方法传感器和信号处理没有完全分离的问题和传输数据带宽不足的问题,满足了当前实时宽带、射频直接采样和调制的需求。它的优点在于:

(1)具备高速AD、DA,可实现高速射频采样;

(2)通过FPGA的高速串行GTX数据接口设计实现了高速数据无损收发,经测试证明,每通道数据传输能力最高可达10 Gb/s;

(3)可实现连续采样数据流信号的完美复原。

综上所述,新型多通道宽带接收激励器平台可满足采样率上百兆、数据传输速率10 Gb/s的传输需求,在嵌入式高速宽带通信等领域具有推广意义。由于AD采样速率还在不断提高,对于采样速率大于500 MHz甚至上GHz的接收激励应用,可以将并行路数提高,如提高至8x或16x模式,进行传输,但在FPGA内部还要进行并行处理,这需要进一步研究解决。

[1]杨胜华.基于FPGA的1GHz高速采样处理平台设计[J].电讯技术,2007,47(6):163 -166.

YANG Sheng-hua.Design of a 1GHz High-speed Sampling and Processing Platform with FPGA[J].Telecommunication Engineering,2007,47(6):163 - 166.(in Chinese)

[2]杨翠虹,文丰,姚宗.基于LVDS的高速数据传输系统的设计[J].通信技术,2010,43(9):59-62.

YANG Cui- hong,WEN Feng,YAO Zong.Design of Long-distance High-speed Serial Data Transmission System based on LVDS[J].Communications Technology,2010,43(9):59 -62.(in Chinese)

[3]李维明,陈建军,陈星锜.基于Aurora协议的高速通信技术的研究[J].电子技术应用,2013,12(4):172 -175.

LI Wei- ming,CHEN Jian - jun,CHEN Xing - qi.Aurora-based Protocol High-speed Communication Technology Research[J].Application of Electronic Technique,2003,12(4):172 -175.(in Chinese)

[4]胡谨贤,张英波,黎仁刚.基于Aurora协议的光传输方案验证[J].科学技术与工程,2012,12(30):8038 -8041.

HU Jin-xian,ZHANG Ying-bo,LI Ren-gang.The Design Test of Optical Transmission Based on Aurora Protocol[J].Science Technology and Engineering,2012,12(30):8038-8041.(in Chinese)

Design of a Novel M ulti-channel W ideband Transceiver

MA Li-ke

(Southwest China Institute of Electronic Technology,Chengdu 610036,China)

To satisfy the demand of high speed wideband radio frequency sampling and signal synthesizing in airborne frontend equipment and also solve transceiver isolation with signal processing and limit of transmission bandwidth of traditional solutions,a novel multi- channel wideband transceiver solution is provided.High speed digital-to-analog converter(DAC)and analog-to-digital converter(ADC)working at 500 Msample/s are used.Perfect recovery of data signal at receiver-end is realized through receiving and simulating channel logic interface design.Inter-FPGA data communication between transceiver and signal processor is transferred at 10 Gb/s at most.The true multi- channel wideband transceiver function is realized and it will find wide applications in high speed wideband communications.

airborne frontend equipment;wideband transceiver;signal recovery;high speed interface;multi-channel

TN802;TN911

A

1001-893X(2014)05-0600-05

10.3969/j.issn.1001 -893x.2014.05.014

马力科.新型多通道宽带接收激励器设计[J].电讯技术,2014,54(5):600 -604.[MA Li-ke.Design of a Novel Multi- channel Wideband Transceiver[J].Telecommunication Engineering,2014,54(5):600 - 604.]

2013-11-28;

2014-03-07

date:2013-11-28;Revised date:2014-03-07

**

mcdona_cn@163.com Corresponding author:mcdona_cn@163.com

马力科(1982—),男,四川成都人,2007年获工学硕士学位,现为工程师,主要从事通信与信号处理处理平台及嵌入式系统开发工作。

MA Li- ke was born in Chengdu,Sichuan Province,in 1982.He received the M.S.degree in 2007.He is now an enginner.His researchconcerns communication and signal processing,embedded system development.

Email:mcdona_cn@163.com