高动态直扩信号快捕设计与FPGA实现*

何攀峰,程乃平,丁 丹,崔建华

(装备学院,北京 101416)

高动态直扩信号快捕设计与FPGA实现*

何攀峰**,程乃平,丁 丹,崔建华

(装备学院,北京 101416)

为了解决高动态直扩信号捕获速度与资源消耗的矛盾,分析了部分匹配滤波结合快速傅里叶变换(PMF-FFT)的捕获性能。针对PMF-FFT捕获范围有限且占用硬件资源过多的问题,采用递归折叠匹配滤波器代替常规匹配滤波器的方法大大节省了硬件资源,并行FFT保证了其捕获速度,同时采用扫频方法成倍增加了频偏捕获范围。给出了该方法的FPGA设计结构与实现结果,验证了该方法的有效性。与FFT循环卷积方法相比,在频偏捕获范围一定的前提下,所提方法捕获速度快,占用资源较少,非常适合高动态直扩信号的快速捕获。

高动态信号;直接序列扩频;频偏捕获;快速捕获;部分匹配滤波器;快速傅里叶变换

1 引言

直接序列扩频(DSSS)具有抗多径衰落、抗干扰能力、发射功率低、截获率低、保密性好等特点[1],目前已被广泛用于军事、移动和卫星通信。空间飞行器与卫星进行通信时,由于双方具有很高的相对径向速度和加速度(即高动态),带来大的多普勒频移及其变化率,给接收机捕获信号带来困难,同时卫星链路接收端信号信噪比较低。因此,在低信噪比、高动态环境以及对实时性要求很高的情况下,实现直扩信号的快速捕获对提高接收机性能具有重要意义。

目前国内外文献已提出很多快速捕获算法,常见的捕获方法有二维串行或并行搜索、基于傅里叶变换(FFT)循环相关捕获[1]、部分匹配滤波器(PMF)结合FFT的捕获方法(PMF-FFT)[2]等。文献[3]通过I、Q两路信号相乘消除了调制和码相位对载波频偏捕获的影响,先捕获载波后捕获伪码,捕获速度快,但信噪比门限较高。文献[1,4]通过差分处理消除载波频偏和调制对伪码相关峰的影响,先捕获伪码相位后捕获频偏,同样捕获速度快,但差分带来部分信噪比损失,检测门限较高。文献[5]基于信号滤波后重构,提出一种部分匹配滤波(PMF)结合离散余弦变换(DCT)的码捕获算法,该方法检测概率高、并且实现复杂度较小,但文章只研究了频偏较小的情况。

考虑到FFT循环相关对硬件要求较高,频率搜索慢,二维串行搜索速度太慢,并行搜索资源消耗又太多,PMF-FFT捕获法是较优的捕获方法,但占用资源仍较多。本文以码速率为9.6 Mchip/s、码长为1 023、最大多普勒频偏为30 kHz、最大多普勒频偏变化率为1.5 kHz/s的BPSK调制信号为对象,在分析PMF-FFT的基础上,提出了递归折叠部分匹配滤波结合并行FFT分析的高动态直扩信号捕获方法,实现了捕获速度与资源消耗的折衷。

2 PM F-FFT捕获方法分析

2.1 PM F-FFT捕获原理

接收的中频信号经AD采样、下变频、滤波、AGC后、抽取得到2倍码片速率信号用复数表示为

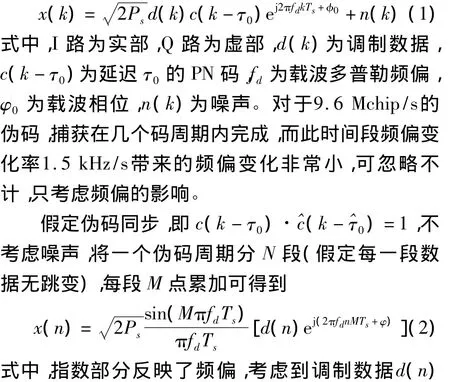

图1 PMF-FFT捕获原理框图Fig.1 The acquisition block diagram of PMF - FFT

对于一个伪码周期的接收信号,分成N段,每一段进行部分匹配滤波(其系数为对应各段的伪码),得到N点累加结果,将其进行FFT分析,直到接收信号与本地伪码对齐,FFT分析后会出现明显的谱峰,且超过预定门限值,此时表明信号捕获成功,得到多普勒频偏估计值。

2.2 PM F-FFT性能分析

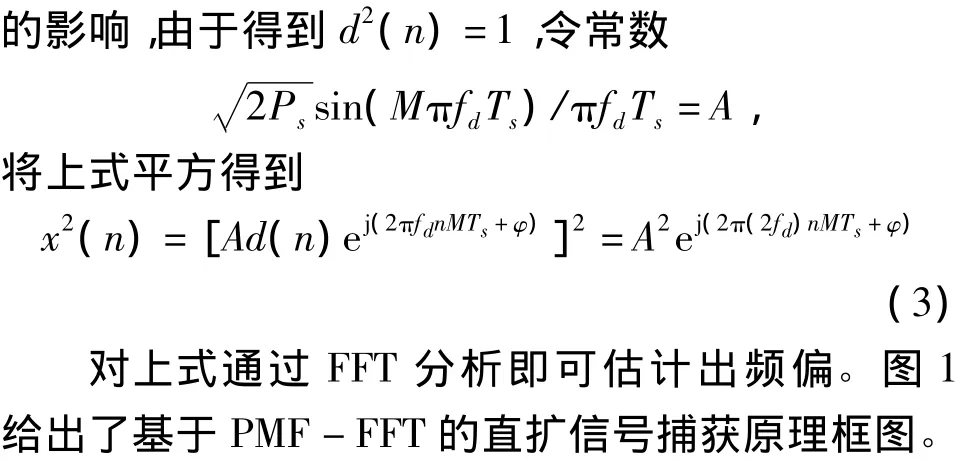

图2 不同匹配滤波长度下频偏对相关峰值的影响Fig.2 The frequency offset's impact on the correlation peak with different Matched filtering lengths

从图2中可知,在部分匹配长度一定的情况下,相关峰值随频偏的增大而减小,且部分匹配长度越长,损失越大。同时,式(4)可得到频偏分析精度Δf=fs/MN,频偏捕获范围为±fs/4M,为了捕获30 kHz频偏,要求即要求M≤80。当M太大时,不仅相关峰值受到较大损失,而且捕获范围也不能满足30 kHz的频偏;当M太小时,虽然受频偏影响减小,但本文对匹配结果的平方处理过程损失了部分信噪比,匹配长度越小,信噪比损失越大。由于上述矛盾,需要通过选择合适的匹配滤波器长度进行折衷。

(2)多普勒频偏对相关峰值的影响

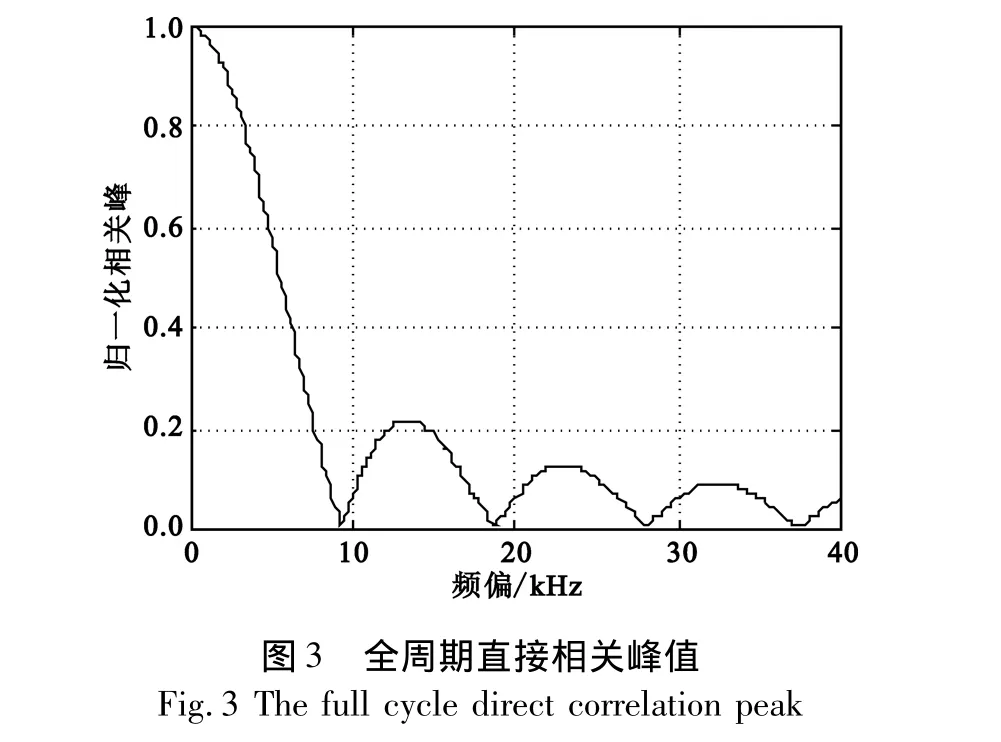

图3给出了不同频偏下直接进行全周期相关的归一化相关峰值结果。可以看出,随着频偏的增大峰值迅速下降,在频偏为30 kHz相关峰值损失超过了90%。

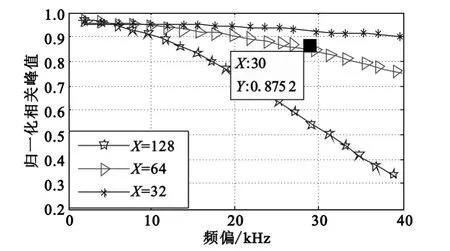

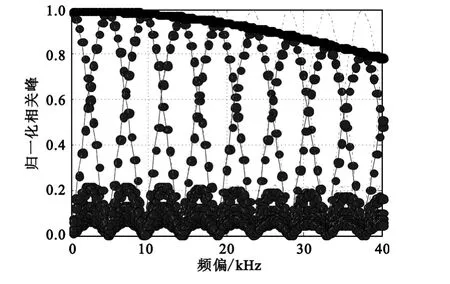

图4 PMF-FFT相关峰值Fig.4 The correlation peak of PMF - FFT

图4给出了在部分匹配滤波器长度M=64时,PMF-FFT捕获相关峰值。PMF-FFT过程可以看成对信号进行频域通道进行滤波,随着频率的增加相关峰值在缓慢较小,在频偏为30 kHz相关峰值损失不超过15%,因此,在±30 kHz范围内,采用PMF-FFT方法可以有效实现频偏捕获。

(3)仿真分析

对于长度为1 023、速率为9.6 Mchip/s的伪码,发送伪码延迟4个码片,接收端采样速率为38.4 MHz,在信噪比为[-30 dB,-5 dB],得到不同多普勒频偏下的检测概率如图5所示。从图中可以看出,在信噪比-23 dB到-18 dB范围内,随着频偏的增大检测概率有所下降,但在高于-15 dB时,基本一致。

图5 PMF-FFT的检测概率Fig.5 The detection probability of PMF - FFT

信噪比为-15 dB、频偏为30 kHz时,PMF-FFT捕获结果如图6所示。捕获频偏为28.13 kHz,伪码延迟量为16个1/4码片,均在误差分析范围内。

图6 PMF-FFT捕获结果Fig.6 The acquisition result of PMF - FFT

3 PM F-FFT的改进FPGA结构设计

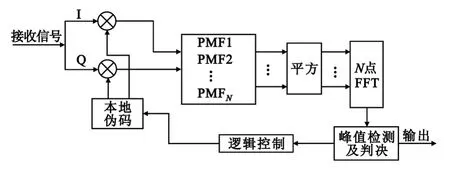

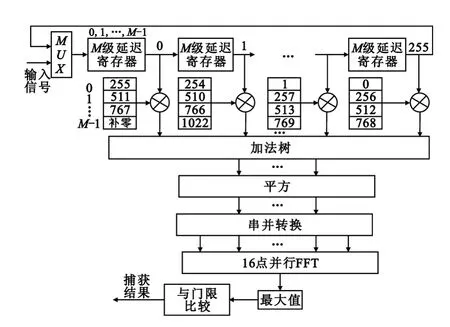

PMF-FFT方法捕获速度快,但是当伪码较长时,需占用资源较多。本文从资源复用的思想出发,设计了递归型的折叠匹配滤波器替代常规部分匹配滤波器,节省了大量FPGA资源,同时采用并行FFT实现快速捕获。图7给出改进的PMF-FFT捕获实现框图。

图7 改进的PMF-FFT实现框图Fig.7 The realization diagram of improved PMF - FFT

根据上节分析结果,选择匹配长度为64,FFT点数16,其频偏捕获范围为 ±37.5 kHz,分析精度为4.7 kHz。

3.1 递归折叠匹配滤波器设计

递归型的折叠匹配滤波器继承了折叠匹配滤波器的优点,同时该移位寄存器存储的是采样数据,而非累加结果,且可用多抽头的大Ram实现。相对于折叠匹配滤波器该方法节约了近一半多的存储资源[6]。

采用4倍折叠匹配滤波器,数据处理速率为采样信号速率(2倍码速率,19.2 MHz)的 4倍,即76.8 MHz,延迟寄存器存储为4级。数据处理流程为:第一个处理时钟将采样数据送入移位寄存器组输入端,其余3个处理时钟将从移位寄存器组末端反馈的数据送入移位寄存器组的输入端,使采样数据全部存储到移位寄存器组,数据顺序见图8。

图8 移位寄存器组中存储数据的顺序Fig.8 The sequence of data stored in register group

Ram0~Ram255通过多抽头的大Ram实现数据递归存储。其中,移位寄存器组的输出信号恰好是采样数据的逆序输出。每一个处理时钟,本地伪码与256点采样信号相乘,之后按照加法树进行求和运算完成匹配滤波。Ram255的1023数据参与累加运算,会有一个码片的增益损失,可忽略不计。

3.2 并行FFT设计

递归折叠匹配滤波器输出结果并行给出,在altera器件中FFT的IP核均为串入串出,累加结果串并转化后要求FFT处理时钟为4倍数据处理时钟,如此高的时钟导致FPGA无法处理。因此,直接进行并行16点FFT处理,不仅加快了处理速度,同时还发挥了FPGA并行处理的能力。

并行16点FFT采用基4频率抽取实现方法,只需要两级基4蝶形模块即可实现[7]。基4蝶形单元实现结构见图9。从图中可以看出,基4蝶形单元除与旋转因子相乘外,仅有一个纯虚数j需要乘法运算,因此运算量较小。16点FFT只需要两级共8个4点FFT基本单位即可实现。

图9 基4蝶形单元运算流图Fig.9 The operational flow chart of Radix -4 butterfly unit

4 捕获结果测试

测试参数为:BPSK直扩信号,码速率为9.6 Mchip/s,码长为1 023,频偏为30 kHz,频偏变化率为1.5 kHz/s。接收到70 MHz中频信号,56 MHz采样、下变频、滤波、数字AGC后,抽取得到2倍码片速率的接收信号,对信号进行捕获。

(1)捕获时间测试

本文以SignalTap II抓取的信号来测量捕获时间。2倍码片速率的采样的信号进入快速捕获模块后捕获结果如图10所示。图中q为开始捕获标志,上升沿到来时开始捕获,acq_flag为捕获脉冲,当有一个脉冲到来时表示捕获成功,得到本地伪码延迟量半个码片数和频率控制字。本次捕获频率控制字对应的频偏为32.8 kHz,与发送端30 kHz频率相比,误差在分辨率范围内,捕获时间为0.133 ms。

图10 捕获测试结果Fig.10 The acquisition test result

为了进一步测试捕获时间,多次捕获测试后,得到的捕获时间范围为[0.095 ms,0.187 ms]。

接收数据需要占用一个伪码周期,捕获过程占用一个伪码周期,因此,总共需要2个伪码周期进行捕获,即捕获时间最长需要0.208 ms。从测得的结果来看,符合理论分析。

(2)占用资源分析

为了便于比较,以载波最大多普勒频偏为150 kHz,伪码速率为10.23 Mchip/s为研究对象,采用Stratix II EP2S60F1020I4芯片进行编译。与已有文献的捕获方案相比,得到资源消耗量及捕获时间见表1。

表1 本文与已有文献的资源消耗及捕获时间对比Table 1 The comparison of resource consumption and aquisiton time between this pager and existing literatures

表1中文献[8]采用FFT循环卷积方法,文献[9]为常规的PMF-FFT捕获方法。可知,与文献[9]相比,本文方法大大减少了资源消耗量;与文献[8]相比,本文的方法资源消耗仍然较小。

对于±150 kHz的频偏,由于本文PMF-FFT的捕获范围为 ±37.5 kHz,以75 kHz为步进,每次驻留2个伪码周期即0.196 ms,5次扫描可捕获±187.5 kHz的载波频偏,扫频只需改变频率控制字,不需要额外的资源,而总的捕获为0.196 ms×5=0.96 ms。文献[9]采用 PMF-FFT方法,故捕获时间与本文相同,而方法文献[8]相比,本文方法大大提高了捕获速度。

5 结束语

为解决PMF-FFT捕获时间与资源消耗之间的矛盾,将两者折衷,本文提出部分递归折叠匹配滤波器与并行FFT结合的二维并行捕获方法,同时给出了FPGA设计结构与实现结果。仿真与测试结果表明,本文方法与FFT循环卷积相比在资源消耗量对等的前提下,大大提高了扩频信号的捕获速度,并保证了一定的捕获精度,同时利用大范围扫频扩大了频偏捕获范围。因此,无论是对连续信号还是突发信号,本文提出的方法均有较好的效果。但该方法在低信噪比下提高检测概率、提高捕获精度等方面还有待提高。

[1]罗炬锋,王翔,付耀先,等.基于FFT并行搜索伪码和频偏的快速捕获新方法[J].电子与信息学报,2011,33(3):563-568.

LUO Ju - feng,WANG Xiang,FU Yao - xian,et al.A new fast acquisition method of parallel search pseudocode and frequency offset based on FFT [J].Journal of Electronics & Information Technology,2011,33(3):563-568.(in Chinese)

[2]齐华,施小茜,冀乐,等.PMF-FFT的PN码捕获方法分析及仿真[J].西安工业大学学报,2010,33(1):57 -60.

QI Hua,SHI Xiao - qian,JI Yue,et al.The analysis and simulation of PN code acquisition method based on PMF- FFT[J].Journal of Xi'an University of Technology,2010,33(1):57 -60.(in Chinese)

[3]任江涛,夏传浩,洪一.载波与码相位分离的载波频偏估计算法[J].合肥工业大学学报(自然科学版),2010,33(9):1359 -1364.

REN Jiang - tao,XIA Chuan - hao,HONG Yi.Carrierfrequency offset estimation algorithm based on separation of carrier and code phase[J].Journal of Hefei University of Technology(Natural Science Edition),2010,33(9):1359-1364.(in Chinese)

[4]赵春燕,崔嵬.一种可克服非相干数据影响的直扩信号捕获算法[J].电子学报,2011,39(7):1491 -1496.

ZHAO Chun - yan,CUI Wei.An DSSS signal acquisition algorithm for overcoming the impact of non-coherent data modulation[J].Journal of Electronics,2011,39(7):1491-1496.(in Chinese)

[5]李小捷,许录平.DCT变换域滤波码捕获方法[J].电子学报,2013,40(10):2122 -2126.

LI Xiao-jie,XU Lu-ping.DCT transform domain filtering code acquisition method[J].Journal of Electronics,2013,40(10):2122 -2126.(in Chinese)

[6]陈鹤,邵定蓉.高动态扩频接收接收机中数字匹配滤波器的FPGA设计[J].电子设计应用,2006(5):85-87.

CHEN He,SHAO Ding - rong.High dynamic digital spread spectrum receiver matched filter receiver FPGA design[J].Electronic Design & Application,2006(5):85-87.(in Chinese)

[7]胡广书.数字信号处理理论、算法与实现[M].2版.北京:清华大学出版社,2003.

HU Guang - shu.Digital signal processing theory,algorithms and implementation[M].2nd ed.Beijing:Tsinghua University Press,2003.(in Chinese)

[8] 陈源,袁嗣杰,章兰英,等.基于 FPGA的高动态扩频信号快捕系统的设计与实现[J].遥测遥控,2008(6):49-54.

CHEN Yuan,YUAN Si- jie,ZHANG Lan - ying,et al.Design and implementation of acquisition of high dynamic DSSS signal based on FPGA[J].Journal of Telemetry,Tracking and Command,2008(6):49 -54.(in Chinese)

[9] 余湋.一种改进的 PMF-FFT短码捕获方法[J].电讯技术,2009,49(2):60 -63.

YU Wei.An improved PMF - FFT C/A code acquisition method [J].Telecommunications Engineering,2009,49(2):60-63.(in Chinese)

Fast Acquisition of High Dynam ic DSSS Signals:Design and FPGA Implementation

HE Pan - feng,CHENG Nai- ping,DING Dan,CUI Jian - hua

(Equipment Academy,Beijing 101416,China)

To solve contradictions between acquisition speed and resource consumption of high dynamic direct- sequence spread spectrum(DSSS)signals,this paper analyzes the performance of PMF - FFT(Part of the Matched Filtering combined with Fast Fourier Transform)method.For the disadvantage that this method has limited scope of frequency acquisition and high hardware resource consumption,this paper replaces conventional matched filter by recursive and folded matched filter,resulting in saving hardware resources largely.Parallel FFT is used for ensuring the speed of acquisition.Frequency sweeping to extend scope of the frequency deviation is adopoted.The structure and FPGA implementation are discussed and the result proves the effectiveness of the proposed method.Compared with the FFT circular convolution method in certain capture range offset,the proposed method has faster acquisition speed,less resource consumption,which is well- suited for fast acquisition of high dynamic DSSS signals.

high dynamic signal;DSSS;frequency offset acquisition;fast acquisition;PMF;FFT

TN911.72;TN914.42

A

1001-893X(2014)05-0547-06

10.3969/j.issn.1001 -893x.2014.05.004

何攀峰,程乃平,丁丹,等.高动态直扩信号快捕设计与FPGA 实现[J].电讯技术,2014,54(5):547 -552.[HE Pan-feng,CHENG Nai- ping,DING Dan,et al.Fast Acquisition of High Dynamic DSSS Signals:Design and FPGA Implementation[J].Telecommunication Engineering,2014,54(5):547 -552.]

2013-11-28;

2014-03-18

date:2013-11-28;Revised date:2014-03-18

**

hepanfeng01@126.com Corresponding author:hepanfeng01@126.com

何攀峰(1986—),男,陕西宝鸡人,2012年获硕士学位,现为博士研究生,主要从事空间信息处理、无线通信系统的研究;

HE Pan - feng was born in Baoji,Shaanxi Province,in 1986.He received the M.S.degree in 2012.He is currently working toward the Ph.D.degree.His research concerns spatial in-formation processing and wireless communication system.

Email:hepanfeng01@126.com

程乃平(1962—),男,陕西扶风人,1998年获博士学位,现为教授、博士生导师,主要从事软件无线电、通信系统等方面的研究;

CHENG Nai- ping was born in Fufeng,Shaanxi Province,in 1962.He received the Ph.D.degree in 1998.He is now a professor and also the Ph.D.supervisor.His research concerns software radio and communication system.

丁 丹(1980—),男,江苏南京人,2006年获硕士学位,现为讲师、博士研究生,主要从事软件无线电、通信系统等方面的研究;

DING Dan was born in Nanjing,Jiangsu Province,in 1980.He received the M.S.degree in 2006.He is now a lecturer and currently working toward the Ph.D.degree.His research concerns software radio and communication system.

崔建华(1982—),男,河北承德人,2008年获硕士学位,现为博士研究生,主要从事软件无线电、无线通信系统等方面的研究。

CUI Jian - hua was born in Nanjing,Jiangsu Province,in 1982.He received the M.S.degree in 2008.He is currently working toward the Ph.D.degree.His research concerns software radio and wireless communication system.