基于H.264的一种视频编码算法的研究与FPGA实现

刘 杰 王旭柱

(1.中国海洋大学信息科学与工程学院通信与信息系统,山东 青岛 266100;2.中国海洋大学信息科学与工程学院电子系,山东 青岛 266100)

基于H.264的一种视频编码算法的研究与FPGA实现

刘 杰1王旭柱2

(1.中国海洋大学信息科学与工程学院通信与信息系统,山东 青岛 266100;2.中国海洋大学信息科学与工程学院电子系,山东 青岛 266100)

H.264是由ITU-T视频编码专家组VCEG和ISO/IEC运动图像专家组MPEG联合制订的新一代视频编码标准。而运动估计是整个编码过程中最耗时的一部分,它的效率直接决定了整个编码系统的效率。因此本文在混合非对称十字多六边形搜索算法原理的基础上,提出了一种混合六边形搜索算法,使四种标准算法合理搭配。并且在FPGA上设计了一种有效的硬件结构实现该算法。

H.264;运动估计;混合搜索;FPGA

1 概述

通过大量H.264算法的试验,人们发现运动估计占整个编码算法全部计算量的60%~80%,因此研究一种搜索速度快、精度高, 同时便于硬件实现的运动估计搜索算法成为视频编码领域的重点和难点。块匹配算法是最常用的运动估计算法,算法简洁,便于硬件实现。通过研究已有的成熟的标准算法,我们发现运动估计不能仅仅使用某种单一的算法,需要我们根据优缺点合理组合各种标准算法,只有这样才能达到更好的编码性能。因此,本文提出了以六边形搜索为主,非对称十字搜索算法、全搜索算法和菱形搜索算法配合的一种混合搜索新算法。同时给出了一种并行流水结构在FPGA上实现该算法。

2 算法描述

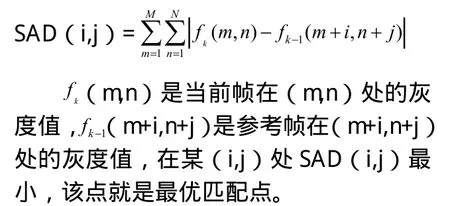

匹配误差准则采用绝对误差和:

本文设计的混合六边形搜索算法示意图如图1所示。步骤如下:

2.1 通过运动矢量预测,首先确定搜索的起始位置。要依据H.264标准的算法进行预测,然后得到一个起始搜索矢量的集合,从该集合中选出对应费用函数最小的运动矢量作为起始搜索点。

2.2 研究发现,不同方向上的运动强度是不同的,水平方向大于垂直方向,所以通过非对称的十字搜索,我们可以初步搜索一下最佳运动矢量。以搜索起点为中心,搜索范围上垂直方向是水平方向的一半,长度2 是搜索点之间的步长,这样一个非对称十字形就产生了。在此基础上,找到当前的最佳匹配点,下一步的搜索中心就是该点。

2.3 以正方形方式全搜索当前中心周围3×3的区域,找到当前的最佳匹配点,下一步的搜索中心就是该点。

2.4 对更大的区域进行搜索,采用六边形搜索,该搜索相对于DS算法速度快且准。

2.5 以搜索最佳匹配点为目的,在半径为1的范围内采用小菱形搜索,搜索到位置点后,输出该点的SAD值及其坐标。

图1 混合六边形搜索算法示意图

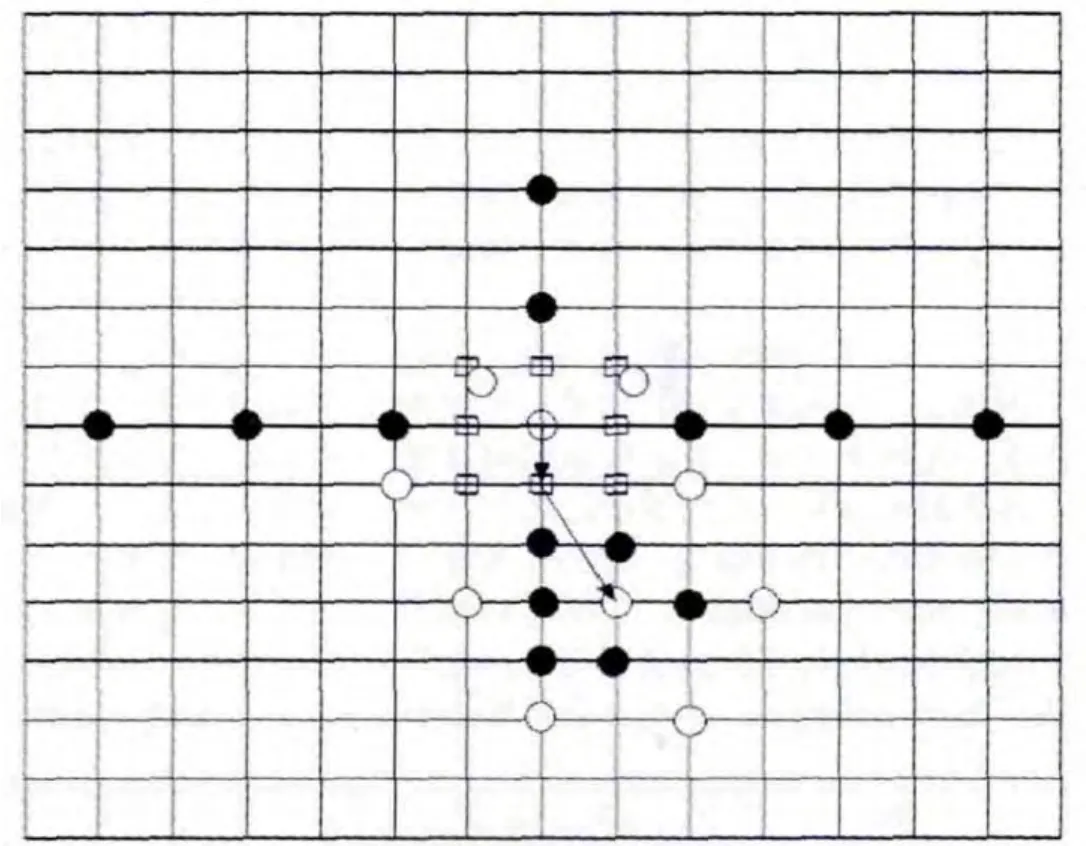

图2 运动估计硬件结构

3 硬件结构与FPGA实现

并行结构组成部分有(1)四种搜索算法实现器,主要组成部分有SAD计算器、比较器、计算器和延时器(2)两个片上RAM组(3)一个控制器,主要由地址产生器组成。本设计同时用到寄存器、片内RAM和片外SDRAM作为数据存储空间,保证数据存取量和存取速度。一个片上RAM组存当前块像素数据,另一个存参考块像素数据,这是因为片外SDRAM存取速度慢,达不到运动预测对数据的快速存取要求。一个RAM组由4个片内RAM构成,从而可以同时读取所有子区域的像素值。结构如图2所示。基于以上设计,该系统能达到高效实时的性能要求。

设计构架中的四种搜索算法分别对应其处理当前块和参考块。每种算法包含了不同个数的SAD计算器与相对应的比较器、延时器、计数器,都对应两个片内大小为16×16的RAM和大小为32×32的当前帧。32×32的当前帧由四个宏块组成,计算一个宏块内点的运动矢量绰绰有余。本设计每搜一步都会重新确定一次搜索地址,然后再搜下一步。每组片内RAM每次存储搜索数据时,都采用流水的方式进行。每完成一个算法,就把坐标点传送给地址产生器,计算出下一个点搜索所需的数据起始位置,运动估计的搜索步骤通过起到重要作用的控制器控制。

4 仿真验证

本设计中FPGA芯片选用Xilinx公司的Spartan3E系列中的XC3S500E,系统门数是50万门。采用硬件描述语言Verilog HDL编写该硬件结构,在开发软件ISE 13.4上进行综合实现与仿真验证。综合结果显示该设计占用的片内block RAM资源为1678 bytes,同时占用逻辑门数36.9k。将本文的设计与参考文献[4]中的TSS算法,文献[5]中FS的算法结构进行性能对比,如表1所示。由表可知,该设计平均需要1189个时钟周期,平均到一种搜索算法,所需要的时钟周期大约只有297个。所以,每个宏块工作时时钟周期处理速度比TSS和FS算法都要快。本设计的逻辑门资源的占有率跟其他文献相比较,保持了很低的状态。

TSS-三步搜索算法,FS-全搜索算法。

表1 本文结构与其他文献结构性能比较

结语

本文介绍了基于H.264编解码标准的一种运动估计混合搜索算法及其FPGA实现方案,该设计提高了搜索速度,保持了较高的搜索精度,同时逻辑门资源的占用率也很低,有较高的实用价值。

[1]毕厚杰.新一代视频压缩编码标准—H.264/AVC[M].北京:人民邮电出版社,2005.

[2]吴水明.基于H.264编解码的算法优化研究及FPGA的硬件实现[D].湖南:湖南大学,2007.

[3]田耘,徐文波,胡彬,等.Xilinx ISE Design Suite 10.x FPGA 开发指南-逻辑设计篇[M].北京:人民邮电出版社,2008.

[4]Sung-Tae Jung; Sang-sloe Lee.”A 4-way Pipelined Processing Architecture for Three-step Search Block-matching Motion Estimation”,IEEE Transactions on Consumer Electronics,Vol.50, No.2,pp.674-681, May 2004.

TN91

A

10.13612/j.cnki.cntp.2014.07.018