60 GHz宽带超大容量无线接入技术研究进展

张景柱,柴焱杰

(1.中国电子科技集团公司第五十四研究所,河北石家庄050081;2.中国人民解放军96275部队,河南洛阳471003)

0 引言

60 GHz毫米波通信的研究推动了面向PC、数字家电、智能便携终端等应用领域的发展,能够实现设备间数Gbps的超高速无线传输。巨大的带宽、较高的发射功率和集成电路设计的进步使得毫米波技术成为吉比特级应用的主要方案。各国和相关国际组织都加大了力度进行理论研究和产业化。目前,我国毫米波频谱标准主流为59~64 GHz和42~48 GHz两个频段。60 GHz国家标准即将出台,45 GHz国家标准发展较晚,正成为学术界新的研究热点,进入快速发展期。未来我国5G发展的主要方向之一,是着力探索毫米波频谱资源的开发利用,致力开发超传输速率达10 Gbps的室内超大容量无线通信系统。

1 60 GHz无线通信的特点

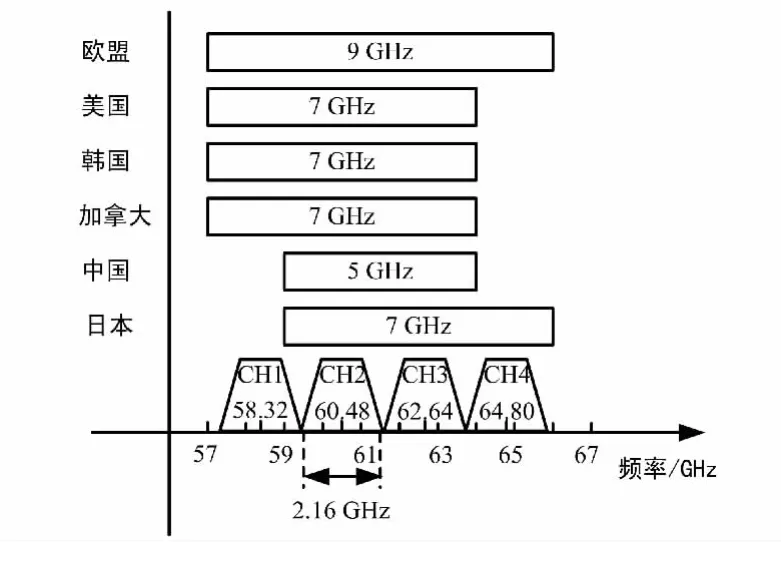

在60 GHz频段内,全球无需许可即可免费使用的带宽可达7~9 GHz(如图1所示),国际标准信道带宽为2.16 GHz。目前,无线局域网、无线个域网近距无线通信标准主要工作在2.4 GHz、5 GHz频段,而日益活跃起来的60 GHz无线通信技术由于高频信号的衰减非常严重,特别适用于短距离高速无线通信。

图1 频谱使用和信道分配图

60 GHz无线技术可用频带宽(57~64 GHz),巨大带宽意味着灵活性和潜在容量;根据山农定理,频谱带宽与信道容量是成正比的,信道容量则直接决定了通信系统所能传输的最大速率,因此使实现数Gbps的无线通信速率成为可能。60 GHz频段无线通信具有以下特点:

①处于氧气吸收极点,空间隔离度高,传输安全性好,抗干扰性强;

②可用频带宽(5~7 GHz),信道容量大,发射功率大,可实现吉比特级传输速率;

③毫米波系统成形因子小,可实现天线小尺寸和电路集成化,易实现设备小型化;

④60 GHz的天线系统能够把99.9%的能量集中在4.7°的波束范围内,再加上氧气等对信号能量的迅速衰减,使得不同链路以及系统间的相互影响很小,可实现较高频率复用;

⑤具有国际通用性和免许可性:全球大多数国家在2000年后,陆续分配了7 GHz的频带带宽用于免授权高速无线通信的研究,且各国在60 GHz附近有约5 GHz的共用频段;频谱资源完全免费,大幅度降低了使用成本。

2 60 GHz无线接入技术标准分析

目前,国际上正在制定和已经制定的60 GHz标准有3项,分别是ECMA-387、IEEE 802.15.3c以及IEEE 802.11ad。其中,ECMA-387已经成为正式的国际标准ISO/IEC 13156-2009。近年出现的60 GHz技术规范还有:WirelessHD和无线吉比特联盟(Wi-Gig)。现有支持1 Gbit/s以上数据速率的超高速无线通信的标准主要为两种[1]:IEEE 802.11ad和IEEE 802.15.3c。

国内无线个域网(CWPAN)标准工作组于2010年3月正式成立60 GHz标准项目组。由其制定的我国毫米波技术标准将于年内出台。

2.1 IEEE 802.11ad

IEEE 802.11ad形成于2009年1月,是在IEEE 802.11–2007基础上修订得来的。该标准设计了60 GHz频带高速数据传输的物理层和MAC层标准,同时规定了WLAN PBSS(Personal Basic Service Set)的工作方式。IEEE 802.11ad标准在保持IEEE 802.11标准的网络架构不变和与IEEE 802.11管理平面后向兼容性的前提下,实现了MAC服务接入点最大吞吐量为1 Gbit/s。此外,该标准定义了在2.4/5 GHz和60 GHz频带之间快速会话的转换机制,以及与其他工作在该频段系统(如 IEEE 802.15.3c和ECMA-387)的共存机制,该标准已在2012年完成。

2.2 IEEE 802.15.3c

IEEE 802.15.3c是基于IEEE 802.15.3标准修订的,批准于2009年9月,是第一个突出实现吉比特短距离无线系统的标准[2]。该标准主要用于扩展可供选择的毫米波物理层和MAC层,定义了3种物理层技术:单载波、高速接口(HSI)OFDM和音视频(AV)OFDM。采用了WPAN piconet(微微网)的工作方式[3]。还定义了基于单载波π/2相移键控(BPSK)的低数据传输速率(25 Mbit/s)公共模式信令(CMS),解决多物理层模式的共存问题。对异构天线类型,这3种物理层都支持波速赋形。波速赋形利用两级机制来寻到最优的发送和接收波速,实现高数据传输速率。

3 60 GHz无线接入技术研究进展

60 GHz无线通信系统主要包括PHY和MAC,PHY(物理层)主要定义收发信机(RF前端和基带处理后端);MAC主要涉及多址技术选择、无线资源管理、速率适配、波速控制和QoS等,目前收发信机结构的研究倾向于与现有集成电路封装技术相结合的低成本低功耗的小型单元电路或射频收发电路的实现。虽然该技术具有强大优势和广阔应用前景,但是作为一种非常复杂的集成系统,在具体实现上面临诸多挑战,比如高网络吞吐量和高功率效率的MAC设计、系统级集成封装和测试等。国内外近年来在该技术领域取得了长足的发展。

3.1 信道建模

无线通信信道中无线电波传输机制非常复杂,准确模拟出真实传播环境显得尤为重要。信道研究一直是通信系统研究的基础。当信道仿真实现后,可以很容易实现对不同传输技术和信号处理算法的性能分析,节省大量的试验测试费用。

60 GHz强衰落特性使其信号被有效限制在小范围空间内。信道模型类型取决于载频、带宽、环境类型和应用的特定系统,如何排除影响实际信道的各因素[4],建立科学准确且简单易实现的模型成为主要研究方向。目前所有60 GHz信道建模方法都是考虑天线影响的无线信道建模,建模方法主要有经验(基于测量)型建模方法、射线跟踪性建模方法和统计性建模方法(基于地理位置的统计模型和基于相关性的统计模型)[5]。

3.2 射频芯片

射频芯片对60 GHz无线通信系统的实现至关重要,其性能直接决定着无线通信系统的功能实现和性能指标。2000年以来,国际半导体设计企业和科研机构纷纷展开6 GHz硅基CMOS射频前端芯片的研究。欧美及日本显示出明显的领先优势。

(1)学术界研究进展

2002年,日本 NEC公司宣布采用0.15 μm GaAs Hetero-junction FET工艺实现了一种60 GHz的收发信机芯片,可以实现1.25 Gbps的数据传输[6]。2006年,IBM研发出基于0.13μm BiCMOS技术的60 GHz芯片组,加外部封装的尺寸也仅12 mm见方,能够实现不小于2 Gbps的信息传输速率[7]。

射频芯片研究主要分为两个阶段:早期是基于GaAs或BiCMOS工艺,采用该工艺的元器件电路性能较好,但集成度低、成本较高,器件难以商用化普及;随着半导体新工艺水平的不断提升,后期采用传统CMOS工艺加工高集成度的单片芯片。

目前学术界关于射频芯片的研究如火如荼,设计研发不断追求高性能高速率,致力于获取较大的放大器增益和输出功率,使得低功耗化设计成为一个研究方向。

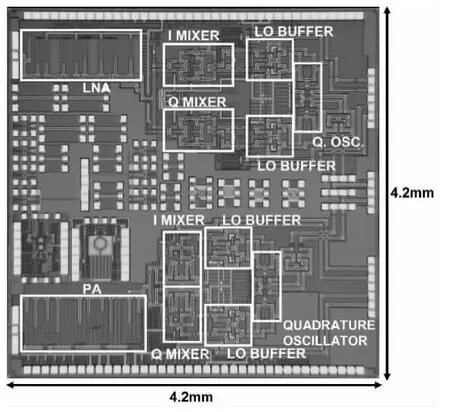

图2 60 GHz直接转换收发芯片(Tokyo Tech)

东京工业大学在ISSCC 2011年发布了16QAM直接转换收发信机[8](如 图 2 所示),采 用 65 nm CMOS工艺,配置阵列天线时最大数据速率10 Gb/s(QPSK)、16 Gb/s(16QAM);发射机功耗为181 mW,接收机为功耗138 mW。东京工业大学在该会议上还展示了60 GHz直接转换收发信机[9],支持 IEEE 802.15.3c标准的无线通信,可采用16QAM/8PSK/QPSK/BPSK调制方式,集成阵列天线的最大速率8 Gb/s(QPSK)、11 Gb/s(16QAM);发射机功耗为186 mW,接收机为功耗106 mW。

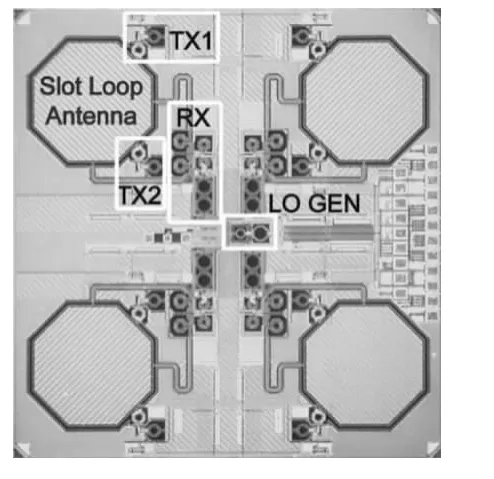

图3 60 GHz相控阵收发芯片(伯克利.2013)

2013年的国际固态电路会议上加州大学伯克利分校的科研团队展示了低功耗60 GHz接收发射相控阵[10](如图3 所示),为了降低功耗,功放和振荡器均采用0.7 V偏压,混频器采用层叠结构,接收机功耗为50 mW,发射机功耗为60 mW,天线为硅片上集成。该款芯片能够在收发芯片距离40 cm处实现10.4 Gbit/s的数据速度,能量/比特比为11 pJ/bit。

60 GHz通信系统一般采用QPSK、16QAM甚至64QAM调制方式来提高数据速率,则要求对功率放大器的线性输出功率和回退程度提出更高的要求。因此,克服高方向性和衰落的新技术成为研发的重点突破方向。

美国加州大学伯克利分校的科研团队在2011年展现了四单元相控阵接收发射系统[11](如图4所示),采用直接变频结构,基带电流分布式开关控制中频信号的相位偏移,并采用开关式功率放大器来降低功耗,锁相环所产生的信号采用Wilkiosn功分器送到四路接收发射通道,每组接收/发射通道的功耗仅为34 mW。

图4 四单元相控阵收发芯片(伯克利.2011)

IBM T J Watson研究中心在2011年的固态电路期刊上展示了0.13 μm SiGe工艺设计的16单元相控阵接收机[12],每个接收前端单元在57~64 GHz频率范围内可实现360°相位可变(精度为11.25°),并通过有源功率合成器进行功率合成。该单片系统功耗为1.8 W,最大传输速率为4.54 Gb/s(单载波)、5.25 Gb/s(OFDM)。东京工业大学在2014年的固态电路会议上发表论文,他们采用四片接收发射机单片芯片键合在一起(如图5所示),可以实现最大数据速率10.56 Gbit/s(64QAM单通道)、28.16 Gbit/s(16QAM四通道),这是目前相关文献报导里最高的数据传输速率[13]。

图5 四片键合收发芯片(ISSCC2014)

60 GHz无线通信的最终目标是研制高度集成、成本低廉、商用化的单片终端芯片。因此,高集成商用单片化,成为射频芯片组研发的终极目标。

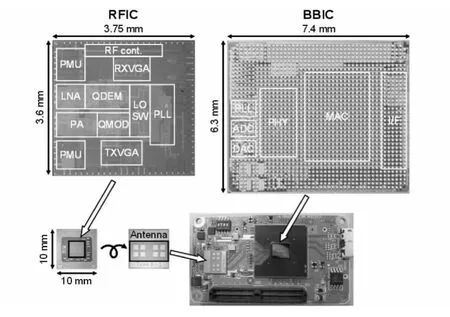

2012年固态电路期刊上公布了东芝研发的一款全集成芯片组[14](如图6所示),用于短距离/点对点无线通信。包括两个芯片,含阵列天线的射频芯片(RF IC)和基带芯片(BB IC)(含PHY/MAC层)。芯片组可实现物理层数据2.62 Gb/s和MAC层吞吐量为2.07 Gb/s,能耗为651 pJ/bit。

综上所述,妊娠糖尿病高危孕妇极容易产生巨大儿、胎膜早破、胎儿窘迫和早产等不良妊娠结局。为了防范不良妊娠结局产生,医务人员应加强对产妇各个妊娠阶段的综合管理,为其提供科学的饮食、运动干预指导,促进高危孕妇合理膳食,形成母婴安全的良好前提。

图6 全集成收发双芯片组(东芝.2012)

松下在ISSCC 2013公布了可量产的毫米波通信用芯片组[15](如图7所示),可实现超1 Gbit/s的数据传输。目标是用于智能手机等便携终端的超高速无线接口。芯片组基 WiGig/IEEE802.11ad标准,采用单载波调制,MAC控制电路嵌入基带IC。包括MAC控制电路在内的功耗在发送信号时为788 mW,接收信号时为984 mW。芯片组评测结果:可实现最大传输速率1.8 Gbit/s(传输距离40 cm)、15 Gbit/s(传输距离1 m)。

图7 全集成芯片组和评测板卡(松下.2013)

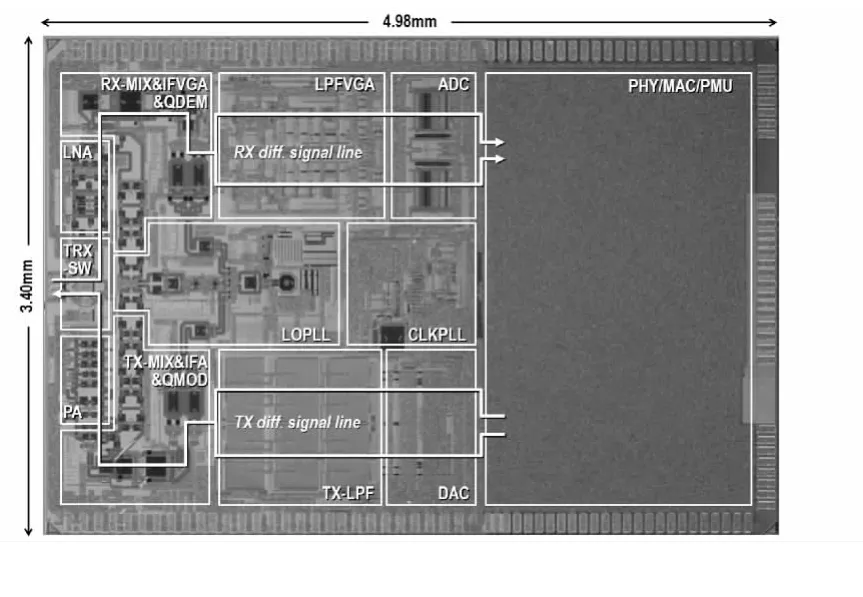

2014年国际固态电路会议中,东芝采用65 nm CMOS工艺研制了一款全集成的60 GHz收发芯片(如图8所示),芯片中不仅集成了RF/PHY/MAC和PMU的电路,包括射频收发系统、时钟频综系统、ADC/DAC电路和基带处理电路[16]。这是目前文献报导的集成度最高的60 GHz通信系统芯片。收发芯片相距4 cm时,采用QPSK调制,可实现通信吞吐量为2 Gbit/s的通信速率,总功耗为1 268 mW。

图8 最高集成度收发芯片图(东芝.2014)

(2)产业界发展现状

目前国外企业正在努力推进60 GHz超宽带通信的无线收发芯片的研发,在最近几年已经连续发布产品和系统解决方案。2010年5月,IBM和MTK(联发科)在IEEE电子射频集成电路研讨会上展示了联合开发的60 GHz收发芯片[17],芯片采用 SiGe BiCMOS工艺,可覆盖60 GHz的4个频段,多层16位带宽的阵列天线集成在标准封装中。

Atheros在Computex 2011上展示的AR9004TB芯片组是全球第一款整合802.11n和802.11ad的芯片组,传输速率(60 GHz下)为5 Gb/s。Wilocity Wi6120芯片提供60 GHz通讯功能,Atheros AR9462芯片提供2.4 GHz/5 GHz/蓝牙通讯功能。2014年1月Atheros和Wilocity推出业内第一款三频参考设计,在一个模块上同时整合802.11ac和802.11ad无线功能。美国半导体公司Hittite2012年发布的HMC6000/6001芯片组,采用SiGe BiCMOS工艺,可应用于60 GHz室外点对点连接和室内消费类设备。

2014年2月矽映电子科技公司(silicon image)发布两款大吞吐量、低功耗、单芯片CMOS波束导向型60 GHz射频收发器(SiI6340/SiI6342),将一个12信道射频收发器和所有必要的电路高度集成到单一芯片上,SiI6340将12根天线集成封装在一个芯片内,缩小了尺寸,扩大了波束导向角度。SiI6342将多条60 GHz射频信道连接到外置的12天线相控阵,此相控阵可以直接绘在印刷电路板上以实现较高的天线增益,扩大传输范围。

目前国内企业还未开发出与60 GHz宽带通信系统相关的收发芯片和解决方案。我国有多家科研院所和大学开始了毫米波技术的研究。其中,清华大学针对60 GHz接收发射系统芯片进行了设计和流片,基本可以满足60 GHz高速通信射频前端的要求。东南大学长期致力于毫米波硅基芯片的研究与开发,在毫米波单片集成电路方面,已完成60 GHz波段低噪声放大器、混频器、压控振荡器、倍频器以及分频器等设计与研制,目前正开展单片收发信机前端的研发。

3.3 集成电路技术

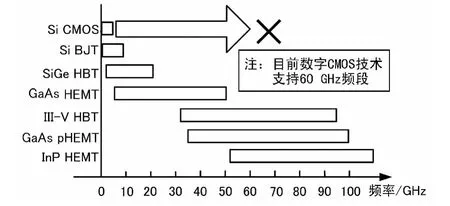

60 GHz频段上主要有3类集成工艺:① 以GaAs和InP为代表的第3代和第4代半导体技术;②以HBT和BiCMOS为代表的SiGe技术;③ 以CMOS和BJT为代表的硅片技术。上述集成工艺的工作频率如图9所示,易发现,早期的硅片技术的工作频率最低,小于10 GHz,而第3、第4代半导体技术的工作频率最高,而目前数字CMOS技术已经支持60 GHz。

图9 集成工艺的工作频率

GaAs技术能满足快速、高增益和低噪声等要求,但价格昂贵。低成本小型化是集成电路技术主要考虑的发展目标。数字CMOS技术由于其相对成本,高集成度,代价小的解决方案已经基本上取代了GaAs基工艺以及其他半导体工艺,在射频低频段中得到广泛应用。

3.4 天线技术

60 GHz毫米波信号的巨大损耗要求天线必须提供大带宽下的高增益和高效率。天线阵列波速赋形技术由于天线增益大、体积小和快速的电子可操纵性比较适用于60 GHz无线通信。目前实现阵列波速赋形技术存在很多技术难题,比如:非视距的实时阻塞问题、高损耗的馈电网络、高集成平面化天线设计等。因此,研究低成本、小型化、高增益、易集成易控的天线阵列,成为60 GHz毫米波天线技术研究的主要内容。

4 结束语

在第5代高速无线传输技术中,60 GHz无线通信技术已经拔得头筹。目前对高清晰视频流的需求直接催生了更高级数据传输速率(至少28 Gbit/s)的要求,带来更大的挑战。我国正加紧第5代移动通信系统(5G)的研发及产业化,建议下一步加大研发投入,秉承低功耗、宽方向性、高集成度的研制理念,推进超10 Gbps的室内超大容量无线通信集成系统的产业化程度,争取尽早出台我国60 GHz通信标准,研制出我国高集成单芯片60 GHz射频收发信机的商业化产品。

[1] 彭晓明,卓兰.60 GHz毫米波无线通信技术标准综述[J].信息技术与标准化,2012(12):50 -53.

[2] IEEE P802-15-3c-D13(2009)IEEE P802-15-3c-D13 Part 15.3:Wireless Medium Access Control(MAC)and Physical Layer(PHY)Specifications for High Rate Wireless Personal Area Networks(WPANs):Amendment 2:Millimeter-wave based Alternative Physical Layer Extension[S].

[3] 周逊,曹亚楠.60GHz超高速无线网络接入机制研究[J].数字通信,2013(5):38 -43.

[4] STEINBAUER M,MOLISCH A F,BONEK E.2001.The double-directional radio channel[J].IEEE Antennas and Propagation Magazine,43(4):51 -63.

[5] (美)夏鹏飞编著.实现吉比特传输的60GHz无线通信技术[M].邹卫霞,译.北京:机械工业出版社,2012.

[6] KEIICHI O,KENICHI M,MASAHARU I,et al.Wireless 1.25 Gb/s transceiver module at 60 GHz-band[C]∥IEEE ISSCC Dig Tech Papers,2002:236 -489.

[7] BRIAN F,SCOTT R,ULLRICH P,et al.A silicon 60 GHz receiver and transmitter chipset for broadband communications[C]∥IEEE ISSCC Dig Tech Papers,2006:2820-2831.

[8] ASADA H.A 60 GHz 16 Gb/s 16QAM Low-Power Direct-Conversion Transceiver Using Capacitive Cross-Coupling Neutralization in 65 nm CMOS[C]∥ISSCC Dig.Tech.Papers,2011:373 -376.

[9] OKADAK.A 60GHz 16QAM/8PSK/QPSK/BPSK Direct-Conversion Transceiver for IEEE802.15.3c[C]∥ISSCC Dig.Tech.Papers,2011:160 -161.

[10] KONG L.A 50mW-TX 65mW-RX 60GHz 4-Element Phased-Array Transceiver with Integrated Antennas in 65nm CMOS[C]∥ISSCC Dig.Tech.Papers,2013:234-235.

[11] TABESH M.A 65nm CMOS 4-Element Sub-34mW/Element 60GHz Phased-Array Transceiver[C]∥ISSCC Dig.Tech.Papers,2011:166 -167.

[12] NATARAJAN A.A Fully-Integrated 16-Element Phased-Array Receiver in SiGe BiCMOS for 60-GHz Communications[J].IEEE Jounal of Sold-State Circuits,2011,46(5):1059 -1075.

[13] OKADA K.A 64-QAM 60GHz CMOS Transceiver with 4-Channel Bonding [C]∥ ISSCC Dig.Tech.Papers,2014:346 -347.

[14] MITOMO T.A 2-Gb/s Throughput CMOS Transceiver Chipset With In-Package Antenna for 60-GHz Short-Range Wireless Communication[C]∥IEEE Jounal of Sold-State Circuits,2012,47(12):3160 -3171.

[15] TSUKIZAWA T.A Fully Integrated 60GHz CMOS Transceiver Chipset Based on WiGig/IEEE802.11ad with Built-In Self Calibration for Mobile Applications[C]∥ISSCC Dig.Tech.Papers,2013:230 -231.

[16] SAIGUSA S.A Fully Integrated Single-Chip 60GHz CMOS Transceiver with Scalable Power Consumption for Proximity Wireless Communication[C]∥ ISSCC Dig.Tech.Papers,2014:348 -349.

[17] 苏莉.60GHz,无线高速公路[J].CHIP 新电脑,2010(8):44-49.