基于SystemVerilog的机载应答机验证技术的研究*

田 毅,李 宏,马腾达,薛茜男

(1.中国民航大学,适航审定技术与管理研究中心,民用航空器适航与维修重点实验室,天津300300;2.民用飞机模拟飞行国家重点实验室,上海200232;3.中国民航大学航空自动化学院,天津300300)

机载应答机对飞机的安全有着重大影响,其作用是接收和识别其他TCAS或者二次雷达地面站的询问,再按照相应的技术要求做出应答[1]。目前,民航机载应答机有3种模式:A模式、C模式、S模式,其中A模式和C模式的脉冲形式完全相同[2]。应答机作为研制保证等级为C级的机载电子设备,会使飞机的性能显著下降,显著地增加机组工作量或降低其工作效率,对飞机安全有重大的影响。所以按照民航适航要求需要对设备中的机载复杂电子硬件(如FPGA)进行严格验证[3]。比如,在功能仿真阶段需要模拟真实信号的脉冲宽度(含阈值),在测试平台(TestBench)中模拟生成含有恰当变化的测试激励。按照RTCA DO-181的规定,A模式、C模式、S模式的各个询问脉冲都含有特殊的脉宽限制,因此如果采用传统的直接验证方式,验证工程师需要耗费大量的时间和精力来搭建测试平台。SystemVerilog是一种标准化的硬件描述和验证语言,集成了来自SUPERLOG、VERA、C、C++和 VHDL语言的特点,提供了包括带约束的随机激励产生、覆盖率驱动验证、断言等功能,适于对于复杂信号的功能仿真验证[4-5]。

1 A/C/S模式工作原理

A/C/S模式询问信号主要由4种脉冲构成,按照顺序分别为 P1、P2、P3、P4,其中 P1、P3 脉冲起到询问信号的作用,P2用于抑制应答机对旁波瓣询问信号的应答,P4是用来区分A/C模式和S模式。通过4种脉冲的有无、宽度和间隔的组合构成询问信号,主要有普通询问信号、全呼叫询问信号、仅呼叫询问信号。在实际中受到天气、收发机功率、电磁干扰等影响,接收到的询问信号脉冲不能够很好的保证在标准要求的范围内,故验证收发机对于接收脉冲信号是否能够准确识别是收发机研制的关键点。

对每种询问信号,脉冲宽度并非只是一个固定值,而是允许在一定范围内的,而脉冲之间的间隔也是如此。综合上述介绍,每种询问信号有2~4个脉冲(一定有P1、P3),去掉各种询问信号不应有的脉冲,各种询问信号均可归结为图1所示波形,其中A0、A1、A2、A3 分别为脉冲宽度,B0、B1、B2、B3 分别为脉冲间隔(B中的最后一个非零值为两个询问信号间隔)。

图1 询问信号波形图

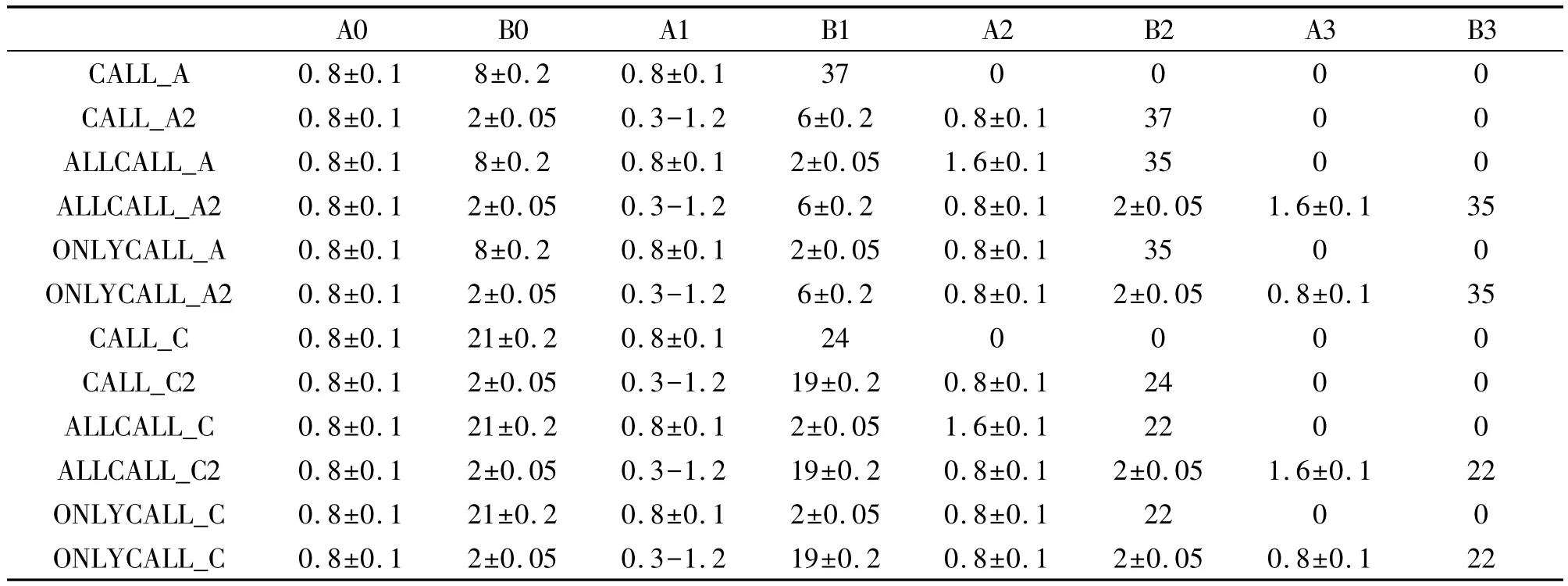

各种询问信号的脉冲宽度、间隔如表1。

表1 各种询问信号的脉冲宽度、间隔表 单位:μs

1.1 普通询问信号

普通询问信号只有P1、P2和P3,按照模式分成A模式和C模式,这两种模式均有P1和P3,且脉冲宽度均为0.8 μs,只是P1和P3的间隔不同,A模式为8 μs,C 模式为21 μs。还可按照对 A 模式询问信号是否抑制、A模式抑制旁瓣询问信号、C模式询问信号、C模式抑制旁瓣询问信号,记为CALL_A、CALL_A2、CALL_C、CALL_C2。

1.2 全呼叫询问信号

全呼叫询问信号和普通询问信号类似,只是在P3后面加入了脉冲宽度为1.6 μs的P4,其分类方法也和普通询问信号一样,分为4种询问信号:A模式全呼叫询问信号、A模式全呼叫抑制旁瓣询问信号、C模式全呼叫询问信号、C模式全呼叫抑制旁瓣询问信号,记为 ALLCALL_A、ALLCALL_A2、ALLCALL_C、ALLCALL_C2。

1.3 仅呼叫询问信号

仅呼叫询问信号和全呼叫询问信号类似,只是在P3后面加入了脉冲宽度为0.8 μs的P4,其分类方法也和普通询问信号一样,分为4种询问信号:A模式全呼叫询问信号、A模式全呼叫抑制旁瓣询问信号、C模式全呼叫询问信号、C模式全呼叫抑制旁瓣询问信号,记为 ONLYCALL_A、ONLYCALL_A2、ONLYCALL_C、ONLYCALL_C2。

2 测试激励

从表1中可以看出,大部分数据都是μ±σ型,其中μ为理想值,σ为容差,所以可以用正态分布来描述此类数据。然而,例如CALL_A2的A1,其理想值为0.8 μs,容差上限为1.2 μs,下限为0.3 μs。容差的上限和下限并不相等,且下限较为接近0,使用正态分布容易产生负值等错误,故需要对正态分布进行改进[6]。

2.1 基于正态分布的脉冲宽度、间隔

由于脉冲宽度和间隔均有一定的容限,所以采用正态分布来产生测试激励,能够更精确的描述实际情况,通过改变标准差来调整注入错误的概率。这样既能很好的描述脉冲的宽度,又能很方便的注入错误。采用系统函数$dist_normal()生成测试向量,即

随机生成正确激励的概率为:

式中seed为随机种子,max为容差上限,min为容差下限,mean为平均值,dev为标准差。其中max、min、mean为已知值,可通过调整标准差值,使P(rignt)=90%。

2.2 改进正态分布

表1中的多数情况均可用正态分布来实现,但是 CALL2 的 A1 值为 0.3 μs~1.2 μs,其期望值为0.8 μs,其值并非对称,且单纯使用正态分布会出现错误,即有一定概率产生负值,或产生一个很大的时间。所以要设定一个故障范围,将故障值约束在一定范围之内。300 ns~1 200 ns为正常值,设定2 00ns~300 ns和1 200 ns~1 400 ns为故障值,当随机出的数值不在正常值的区间内时,则归结到该故障值内,故障值采用平均分布。改进正态分布概率如图2所示。

图2 改进正态分布概率图

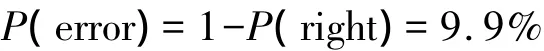

为保证随机生成正确激励的概率约等于90%,将标准差设为268,则

则随机生成错误激励的概率为

由于将所有的错误情况都归结到[200:299]和[1201:1400]这个区间内的平均分布,此平均分布的区间长度为400,则此平均分布的概率为

2.3 脉冲生成

应答机12种询问信号都可归结成图1所示波形,依据表1的数据,来生成相应的询问信号。对于每个脉冲,只需保证脉冲宽度和间隔符合要求即可,由于这两者均为随机数,所以采用并行语句来描述。

询问信号最多有4个脉冲,每个脉冲的形式相同,所以通过for循环来逐个生成,即通过for循环来不断的调用gen_forkwave任务。

2.4 询问信号生成

由于各种询问信号都可以归结为图1所示的波形,所以只写一个task使其能产生各种波形。首先将各种询问信号进行定义,将其定义成枚举类型wavemode,作为task的输入变量,以识别所需产生的询问信号。

task通过输入的枚举变量来识别所需生成的询问信号后,还要从表1中查出对应的脉冲宽度和间隔。所以,将各种询问信号的脉冲宽度和间隔都存入一个4维数组常量 ALL_WAVE_INFO[12][2][4][6]中。其中第一维用来区分询问信号类型,第二维用来区分脉冲宽度和间隔,第三维用来指示脉冲宽度An和间隔Bn中的n,第四维用来存储该随机数值的信息。

3 验证

验证主要提供硬件设计符合需求的证据。在验证过程中采用适宜的方法对硬件进行检验,并进行测量。常用的方法有评审、分析及测试或三者的组合。

待验应答机所选用的是Altera公司的CycloneⅢ系列的某型芯片,并在设计中调用了内部的IP核资源,包括:加法器、乘法器、PLL、缓存核等。项目组按照适航要求,对待验证FPGA的原厂提供的质量证明、生产记录及该型元器件成功工作的服务历史等相关信息进行了评估,并按照原厂指导对于主要功能IP(如缓存)进行了验证,从而保证这些设计不可控元素的可靠性。在此基础上,搭建下述验证分析平台[7-8]。

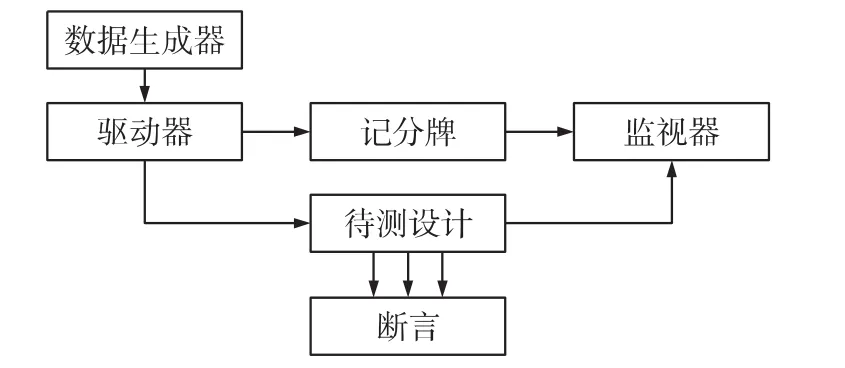

3.1 验证分析平台结构

采用分层结构来搭建验证平台[9-10],主要由数据生成器、驱动器、记分牌、监视器和断言等组件组成,如图3所示。

图3 测试平台结构图

数据生成器用来生成数据模式,具体到本验证平台,就是生成一组询问模式变量,都写入邮箱传递给驱动器组件。

驱动器根据数据生成器的数据,生成相应的波形数据,发送给待测设计;在发送给记分牌时,并将其中的错误数据过滤掉,只将正确数据发送过去。

监视器监视待测设计的输出,并将其传给记分牌。记分牌将驱动器和监视器的数据作对比,即可判断待测设计的正确性。

断言组件单独写成一个module,待测设计的输入和输出都作为断言模块的输入,检测待测设计的属性是否符合设计需求。在测试平台中,通过关键字blind与待测设计绑定[11]。

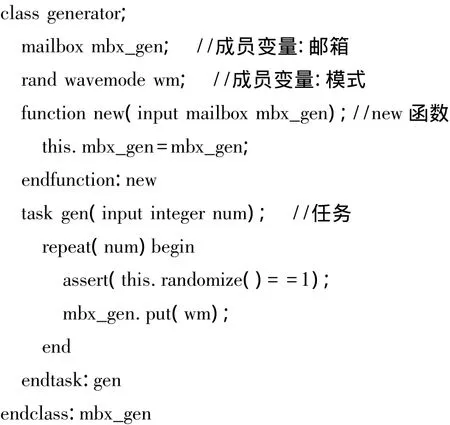

3.2 组件

除断言以外的模块都是通过类(class)来实现的,在类中定义成员变量及函数、任务,而组件之间的通信都是通过邮箱(mailbox)来实现,以数据生成器为例,其代码如下:

在每个类中,首先要定义成员变量,包括用作通信的邮箱以及需要随机的变量等;由于在实例化时需要给该类加一个邮箱参数,所以还要定义一个带参数的new()函数;最后就是任务,通过任务来执行相应的动作,包括向邮箱内写数据以传递给后面的组件等。

图4 概率分布图

4 实验结果

4.1 改进型正态分布

以CALL2的A1值为例,采用改进型正态分布生成1000次随机值,各区间的概率分布如图4所示,生成结果符合图2的预期结果。随机变量被约束在200~1 500的范围之内,避免生成负值造成仿真错误,并且避免生成一个极大的正值造成仿真效率下降。

4.2 仿真激励波形

依据机载应答机各种模式询问信号要求,应用改进的正态分布算法产生脉冲宽度和间隔,生成的各种模式仿真激励波形如图5所示。

图5 仿真激励波形图

4.3 仿真结果

在验证平台中将上述仿真激励注入到待测设计中,得到的仿真结果如图6所示。

图6 仿真波形图

5 结论

本研究采用改进型正态分布生成测试向量,通过SystemVerilog验证语言搭建验证平台实现了对应答机可编程逻辑器件的验证。改进后的测试激励生成算法既避免了产生负值的错误,又模拟了真实情况,在对机载应答机的验证中取得了良好的效果,达到了高效、精确验证的目的。该方法有望应用于其他机载电子设备可编程逻辑器件的设计验证中。

[1]马进.基于FPGA和TCAS与S模式应答机综合化数字中频接收系统的设计与仿真[D].上海:上海交通大学,2011.

[2]MH/T 4010—2006,空中交通管制二次雷达设备技术规范[S].

[3]王鹏,田毅.DO-254标准在机载电子硬件审定中的应用[J].中国民航大学学报,2010,5(28):17-24.

[4]Mark Zwolinski.Digital System Design with SystemVerilog[M].Pearson,2009,24-78.

[5]Christian B Spear.SystemVerilog for Verification:A Guide to Learning the Testbench Language Features[M].Springer,2008,44-125.

[6]张建平,王睿韬.对数正态分布下基于MAM的VFD加速寿命试验研究[J].电子器件,2008,31(6):1735-1738,1742.

[7]周德新,金志威,王鹏,等.基于SystemVerilog的SRAM控制器IP 核验证[J].电子器件,2012,35(5):619-622.

[8]刘萌,冯海洲,李康,等.基于SystemVerilog的网络处理器验证平台设计[J].电子器件,2011,34(3):320-323.

[9]Janick Bergeron,Eduard Cerny,Alan Hunter,et al.Verification Methodology Manual for SystemVerilog[M].Springer,2005,23-145.

[10]Mark Glasser.Open Verification Methodology Cookbook[M].Springer-Verlag,2009,47-129.

[11]Srikanth Vijayaraghavan,Meyyappan Ramanthan.A Practical Guide for SystemVerilog Assertions[M].Springer,2005,21-59.