基于多线阵CCDS相机的大幅面扫描仪高精度实时拼接实现新方法*

别俊锋,叶玉堂,刘 霖,刘娟秀,贾宏宇,骆才华,王 平,徐文涛,郝 霞

(电子科技大学光电信息学院,成都610054)

基于多线阵CCDS相机的拼接型高精度大幅面扫描仪的研制一直是国内、外学者及产业界关注的重点领域[1],但是由于涉及精密光路设计[2]、复杂机械平台[3]、完备硬件系统[4]、友好人机界面、智能算法实现这五个关键技术[5-6],其中高精度实时拼接技术又是其中的重点难点。迄今为止,基于多线阵CCDS相机的拼接型高精度大幅面扫描仪的全部关键技术基本上被国外跨国公司与大型研究机构所垄断,国内完全依靠进口[7-9]。

高精度实时拼接技术是多线阵CCDS相机的大幅面扫描仪中的重点难点。由于线阵CCDS相机的视场有限,在视场范围要求大扫描精度高的大幅面扫描仪应用背景下,单个三线阵CCDS相机显然不能满足需求,因此需要多个三线阵相机拼接实现拼接最重要的指标是保证图像信息不丢失不错位最理想的情况是,所有三线阵CCDS相机保持在同一水平面,相邻两个相机采集图像的像素连续。

为了适应拼接型多线阵CCDS大幅面扫描仪这一应用需求,通常采用光学拼接或光学拼接加入软件后续处理[10]。光学拼接通过分光棱镜将多个线阵CCDS相机首位相连,即前一级CCDS相机最后一个有效像素与下一级CCDS相机第1个有效像素相连,其精度要求偏差在1个像素以内,且多个CCDS相机所有像素必须在同一个水平面上,这对机械加工精度要求非常高,相应成本也非常高,其拼接精度随着使用时间增加而降低[11]。光学拼接加入软件后续处理通过将相邻两个CCDS相机有效像素进行重叠以此保证图像信息不丢失,然后将采集到的图像信息保存在电脑内存里,通过软件算法将每个相机采集到的图像数据上下左右平移进行拼接,这种拼接方式对机械的精度要求有所降低,但是对电脑配置要求较高,拼接时间较长需要2 s~3 s,对大幅面扫描仪的实时性有一定影响[12]。

针对这一问题,笔者深入研究了FPGA/SDRAM/CCDS的内部结构,通过多次试验验证,提出了一种新的基于多线阵CCDS相机的大幅面扫描仪高精度实时拼接实现新方法——硬件拼接法[13-18]。

1 基本理论

1.1 拼接原理

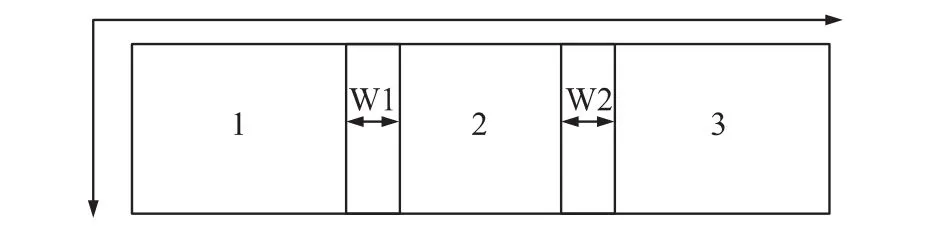

为了保证相邻相机首尾相连处数据不丢失,必须使两相机之间有效像素部分重合,如图1拼接原理图所示。

图1 拼接原理图

相机1与相机2重叠W1个像素,相机2与相机3重叠W2个像素。将SDRAM的地址分为3个地址分块,相机1对应的初始地址为ADDRESS_1,相机2对应的初始地址为ADDRESS_2,相机3对应的初始地址为ADDRESS_3。三线阵CCDS相机逐行扫描,将3个相机采集到的每一行数据分别连续存储到SDRAM开辟的3个地址分块里,因为SDRAM的地址与数据一一对应,知道每一行数据的首地址,通过对偏移量的设置,从指定每行数据首地址位开始连续读取数据即可对3个相机的数据进行实时拼接。

1.2 拼接过程中出现的实际情况与处理方法

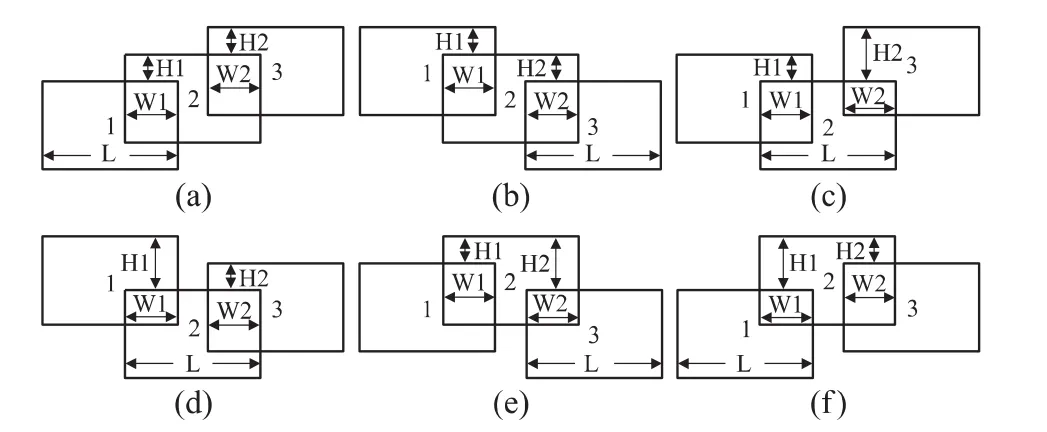

实际过程中,由于机械平台加工的精度问题,3个相机可能不在同一水平面上,并且相邻两相机的重叠像素部分也不一定相同,就造成常规数据传输中有错位现象产生。根据实验与分析,拼接过程中会出现6种可能情况,如图2(a)、2(b)、2(c)、2(d)、2(e)、2(f)所示。

图2 拼接中出现的六种情况

图2(a)为相机1水平位置大于相机2水平位置,相机2水平位置大于相机3水平位置时,图像有效数据错位情况。图2(b)为相机1水平位置小于相机2水平位置,相机2水平位置小于相机3水平位置时,图像有效数据错位情况。图2(c)为相机2水平位置大于相机1水平位置,相机1水平位置大于相机3水平位置时,图像有效数据错位情况。图2(d)为相机2水平位置大于相机3水平位置,相机3水平位置大于相机1水平位置时,图像有效数据错位情况。图2(e)为相机3水平位置大于相机1水平位置,相机1水平位置大于相机2水平位置时,图像有效数据错位情况。图2(f)为相机1水平位置大于相机3水平位置,相机3水平位置大于相机2水平位置时,图像有效数据错位情况。

因此需要先确定扫描仪3个相机处于何种位置情况,相机每一行像素个数为L=5340个,上位机根据特定情况设定 H1、H2、W1、W2 的值,根据 H1、H2 W1、W2的预设值计算出需要缓存数据最大行数,相机2每行缓存数据的读出首地址与末地址,相机3每行缓存数据的读出首地址与末地址,最后顺序读写出每一个相机缓存数据传输到上位机实时显示。

图2所示6种情况中的写缓存初始地址都是一致的,即,相机 1写缓存初始地址 ADDRESS_WRITEBUFFER_1=ADDRESS_1,相机2写缓存初始地址 ADDRESS_WRITEBUFFER_2=ADDRESS_2,相机写缓存初始地址ADDRESS_WRITEBUFFER_3=ADDRESS_3。

针对图2(a)的情况,需缓存BUFFER_LINE=H1+H2+1行数据,相机2连续写入H1+1行数据后需对写入地址初始化,相机3连续写入H1+H2+1行数据后需对写入地址初始化。相机1写初始地址ADDRESS_WRITE_1=ADDRESS_1+(H2-H1)·L+H2-H1,相机2写初始地址ADDRESS_WRITE_2=ADDRESS_2+H2·L+H2,相机 3写初始地址ADDRESS_WRITE_3=ADDRESS_3。相机1读初始地址ADDRESS_READ_1=ADDRESS_1+(H1+H2)·L+H1+H2,相机2读初始地址ADDRESS_READ_2=ADDRESS_2+H2·L+W1+H2,相机3读初始地址ADDRESS_READ_3=ADDRESS_3+W2。

针对图2(b)的情况,需缓存BUFFER_LINE=H1+H2+1行数据,相机1连续写入H1+H2+1行数据后需对写入地址初始化,相机2连续写入H2+1行数据后需对写入地址初始化。相机1写初始地址ADDRESS_WRITE_1=ADDRESS_1,相机2写初始地址 ADDRESS_WRITE_2=ADDRESS_2+H1·L+H1,相机3写初始地址ADDRESS_WRITE_3=ADDRESS_3+(H1+H2)·L+H1+H2。相机 1读初始地址ADDRESS_READ_1=ADDRESS_1,相机2读初始地址 ADDRESS_READ_2=ADDRESS_2+H1·L+W1+H1,相机3读初始地址 ADDRESS_READ_3=ADDRESS_3+(H1+H2)·L+H1+H2+W2。

针对图2(c)的情况,需缓存BUFFER_LINE=H2+1行数据,相机1连续写入H1+1行数据后需对写入地址初始化,相机3连续写入H2+1行数据后需对写入地址初始化。相机1写初始地址ADDRESS_WRITE_1=ADDRESS_1+(H2-H1)·L+H2-H1,相机2写初始地址ADDRESS_WRITE_2=ADDRESS_2+H2·L+H2,相机 3写初始地址ADDRESS_WRITE_3=ADDRESS_3。相机1读初始地址ADDRESS_READ_1=ADDRESS_1+(H2-H1)·L+H2-H1,相机2读初始地址ADDRESS_READ_2=ADDRESS_2+H2·L+W1+H2,相机 3读初始地址ADDRESS_READ_3=ADDRESS_3+W2。

针对图2(d)的情况,需缓存BUFFER_LINE=H1+1行数据,相机1连续写入H1+1行数据后需对写入地址初始化,相机3连续写入H2+1行数据后需对写入地址初始化。相机1写初始地址ADDRESS_WRITE_1=ADDRESS_1,相机2写初始地址 ADDRESS_WRITE_2=ADDRESS_2+H1·L+W1+H1,相机3写初始地址ADDRESS_WRITE_3=ADDRESS_3+(H1-H2)·L+H1-H2。相机1读初始地址ADDRESS_READ_1=ADDRESS_1,相机2读初始地址ADDRESS_READ_2=ADDRESS_2+H1·L+W1+H1,相机3读初始地址 ADDRESS_READ_3=ADDRESS_3+(H1-H2)·L+H1-H2+W2。

针对图2(e)的情况,需缓存BUFFER_LINE=H2+1行数据,相机1连续写入H2-H1+1行数据后需对写入地址初始化,相机2连续写入H2+1行数据后需对写入地址初始化。相机1写初始地址AD DRESS_WRITE_1=ADDRESS_1+H1·L+H1,相机 2写初始地址ADDRESS_WRITE_2=ADDRESS_2,相机3写初始地址ADDRESS_WRITE_3=ADDRESS_3+H2·L+H2。相机1读初始地址ADDRESS_READ_1=ADDRESS_1+H1·L+H1,相机2读初始地址AD DRESS_READ_2=ADDRESS_2+W1,相机3读初始地址ADDRESS_READ_3=ADDRESS_3+H2·L+H2+W2。

针对图2(f)的情况,需缓存BUFFER_LINE=H1+1行数据,相机2连续写入H1+1行数据后需对写入地址初始化,相机3连续写入H1-H2+1行数据后需对写入地址初始化。相机1写初始地址AD DRESS_WRITE_1=ADDRESS_1+H1·L+H1,相机 2写初始地址ADDRESS_WRITE_2=ADDRESS_2,相机3写初始地址ADDRESS_WRITE_3=ADDRESS_3+H2·L+H2。相机1读初始地址ADDRESS_READ_1=ADDRESS_1+H1·L+H1,相机 2读初始地址ADDRESS_READ_2=ADDRESS_2+W1,相机3读初始地址ADDRESS_READ_3=ADDRESS_3+H2·L+H2+W2。

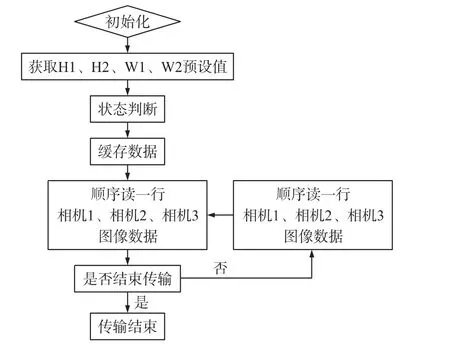

图3 拼接传输流程图

2 实验结果与讨论

2.1 方法执行过程

多线阵CCDS相机的大幅面扫描仪高精度实时拼接实现新方法流程如图3所示。根据主要器件的特性,上电后需对FPGA、SDRAM初始化,使其处于正常工作状态。从上位机获取H1、H2、W1、W2的预设值,判别相机位置处于何种情况。定义H1最高位为1时,相机1水平位置高于相机2水平位置H1最高位位为0时,相机1水平位置低于相机2水平位置。定义H2最高位为1时,相机2水平位置高于相机3水平位置,H2最高位为0时,相机2水平位置低于相机3水平位置。图2所示6种情况分对应H1、H2预设值的6种状态。H1最高位为1,H2最高位为1时对应图2(a);H1最高位为0,H2最高位为0时对应图2(b);H1最高位为0,H2最高位为1,且H1小于H2时对应图2(c);H1最高位为0,H2最高位为 1,且 H1大于等于 H2时对应图2(d);H1最高位为1,H2最高位为0,且H1小于H2时对应图2(e),H1最高位为1,H2最高位0,且H1大于等于H2时对应图2(f)。获取预设值后就进行数据缓存,按照相机编号逐行读出图像数据,判断读地址是否需要初始化,按照相机编号逐行写入图像数据,判断写地址是否需要初始化,最后判断是否接收到上位机发出的结束信号。

2.2 大幅面扫描仪上的实际使用效果

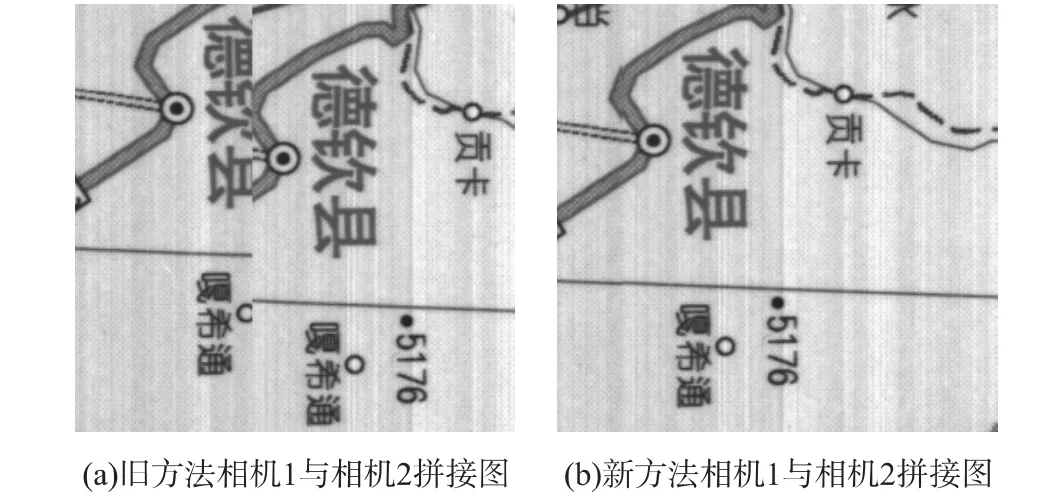

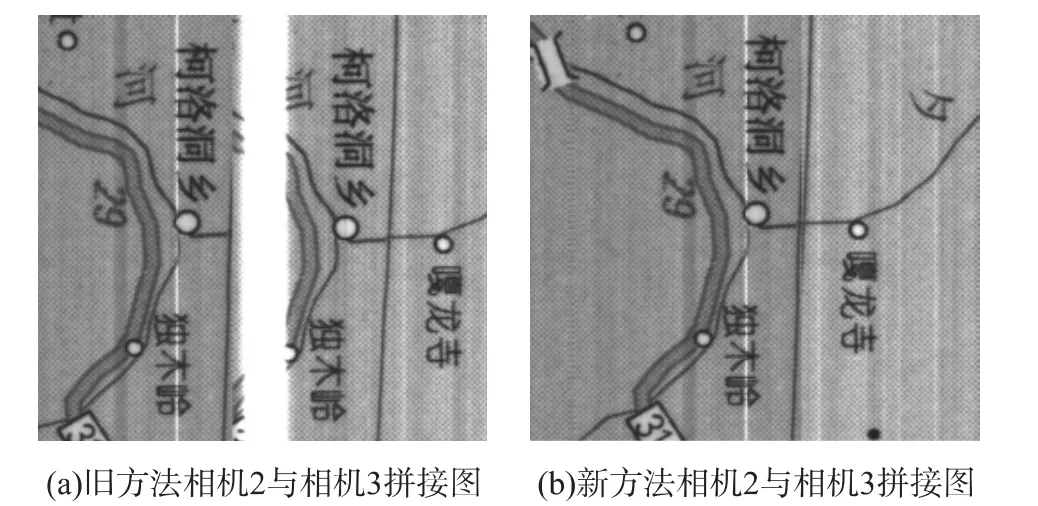

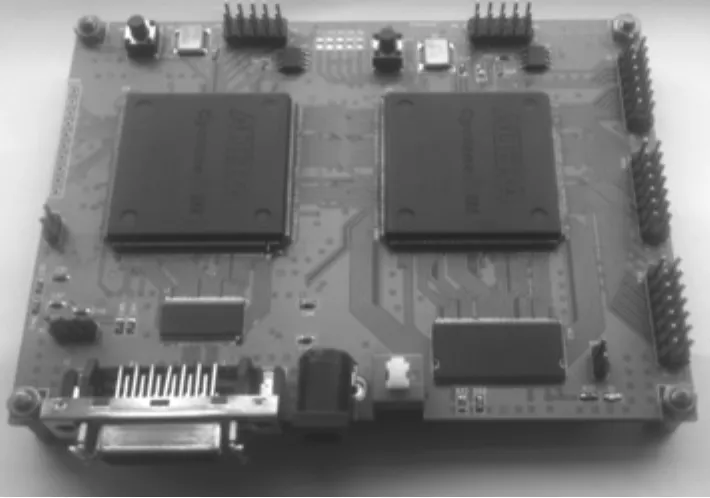

采用多线阵CCDS相机的大幅面扫描仪高精度实时拼接实现新方法后,3个相机图像数据能够实时拼接传输,图像水平错位现象得以解决,重叠部分裁剪后实现无缝拼接。经分析测试,H1=56,H2=6,W1=118,W2=168,且 H1 最高位为0,H2 最高位为0,即对应图2(b)所示情况。图4(a)为采用新方法前相机1与相机2拼接效果图,图4(b)为采用新方法后相机1与相机2拼接效果图。图5(a)为采用新方法前相机2与相机3拼接效果图,图5(b)为采用新方法后相机2与相机3拼接效果图。图6为拼接型大幅面扫描仪整机图,图7为硬件拼接核心板。

图4

图5

图6 拼接型大幅面扫描仪整机图

图7 硬件拼接核心板

3 结论

通过对基于多线阵CCDS相机的大幅面扫描仪拼接方法的深入分析,并比较现有的通行方式,提出了一种高精度实时拼接的新方法,制作了国内第一台基于多线阵CDDS相机的拼接型大幅面扫描仪解决了拼接过程中水平错位、无缝拼接的难题。

实验及测试结果表明:项目组制作的大幅面扫描仪最大幅面A0,光学分辨率高达1 200 DPI,扫描速度达到2.54 cm/s,扫描及拼接精度能达到+/-1像素,能够进行实时拼接传输。

高精度实时拼接新方法在该扫描装备的成功实施,解决了在基于多线阵CCDS相机的大幅面拼接型高精度扫描仪的诸多难题,填补了该领域的工程应用空白。据我们所知,在应用上成功实现大幅面拼接性高精度一次性成像扫描仪的高精度实时硬件拼接,国内、外未见报道。

在以后的工作中,将对高精度实时硬件拼接进行进一步的优化处理,并在速度保障的情况下,争取进一步提高图像质量,能够更加接近理想状态。

[1]Kumpulainen T,Latokartano J,Vihinen J,et al.Scanner Test Pattern for Evaluation of Beam Manipulation Accuracy[C]//Assembly and Manufacturing(ISAM),2011 IEEE International Sym-posium on,2011,1-5.

[2]任建岳,孙斌,张星祥.TDICCD交错拼接的精度检测[J].光学精密工程,2008,16(10):1852-1857.

[3]武星星,刘金国.三线阵立体测绘相机时间系统优化与实时监测[J].光学精密工程,2012,20(5):1022-1030.

[4]朱宏殷,郭永飞,司国良.多TDICCD拼接相机成像非均匀性实时校正的硬件实现[J].光学精密工程,2011,12(19):3025-3041.

[5]Hyuck Choo,Garmire D,Demmel J,et al.Simple Fabrication Process for Self-Aligned High-Performance Microscanners-Demonstrated Use to Generate a 2-D Ablation Pattern[J].Microelectro mechanical Systems,2007,16(2):260-268.

[6]Hu Tao,Chen Yanan.Design of the Linear Array CCD Acquisition System that Line Frequency and Integration Time Adjustable[C]//Electronics and Optoelectronics(ICEOE),2011 International Conference on,2011,2:253-256.

[7]Wang J H.A Topology Set Method for Vectorization[C]//Eighth ACIS International Conference on Software Engineering,IEEE,2007,1:229-234.

[8]Nicholson S W,Peiffer R,Shaw J D.Hardware in Libraries:Making Informed Choices[J].Library Hi Tech,2011,1(29):73-82.

[9]Bhavsar A V,Rajagopalan A N.Range Map with Missing Data-Joint Resolution Enhancement and Inpainting[C]//2008 Sixth Indian Conference on Computer Vision,Graphics & Image Processing,IEEE,2008:259-365.

[10]王勤,王庆友,齐龙.多线阵CCD拼接检测宽幅PS版表面缺陷的研究[J].光电子激光,2005,16(11):1350-1354.

[11]Linden J,Knappe C,Richter M,et al.Limitations of ICCD Detectors and Optimized 2D Phosphor Thermometry[J].Measure ment Science & Technology,2012,3(23):8.

[12]Monoi M,Sasaki S,Dobashi K,et al.A Single-Layer CCD Image Sensor with Wide Gap Electrode and Gradual Potential Channe[C]//Society of Photo-Optical Instrumentation Engineers(SPIE Conference Series,SPIE,2009,7247:12.

[13]夏玉立,雷宏,黄瑶.用Xilinx FPGA实现DDR SDRAM控制器[J].微计算机信息,2007,23(9-2):209-211.

[14]马灵,杨俊峰,宋克柱.地震数据采集中基于FPGA的多DDR SDRAM控制器设计[J].中国科学技术大学学报,2010,40(9):939-945.

[15]Zheng Dechun,Yang Yang,Zhang Ying.FPGA Realization o Multi-Port SDRAM Controller in Real Time Image Acquisition Sys tem[C]//Multimedia Technology(ICMT),2011 Internationa Conference on,2011,4925-4928.

[16]陈学飞,汶德胜,郑培云.基于CPLD的CCD视频信号处理电路的设计与硬件实现基于CPLD的CCD视频信号处理电路的设计与硬件实现[J].电子器件,2008,31(3):807-810.

[17]Zhou Zude,Cheng Songlin,LiuQuan.Application ofDDR Controller for High-Speed Data Acquisition Board[C]//Innovative Computing,Information and Control,2006.ICICIC’06.First Inter national Conference on,2006,2:611-614.

[18]Pan Guangrong,Feng Da,Wang Qin,et al.The Design and Imple mentation ofAMBA Interfaced High-Performance SDRAM Controller for HDTV SoC[C]//Computer Science and Information Engineering,2009 WRI World Congress on,2009,3:448-452.