统一并行体系结构实验平台研制

蔡 晔,周春云,罗秋明

(1.深圳大学国家高性能中心深圳分中心,广东深圳 518060;2.扬州万方电子技术有限责任公司,江苏扬州 225006)

1 并行体系结构的发展

近年来,随着微处理器技术的发展和进步,主流并行计算体系结构获得了飞速发展。目前多核处理器已经成为主要的计算单元,传统的并行体系结构底层逐步向片内过渡,并行计算的并行层次相应增加。另外,混合异构结构迅速发展,快速标量部件、向量部件、FPGA、GPU 等加速部件已充分应用到在并行体系结构上[1]。

SMP(symmetric multi-processor)结构是传统并行体系结构中高性能服务器和工作站架构提升性能的有效手段。SMP当前发展趋势是逐步向片内多核过渡,将SMP系统实现在一块芯片内部。由于多个处理器集成在一块芯片上,故采用共享缓存或者内存的方式,同时利用片内的高带宽总线来替代片外总线,可以有效降低多线程通信延迟。CC-NUMA(cache-coherent NUMA)结构主要针对SMP结构在可扩展上的局限性,实现在更大规模上的并行计算。传统CC-NUMA互连技术一般使用多级交叉开关结构来减少连接代价,由于受物理通信链路数量以及并行总线频率增长的约束,以及专用互连芯片带来了额外的延迟,早期的结构在多核处理器出现后,处理器间通信能力很难适应日益增长的片上通信带宽,因此出现了处理器间直接互连技术(direct link)。direct link的主要技术特点:一是首先处理器集成内存控制器,可让主内存响应时间更快,同时可降低缓存大小以及芯片制造的成本;二是通过专用连接通道实现处理器间直接通信,避免了专用桥或路由芯片的使用,可减少系统成本和转发带来的延迟;三是基于先进的串行通信技术来提供高速连接,通过一路或多路并行来保证互连带宽。

在系统级互连方面,典型结构依然为机群CLUS-TER 结构以及MPP(massively parallel processor)结构,CLUSTER 是一种松耦合结构,MPP 为紧耦合结构。MPP处理器之间通常由伸缩性较好的特制的互连网络(如Mesh、交叉开关网络等)相连,每个处理器之间通过消息传递的方式进行通信和协调。机群系统将大量同一品种的工作站或微机通过高速网络互连,以构成廉价的高性能计算机系统。MPP 和CLUSTER 结构在多核处理器出现后,面临着新的挑战,多核作为一种新的并行层次出现,并行软件需要相应的发展变化,或寻求从底层来应对,对多核加以隐藏,或是把高端计算里面并行程序设计语言和环境(如MPI和OpenMP)组合起来用,根据多核的特点,充分利用新的体系结构的优势加以性能优化。另外,混合异构结构的普遍出现和应用,导致软件基础架构的关键部分难以跟上变化的步伐,也给传统并行算法的设计和教学带来了机遇和挑战。

计算机并行体系结构和并行软件日新月异的发展,导致高校在进行并行体系结相关课程教学时,首先要及时跟踪国内外并行体系结构领域的主流技术和最新进展,并反映到课堂教学上;其次要不断更新相关的实验室设施、设备,以及实践方法和手段,以适应不断变化的并行体系结构的教学需求。

深圳大学国家高性能中心深圳分中心致力于国产个人高性能计算机的研制,先后和相关单位联合研制了KD 系列[2-3]和SD 系列[4]个人高性能计算机(personal high performance computer,PHPC)系统[5]。从2010年起,结合科研优势,在本科教学层次成立了高性能计算特色班,立足为高性能计算发展和并行计算培养高素质的基础学术性人才和应用型综合人才。为了满足教学和实验的需求,结合研制PHPC 系统的技术积累,和相关公司联合设计了一种统一并行体系结构实验平台。“统一实验教学”平台的概念由清华大学计算机实验教学中心提出[6-7],并设计了计算机硬件统一实验平台,完成了对计算机硬件课程实验的整合,支持计算机硬件系列课程中的主干课程实验(数字逻辑、计算机组成原理和计算机系统结构)。实践表明,有效减少了教学资源的硬件浪费,缩短了学生熟悉实验设备的时间,提高学生实验的系统性。

本文研制的统一并行体系结构实验平台(以下简称实验平台)基于“统一实验教学“的思想,采用国产高性能多核处理器龙芯3A(4核)或3B(8核)[8]进行设计。该实验平台具有以下特点:(1)便携性,采用PHPC技术,在单一定制机箱(440 mm×420 mm×320mm)单元内可支持高达万亿次的并行计算能力;(2)灵活性,可通过系统配置支持最新的各种并行体系机构以及互联结构,并实现功能扩展;(3)统一性,可将计算机并行体系结构相关的多门课程和实验教学统一到一个实验平台上;(4)开放性,从系统硬件、BIOS、操作系统以及并行计算基础平台都进行了开源,可支持更深入的教学或科研工作;(5)先进性,符合当前计算机并行体系结构发展的最新进展。

2 统一并行体系结构实验平台设计方案

该实验平台的设计目标是利用PHPC 技术,设计便携的面向并行体系结构教学和实验用的仪器平台,系统峰值性能可达万亿次,不但能满足教学和实验的需求,而且能提供给科研人员使用。并行体系结构实验平台采用了国产龙芯3号处理器,龙芯3号的互连接口采用了扩展的HyperTransport(HT)[9]协议,既可以连接IO,也可以实现多芯片间的直接互连(direct-link)。龙芯3 号在单芯片上同时提供了板级互连接口(HT0,16位,可拆分为2个8位通道使用)以及系统级的互连接口(HT1,16位,可拆分为2个8位通道使用)。在统一并行体系结构实验平台中,HT0用来实现2个处理器直接互连以实现CC-NUMA 结构,而HT1则拆分为2个8位通道,其中高8位HT1通道用于连接系统北桥和南桥,进行网络IO 接口扩展,扩展后的网络IO 接口信号连接到背板的FPGA芯片上进行交换;低8位HT1通道则直接连接到背板的FPGA 互联芯片上,支持通过处理器前端总线直接高效地进行交换。背板通过FPGA 实现10个处理器的互连,通过配置可实现不同的互连方式和拓扑结构。该实验平台可满足并行体系结构相关课程,包括:计算机高级体系结构[10],并行计算机体系结构,并行算法的设计与分析,并行算法实践,并行程序设计等[11-14]的教学和实验需求。

2.1 实验平台总体结构

该实验平台总体组成包括:440mm×420mm×320 mm 单一定制机箱;计算节点(双路龙芯3/AB 8核处理器刀片)×5,集成10个(PE1—PE10)龙芯3A8核(或龙芯3B8核)处理器,系统峰值性能可达万亿次(采用龙芯3B);前置服务主板1个,提供系统引导、磁盘存储、用户登录、任务调度等功能;系统支持双交换通道,即16端口千兆以太网交换通道以及背板定制的FPGA 互连交换通道,其中16端口千兆以太网交换机用于系统内部管理,连接前置服务主板和5个龙芯计算刀片,而背板上定制的FPGA互连通道则用于计算节点之间计算和数据交换使用,可提供2种互连交换模式,一种为48端口以太网交换方式,在这种模式下,处理器通过南桥扩展的网络接口直接连接到FPGA进行网络交换;另一种为通过处理器前端HT总线直接进行交换的模式,即MPP互连模式,在MPP互连模式下,通过配置内部路由模块的参数可实现计算节点间不同的系统互连和拓扑结构。系统总体结构参见图1。

图1 系统总体结构

2.2 计算节点结构

该实验平台的计算节点采用2 个龙芯多核处理器作为计算处理单元(PE),2 个龙芯多核处理器之间通过基于HT 总线的直接互连技术实现CC-NUMA 并行结构,该系统在设计时可同时兼容龙芯3A(4核)或龙芯3B(8 核)处理器。在采用龙芯3B 时的计算节点结构如图2 所示,单处理器为8 核SMP结构,双处理器之间使用直接互连技术,通过处理器前端HT 总线构成2 路CC-NUMA 结构,每个计算节点可实现16 核的CC-NUMA 结构的高性能并行系统。

图2 双路龙芯CC-NUMA结构

与常规CC-NUMA 结构系统共享一个IO 套片不同,该实验平台每个处理器采用了独立的IO 套片进行IO 功能扩展,每个处理器计算节点为每个处理器提供了高达5路千兆网络互联接口。因此系统并行结构在不使用处理器间CC-NUMA 互连通路时(通过软件配置)可以配置为SMP-CLUSTER(MPP)两级并行结构,在使用处理器之间互连时可以配置为SMP-(CC-NUMA)-CLUSTER(MPP)的三级并行结构。在表1 中列出了该实验平台支持的7 种并行体系结构。由于龙芯3B处理器内部采用了向量部件加速部件技术,在使用龙芯3B 处理器时,还支持基于向量部件的混合异构结构。每个计算节点提供了高速FLASH(SATA DOM 盘)本地存储,也可利用外部共享磁盘阵列处理海量数据。

当采用MPP互联模式时,可通过对FPGA 内部实现的路由器的连接和对参数进行灵活配置以实现不同的互联拓扑结构。实现的路由器结构示意图见图3。每个处理器通过HT1 低8 位互连通道与FPGA内部实现的一个路由器(Router)相连接,路由器支持东、南、西、北和上、下总计6 个连接通路,用于和其他处理器的路由器连接,每个方向可根据实际需求连接和配置使用。因此可通过不同的配置实现常见的二维(使用东、南、西、北4个通道)、三维(使用东、南、西、北和上、下6 个通道)、环形(使用东、西2 个通道)以及树形等拓扑结构,可在教学和实验中让学生实际配置,以及评估不同互连拓扑的结构特点并进行性能分析。

表1 统一并行体系结构实验平台并行体系结构的配置

图3 FPGA路由器结构示意图

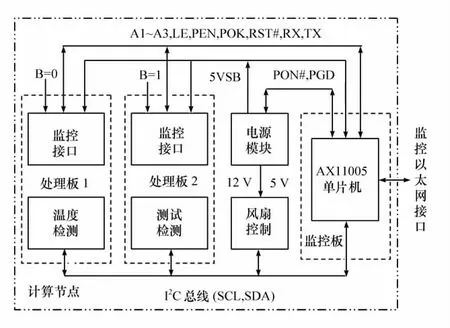

2.3 监控管理方案

该实验平台采用了远程分布式实时监控方案,如图4所示,前置管理服务器通过百兆网络与底板的控制单片机AX11015通信,完成对整个系统的管理。其监控网络由I2C 总线、UART 总线和若干控制总线组成,控制AX11015单片机可根据系统负载状况,独立关闭处理单元或者计算节点,以及自动调节散热风扇的转速,或通过串口获取处理器的运行状态,通过UART 转TCP/IP机制发送到远程服务器上。

图4 系统监控管理方案

3 基于该实验平台的教学思路

采用该实验平台实施并行体系结构相关课程的教学,有利于解决现在各课程独立进行教学和实验时存在的问题。传统教学的各门课程教学和实验内容各自独立,相互之间缺少衔接性,学生在学习过程中无法建立系统的概念,而且现有的实验设备缺少灵活性,无法跟上体系结构的实际发展,不能真实地提供不同并行体系结构和互连拓扑结构,而且很多实验仅通过仿真软件实现,实验方式限制了学生的兴趣和创造性。另外,不同课程总共需要的实验设备和PC机型号相对较多,实验室管理困难,维护成本较高。采用统一并行体系结构实验平台则能有效地解决这些问题。

深圳大学面向本科教学的并行体系结构系列课程主要有4门:并行体系结构、并行算法设计、并行数值算法以及并行程序设计和实践。在引进该实验平台后,采取了“统一实验教学”的思路,系列课程设定统一的教学目的,各课程的教学内容按总体目的分工划分,但相对独立,实验内容统一在该实验平台上完成,并保证个课程实验内容之间的衔接性。这样学生在实验时可以快速上手,充分激发学生学习并行体系结构和并行计算的积极性,缩小理论教学和实际应用能力之间的差距。

深圳大学设定的并行体系结构系列课程的统一教学目的为:系列课程以并行体系结构和并行计算为主题,要求讲授并行计算的硬件平台(当代并行计算机系统及其结构模型)、软件支撑(并行程序设计)和理论基础(并行算法的设计和并行数值算法)。在内容组织上,强调并行机结构、并行算法和并行编程为一体,着重讨论并行算法的设计及其实现,并力图反映本学科的最新成就和发展趋势,体现并行机硬件和软件相结合、并行算法和并行编程相结合的思想。在教学过程中采用统一的并行教学实验平台,各课程统一安排足够数量的实践内容,以巩固和加深学生对并行算法理论、设计技术、分析方法和具体实现等各个环节的衔接性和整体理解。

根据系列课程的总体要求,具体课程总体实验教学的总体要求如下:

(1)并行体系结构:通过该实验平台让学生熟悉4种以上的主流并行计算平台,包括共享存储的多处理机(SMP)、分布存储的多计算机(CC-NUMA)、目前流行的PC机群结构以及MPP并行结构,实现不同的互连拓扑结构并进行性能测试。要求学生能够使用上述几种并行计算平台所提供的硬/软件环境及工具来开展自己的实验工作。

(2)并行程序设计和实践:在该实验平台上熟悉Linux操作系统和并行编程环境,掌握至少2种并行程序设计语言标准,即分布存储的MPI和共享存储的OpenMP。另外,对面向大型科学和工程计算的HPF(高性能Fortran)也应尽量了解和熟悉。

(3)并行算法设计:选择典型的非数值并行算法,使用并行程序设计和实践用的并行编程语言标准,在不同的并行计算平台上编程调试、分析和运行它们,要求通过不同特点的算法让学生体会不同的并行计算平台的优劣。

(4)并行数值算法:选择典型的数值并行算法,使用并行程序设计和实践用的并行编程语言标准,在不同的并行计算平台上编程调试、分析和运行它们,要求通过不同特点的数值算法让学生体会不同的并行计算平台的优劣。

这样,通过该实验平台,相关课程的教学和实验具有一定的衔接性和继承性,使学生能在统一规划下逐步掌握底层硬件和系统结构、基础并行软件平台、并行应用开发的全过程。

4 小结

统一并行体系结构实验平台的研制成功,将给高校计算机专业并行体系结构系列课程的教学提供一个新的思路。统一并行体系结构实验平台能保证系列课程的实验内容具有良好的衔接性,充分提高学生的实验兴趣和实验的积极性,对进一步深化相关课程的教学改革、提高课程的教学水平和教学质量、促进课程的建设与发展具有重要意义。

(

)

[1]陈国良,孙广中,徐云,等.并行计算的一体化研究现状与发展趋势[J].科学通报,2009,54(8):1043-1049.

[2]张俊霞,张焕杰,李会民.基于龙芯2F的国产万亿次高性能计算机KD-50-I的研制[J].中国科学技术大学学报,2008,38(1):105-108.

[3]张俊霞,李春生,张焕杰.KD-50-I-E:一台增强型高性能计算机[J].中国科学技术大学学报,2009,39(8):894-896.

[4]陈国良,蔡晔,罗秋明.国产个人高性能计算机系统研制[J].深圳大学学报,2011,28(6):471-477.

[5]孙凝晖,陈国良.PHPC:一种普及型高性能计算机[J].中国科学技术大学学报,2008,38(7):745-752.

[6]全成斌,管晓培,李山山,等.计算机硬件实验统一平台设计[J].计算机教育,2008(18):3-5.

[7]汤志忠.清华“计算机专业实践”课程的创新与实践[J].计算机教育,2006(7):7-9.

[8]Hu W,Wang J,Gao X,et al.Godson-3:A Scalable Multicore RISC Processor with x86Emulation[J].IEEE Micro,2009(29):17-29.

[9]HyperTransportTM I/O Link Specification Revision 3.0[S].USA:HyperTransport Technology Consortium,2006.

[10]郑纬民,汤志忠.计算机系统结构[M].北京:清华大学出版社,2001.

[11]陈国良.并行计算:结构·算法·编程[M].北京:高等教育出版社,2003.

[12]陈国良.并行算法的设计与分析[M].修订版.北京:高等教育出版社,2003.

[13]陈国良.并行计算机体系结构[M].北京:高等教育出版社,2003.

[14]陈国良.并行算法实践[M].北京:高等教育出版社,2003.