时域反射仪高精度步进延迟系统设计

沈绍祥,刘丽华,方广有,王 礼

1)中国科学院电子学研究所,北京100190;2)中国科学院大学 电子电气与通信工程学院,北京100049;3)中国建筑科学研究院防火所,北京100013

时域反射仪(time domain reflectometry,TDR)是一种通过观测电磁波在介质中的传播来确定待测介质电磁性质的探测仪器. 由于电磁波在不同介质中的传播速度与介质的介电常数有关,工程上运用TDR 获取电磁波在介质中的反射信号来反演被测介质参数. TDR 系统的发射信号具备快速上升沿及准周期特性,针对该形式的高频准周期重复信号采样,一般在工程实践中采用等效采样的方法. 它是利用信号的准周期性,在时域上通过采样保持将模拟信号展宽为低频信号[1],然后再由低速模/数转换器(analogy to digital converter,ADC)对该低频信号采集. 相对实时采样,该采样方式为欠采样技术. 等效采样虽降低了采样率,避开了实时采样对ADC 转换速率的极高要求,但也带来了如何实现高带宽的采样门电路及如何实现采样门开启的高精度步进延迟脉冲的难题.

在等效采样方法中,获得步进延迟脉冲的方法有快慢斜波比较法、延迟芯片法、差频法和特殊工艺法. 快慢斜波通过快慢斜波电压在比较器上进行比较使比较器翻转输出延迟脉冲,其存在电压翻转区域,而非理想的快慢斜波交点处输出. 这是因为比较器本身非理想运放,开环增益非无穷大,存在线性区. 此外,快慢斜波电压本身噪音较大,当所需单位步进延迟量小于10 ps 时,该方案难以奏效.而延迟芯片法,要获得小于10 ps 的步进延迟时,这类器件种类有限,价格昂贵,且数字可编程级数不足. 当实现较大延时量时,需多个芯片级联[2],通常输出信号的电平类型较复杂. 另外,某些TDC测量应用则利用了器件固有延迟来实现延迟调节,其精度可达几皮秒到几十皮秒[3-4],该方法可认为是特殊工艺法,但只能获得固定范围延迟,如采用现场可编程门阵列 (field programndde gatearray,FPGA)实现时,FPGA 结构会严重影响其实现精度,不同布线算法也会直接影响结果的准确性[5-6].差频法利用两个晶振具有极小频率相位差来获得皮秒量级延迟,该方法不易控制. 实际应用中常采用DDS 输出不同频差信号,这也带来小步进难以实现的问题,主要是DDS 波形码字需要经过DAC 刷出,而过小的相位差被DAC 有限位数截断后,很难达到步进小于10 ps 的要求[7]. 为此,本研究结合TDR 系统的应用要求,提出一种有效的斜坡式步进延迟设计方案,利用微波三极管的开关特性构成近似比较器,结合恒流源和充放电电容共同组成步进延迟电路,实现单位步进延迟量为8 ps,测试效果良好,满足应用指标要求[8].

1 斜坡式步进延迟原理

图1[1]为快慢斜波比较法实现步进延迟原理示意图. 该方法基本过程为:快斜波电路受控于触发脉冲,并产生与触发脉冲相同重复频率的快斜波信号. 慢斜波电路在首个触发脉冲到来时被触发形成慢斜波信号,并在整个步进延迟时间窗内以一定斜率渐升. 快斜波电压与慢斜波电压在比较器上进行比较,当快斜波电压幅度达到慢斜波电压幅度时,比较器翻转并输出步进延迟脉冲信号. 随着慢斜波信号幅度增大,输出的步进延迟脉冲信号相对触发脉冲 的 延 迟时 间 越 大[2,8]. ADI 公 司 延 迟 芯 片AD9501 构成步进延迟原理就是这种方法的代表[6].

图1 快慢斜波比较步进延迟原理[1]Fig.1 Principle of fast slow comparison[1]

TDR 步进延迟系统采用斜坡式步进延迟原理设计,其构成框图及原理图[10]如图2.

图2 斜坡式步进延迟原理Fig.2 Ramp step-delay method

斜坡式步进延迟框图由数/模转换器(digital to analogy converter,DAC)、高速比较器、恒流源、充电电容C、等效开关K 及开关二极管D 组成. 斜坡式步进延迟工作过程为:由1 个启动延时脉冲触发K,当触发脉冲处于高电平时,K 闭合,C 通过D 对地放电;当触发脉冲处于低电平时,K 断开,恒流源对C 充电. 电容充电电压与DAC 的输出电平通过比较器进行比较,当电容电压达到DAC 的输出电平时,比较器输出发生翻转,获得步进延迟脉冲输出. 相对启动延时的触发脉冲而言,比较器输出脉冲产生步进延迟.

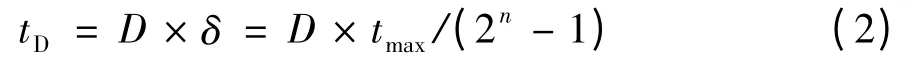

设最大可编程延迟时间为tmax,DAC 数字量为n bit,则单位步进延迟量δ 为

当DAC 数字量为D 时,步进延迟量

其中, × 表示乘积运算;tmax= (C/I)× (Vmax-Vmin);C 为电容电量;I 为恒流源电流.

步进延迟最大时间tmax由Vmax决定,Vmin确定步进延迟的起始点. 电容C 的充电过程是非线性的,故可编程延迟时间的线性范围tl小于编程延迟时间tprg. 电容的充电斜率与δ 呈反比.

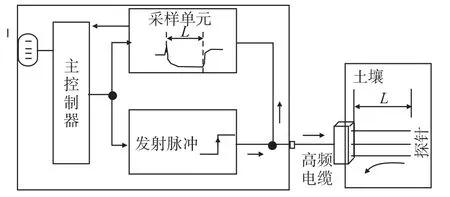

2 TDR 测量原理

图3 为TDR 系统的基本测试原理框图. 由图3可见,发射脉冲产生的快沿阶跃脉冲经电缆传输至探针,探针前端开路,脉冲信号在探针前端开路处发生全反射. 采样单元记录脉冲幅度随时间变化的波形,通过计算脉冲在探针上的传输时间,可推算出不同介质的介电常数. 参数的计算方法详见文献[11-12],本研究用式(3)计算相对介电常数

其中,εr为相对介电常数;L 为探针长度;t 为电磁波在探针上传播时间.

图3 TDR 测试原理框图Fig.3 Test principle diagram of TDR

3 步进延迟系统设计

3.1 电路设计

本研究基于斜坡式步进延迟电路原理,介绍的步进延迟电路由基于微波三极管开关特性的近似比较器、恒流源、充电电容、等效开关、等效DAC和反向器整形共同构成,电路见图4. 图中“❶”表示电路节点标号1,对应的节点电压为V(1),其他节点电压依次定义为V(n)(n = 2,3,…,13).

图4 步进延迟电路图Fig.4 Circuit of step delay system

步进延迟电路中Q5与D3构成等效开关,Q3与D4构成恒流源,充电电容C3,微波三极管Q2和V3等效为DAC,pulse 为开关脉冲信号源,Q6与Q7形成整形反相器. 步进延迟电路的工作过程为:

1)设V3输出电压V0,使节点9 电压为V(9)=V0- VD1.

2)pulse 以某固定频率输出开关脉冲信号,占空比为95%.

3)当开关脉冲信号为高电平时,等效开关开启,节点2 的电压为V(2),D2的压降为VD2,此时恒流源不对C3充电. 而Q2的Vbe= V(2)-VD2-V(9),故等效开关开启时,需保证Vbe大于Q2的导通压降,使Q2导通. Q2的输出为某一固定电压.

4)当开关脉冲信号为低电平时,等效开关关闭,为提高关断速度,利用肖特基二极管D3加速关断. 而关闭前,C3先放电,当等效开关彻底关闭时,恒流源向C3充电. 随着C3不断被充电,V(2)增大,一旦Vbe大于Q2的导通压降,Q2导通,此时Q2的集电极输出步进脉冲.

5)依靠Q1、D2和D3构成Q2回流通路,使Q2导通后,随着V(2)继续增大,V(9)的电压随之增大,直到C3充电饱和. 当开关脉冲信号高电平再次到来时,V(2)和V(9)降至初始值. 所以,当输入不同V0时,可获得不同延迟时间.

3.2 电容充电线性区及步进延迟量分析

在上述电路中,由于C3充电过程是非线性的,在充电接近饱和时,会逐渐呈非线性,使对应等效DAC 某些区域数字量所产生的步进延迟量不是均匀变化. 因此,需确定C3充电的近似线性区及真实单位步进延迟量,保证在该区域中,等效DAC 单位数字量变化所产生的单位步进延迟量变化相同.

设C3的初始电压为Um,则充电过程中C3电压u(t)随时间变化规律为

其中,τ 为时间常量. 将u(t)在某点t0处展开为泰勒级数,得

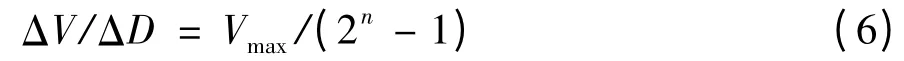

由式(5)可知,u(t)的变化趋势主要由第1 项直流分量和第2 项1 阶导数分量决定,而1 阶导数项表示t0处的斜率,故可采用切线法[13]确定线性区.如图5,V(9)曲线所判定的线性区为ab 段. 仿真可获得ta、Va、tb和Vb,且ΔV = Vb-Va、Δt = tb-ta.设DAC 为n b,则

由式(6)可推导出

其中,Vmax为DAC 的满量程输出电压值;ΔD 为对应ΔV 下的数字量. 因此,单位步进延迟量为

图5 C3 充电线性区判定Fig.5 Judgment of C3 charging range of linearity

3.3 电路参数仿真

仿真电路中的微波三极管Q2选用BFP620,D1、D2和D3选用HSMS281x. 在仿真过程中建立器件的Spice 模型,采用Pspice 进行电路仿真,C3=220 pF. 当V3(等效DAC 输出电压)分别取0.7、1.7 、2.5 和3.0 V 时,仿真结果如图6.

仿真结果表明,V3越大,则V(9)输出电平位置越高,步进延迟脉冲信号V(15)输出延迟越大. 所以,通过改变V3输出电压值,可以控制步进延迟脉冲信号输出延迟时间. 随着V3输出不同电压值,使V(9)电压不同,当C3充电电压V(2)达到能使Q2导通的值时,步进延迟脉冲V(15)输出,随后V(9)与V(2)同趋势变化.

设等效DAC 为14 b,系统供电VCC=5 V,取Vmax=3 V,由仿真分析可得Δt =32.097 ns,ΔV =2.446 V,代入式(7)得ΔD =4 012,故由式(8)可计算电路的单位步进延迟量δ=8 ps.

4 实验结果分析

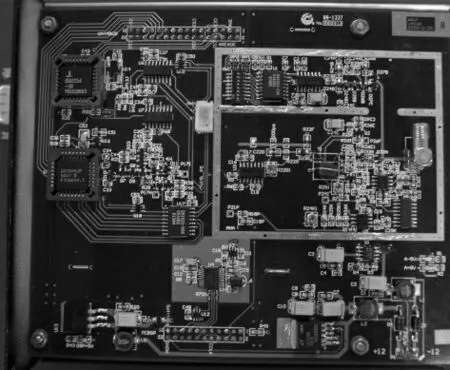

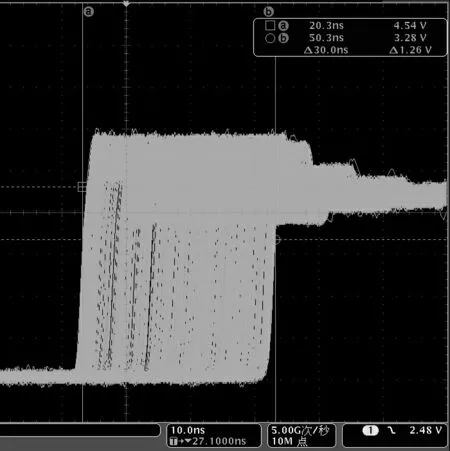

将该步进延迟电路应用于时域反射仪TDR-I中,电路实物图见图7. DAC 采用AD7840JP. 实际电路中的充电电容线性区是确定的. 测试条设备采用具备余辉扫描功能的1 GHz 以上带宽的实时示波器,可实时修改DAC 的数字量. 测试时,DAC的数字量以步进N 从0 增至8 191 b,N 一般取1 000,然后记录每次步进延迟量ti(i = 1,2,3,…,8).

当ti= ti+1时,认为ti和ti+1区域为电容线性区的一部分;当ti≠ti+1且ti= ti-1时,说明ti+1包含非线性区,需在tj中进一步测量非线性区的起始位置,可进一步细化测量ti+1域中的N,由此确定该步进延迟电路的线性区. 在自行研制的时域反射仪TDR-I 中,步进延迟线性区大小为30 ns,单位步进延迟约8 ps. 步进延迟线性区测试结果如图8.

表1 为采用本研究设计的步进延迟系统自研时域反射仪TDR-I 与Cambell 公司的TDR100[14]对壤土和砂质壤土的测试结果,采用相同长度的探针来测量样本湿度递增变化,结果取3 次平均. 由表1可见,所测介电常数与TDR100 的计算结果接近[15]. 可见,本研究设计为步进延迟电路能实现步进精度约8 ps,适合高精度等效采样系统.

图6 V(1)、V(2)、V(13)、V(15)、V(9)仿真曲线Fig.6 Simulation results of V(1),V(2),V(13),V(15),V(9)

图7 时域反射仪硬件电路Fig.7 Hardware circuit of TDR

图8 步进延迟量测试结果Fig.8 Test results of step delay range

表1 TDR-I 和TDR 100 介电常数测试结果Table 1 Measured permittivity by TDR-I and TDR 100

结 语

本研究设计了可获得8 ps 的单位步进延迟量的时域反射仪高精度步进延迟系统,并分析其工作原理. 若要达到更高的步进精度,如小于5 ps,只需调整充电电容值,选用高精度的电容或提高DAC分辨率. 一般电路获得的线性步进延迟时窗不是很大,为获得更大的使用时窗,可与硅延迟芯片,如DS1023-500[16]级联,进行时窗拓展[17]. 在时域反射仪TDR-I 中采用本文设计的步进延迟电路,可大幅提高系统稳定性和采样准确度,有益于工程应用.

/ References:

[1]Su Hongqi. The Research on Data Acquisition Method and System of Geological Radar Signals [D]. Beijing:China University of Mining and Technology(Beijing),2004.(in Chinese)苏红旗. 地质雷达信号数据采集方法及系统研究[D]. 北京:中国矿业大学(北京),2004.

[2]Gan Lu,Gan Liangcai,Tian Mao,et al. Step-sampling system of high resolution ground penetrating radar [J].Chinese Journal of Radio Science,2008,23(3):555-559.(in Chinese)甘 露,甘良才,田 茂,等. 高分辨率探地雷达步进延迟系统的研究与实现[J]. 电波科学学报,2008,23(3):555-559.

[3]Lukas P,Joergen C. A flexible 5 ps bin-width timing core for next generation high-energy-physics time-to-digital converter applications [C]// The 8th Conference on Ph.D.Research in Microelectronics and Electronics (PRIME).Aachen (Germany):[s.n.],2012:179-182.

[4]Kim Y H,Yu W S,Cho S H. A 7 bit,3.75 ps resolution two-step time-to-digital converter in 65 nm CMOS using pulse-train time amplifier [J]. IEEE Journal of Solid-State Circuits,2013,48(4):1009-1016.

[5]Chen Liang,Li Yan,Li Ming,et al. Implementation and application of navigated place and route for an SRAMbased FPGA [J]. Journal of Shenzhen University Science and Engineering,2012,29(3):217-223. (in Chinese)陈 亮,李 艳,李 明,等. 基于SRAM 的FPGA导航布局布线方法实现与应用[J]. 深圳大学学报理工版,2012,29(3):217-223.

[6]Zhang Feng,Li Yan,Han Xiaowei,et al. Design and implementation of an integrated multi-level FPGA design system [J]. Journal of Shenzhen University Science and Engineering,2012 ,29(5):377-385. (in Chinese)张 峰,李 艳,韩小炜,等. 用于FPGA 的多层次集成设计系统的设计与实现[J]. 深圳大学学报理工版,2012 ,29(5):377-385.

[7]Huang Chao,Ren Lixiang,Mao Erke. Desigh of a time delayed receiver local oscillator in stepped-frequency radar[C]// IET International Radar Conference. Guilin (China):[s.n.],2009:1-4.

[8]Shen Shaoxiang,Feng Wei,Ji Yicai,et al. Hardware design of a portable time domain reflectometry [J]. Application of Electronic Technique,2010,36(1):75-78.(in Chinese)沈绍祥,冯 炜,纪奕才,等. 便携式时域反射仪硬件系统设计[J]. 电子技术应用,2010,36(1):75-78.

[9]Analog Device Inc. Digitally Programmable Delay Generator AD9501 [M/OL]. Norwood (USA):ADI,2003:4-11. [2013-03-01]. http://web. hep. uiuc. edu/cleo/trig3/boards/TILE/vme021d_data_sheets/ad9501.pdf.

[10]Su Hongqi,Yang Feng,Ma Kai,et al. Research on high-accuracy programmable timer used in acquiring UWB signals [J]. Applied Geophysics,2005,2(2):127-130.

[11]Robinson D A,Jones S B,Wraith J M,et al. A review of advances in dielectric and electrical conductivity measurement in soils using time domain reflectometry [J].Vadose Zone Journal,2003,2(4):444-475.

[12]Huisman J A,Lin C P,Weihermüller L,et al. Accuracy of Bulk electrical conductivity measurements with time domain reflectometry [J]. Vadose Zone Journal,2008,7(2):426-433.

[13]Shen Shaoxiang,Feng Wei,Ji Yicai,et al. The implementation of and determination of Traveling Time of TDR waveform with Tangnet method [J]. Science Technology and Engineering,2009,9(24):7537-7581. (in Chinese)沈绍祥,冯 炜,纪奕才,等. TDR 波形传输时间的切线法判定与实现[J]. 科学技术与工程,2009,9(24):7537-7581.

[14] Campell Scientific Inc. TDR100 Instruction Manual[M/OL]. Logan (USA):Campell Scientific Inc,2006:5-95. [2013-03-01]. http:// s.campbellsci.com/documents/us/manuals/tdr100.pdf.

[15]Feng Wei,Ji Yicai,Shen Shaoxiang,et al. Water ratio and electrical conductivity measurement in soil with TDR[J]. Transactions of the Chinese Society for Agricultural Machinery,2009,40(5):59-63.(in Chinese)冯 炜,纪奕才,沈绍祥,等. 测试土壤含水率和电导率的时域反射仪系统[J]. 农业机械学报,2009,40(5):59-63.

[16]Maxiam Inc. 8-bit Programmable Timing Element [M/OL]. Beijing:Maxiam Inc,2003:1-16. (2001-07-30)[2013-03-01].http:// china.maximintegrated.com/datasheet/index.mvp/id/2608.

[17]Zhang Kang,Zhou Bin,Fang Guangyou. Miniaturized design of impulse ground penetrating radar host control system [J]. Control & Automation,2007,23(35):211-213.(in Chinese)张 康,周 斌,方广有. 无载频脉冲探地雷达主控系统小型化设计[J]. 微计算机信息,2007,23(35):211-213.