一种高性能的数字预失真系统硬件设计与实现

李幸霖,曾志斌

(中国传媒大学广播电视数字化教育部工程研究中心,北京100024)

一种高性能的数字预失真系统硬件设计与实现

李幸霖,曾志斌

(中国传媒大学广播电视数字化教育部工程研究中心,北京100024)

针对高频和宽带数字广播信号,设计了一种基于FPGA的数字预失真硬件系统,设计选用了高性能的数字和模拟器件,并重点考虑了高速硬件系统的电磁兼容和信号完整性的电路设计。工程实测证明了本预失真硬件系统的高性能,稳定性和可靠性。

功率放大器;数字预失真;电磁兼容;信号完整性

1 背景介绍

线性化技术是现代数字广播发射系统的主流的线性化技术之一,对降低发射机功率放大器的幅相失真,提高功率效率频具有重要意义。功率放大器是现代通信系统中不可缺少的重要组件,其固有的非线性特性会导致信号失真与邻道干扰。目前普通射频功率放大器的效率仅为 10%左右,不仅造成了大量的资源浪费,并对邻道通信带来严重干扰。

早期的线性化技术主要从功率放大器器件本身的物理特性出发,采用模拟方式直接对射频电路进行补偿,因模拟器件本身的其可靠性较差,因而其性能有限。预失真技术是现代数字广播发射系统的主流的线性化技术之一,其优点是:高度数字化、算法灵活和稳定可靠,迎合了今后的发展方向[1]。

本文介绍一种新型的数字预失真系统硬件设计,应用赛灵思(Xilinx)公司的Vertex-5系列FPGA芯片完成预失真算法。FPGA具有可编程能力,因此用户能够灵活地优化解决方案,并能够适应数据转换器和功率晶体管技术的未来发展。除此之外,系统设计了高可靠性和低附加失真的下变频电路,并选用高性能模数和数模转换芯片等外围器件,共同组成了性能稳定,指标优良的数字预失真硬件系统。

2 数字预失真技术原理

预失真是人为地加入与功放系统非线性特性(幅度和相位)相反的信号处理模块(预失真器),进行非线性补偿,从而达到功放输出信号无失真传输的目的。实现过程如图1所示。

图1 预失真原理示意

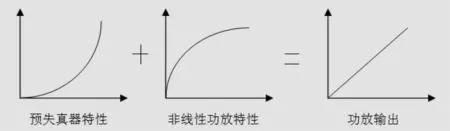

预失真处理在数字域中完成,数字预失真的输入信号是正交的基带数字IQ信号,在基带经预失真器中完成预失真处理[2],再上变频到射频,如图2中所示。

图2 基带数字预失真框图

3 数字预失真硬件设计

自适应数字预失真电路板(AdaptDPD)主要由信号接收、信号处理和信号发射三部分构成。本设计适用DAB,DRM和CMMB等多种数字广播标准,本预失真电路主要针对CMMB信号进行处理和验证。

3.1 数字预失真原理图

预失真板硬件电路主要混频器,数模转换器,FPGA,模数转换器,正交调制器以及频率合成器等主要部分组成。其中混频器完成射频信号的下变频至中频。FPGA将数字中频信号解调至数字基带信号,并完成预失真算法,并输出预失真处理后的源基带信号,和频率合成器输出的射频载波一起馈送至正交调制器,上变频到射频。电路板的框图如图3所示。

图3 数字预失真原理框图

在电路板的PCB设计过程中,根据高频电路设计原则和EMC及信号完整性的考虑,在布局布线方面做了重点设计考虑。

1.布局:对多层PCB板进行布线层、电源层和地层的合理排序,以及元器件合理布局,如数字和模拟器件分开,最大程度降低电磁干扰。

2.布线:高速时钟线和高速信号线等关键走线必须做首要考虑。其走线的位置,长度,阻抗匹配都必须符合一定的设计原则,以确保信号的完整性。

3.2 反馈部分

本设计的重点在于:高可靠性和低附加失真的下变频电路,这是复杂的DPD闭环算法进行有效预失真参数提取的前提,尤其对于频率达G赫兹量级的射频信号,要保证信号下变频至基带并尽可能降低附加失真。

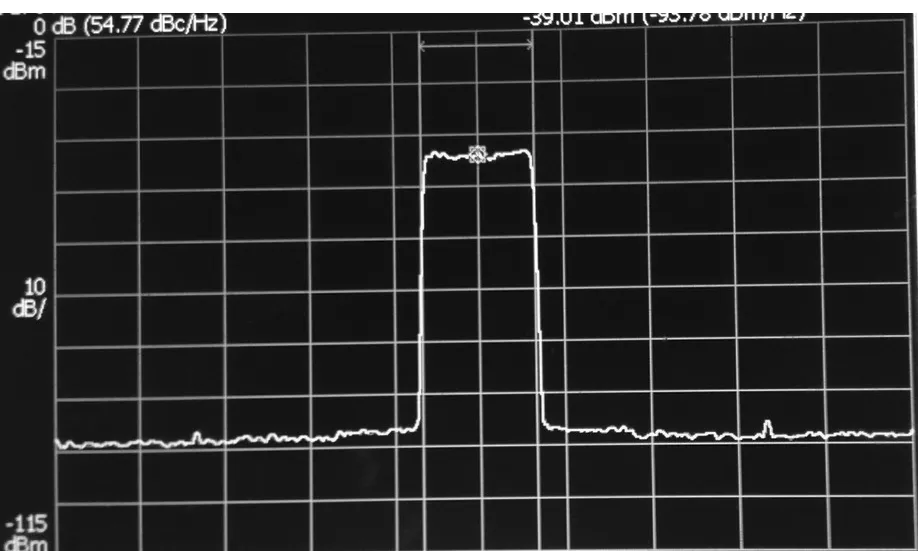

混频器是在下变频电路中起着至关重要的作用。数字预失真电路板接收RF信号后进入混频器。混频器选用高线性度双平衡无源混频器。本振信号选用集成VCO的宽带频率合成器芯片产生,以提供出色的相位噪声性能。用频谱仪测量相位噪声如图4所示,在1kHz相位噪声大约-95dBc/Hz,随着频率增加,相位噪声经过一段平缓的区域迅速下降,指标满足系统需要。

图4 本振信号的相位噪声

中频信号进入可变增益放大器,VGA芯片选用数字控、可变增益、高带宽放大器,可以提供精密增益控制、高IP3与低噪声系数[3]。

为避免模数转换后的信号混叠,下变频后的40MHz的中频信号须经巴特沃兹低通滤波器滤波。对8MHz带宽的CMMB信号,考虑到三阶和五阶互调,其带宽至少是原信号的5倍带宽,即40MHz。出于更高阶互调和对称性考虑,我们将滤波器截止频率设置为80MHz,频率响应如图5所示:

图5 低通滤波器频率响应

数模转换器采用12位宽,160MHz采样率的ADC芯片,并具有优异的动态性能,适合宽带载波和宽带系统。ADC芯片将模拟中频信号转换为数字中频信号馈送入FPGA[4],至此完成了高性能、低附加失真下变频工作。

4 测试结果

我们对本预失真系统的性能进行了工程实测,测试环境为:

1.带宽为8MHz的CMMB信号;

2.L波段的50瓦功率放大器;

3.工作频率1.472814GHz。

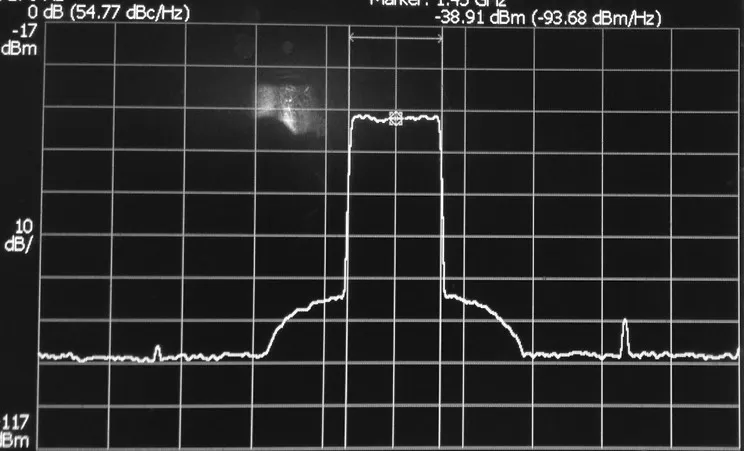

图6a和图6b分别是未经和经预失真处理的功率放大器输出的CMMB信号频谱。对比可知,其带肩比改善了约15dB,从侧面表明了本预失真硬件设计在电磁兼容和信号完整性方面的性能,达到了预期目标。

图6a 无预失真CMMB信号功率谱

图6b 有预失真CMMB信号功率谱

5 结论

本数字预失真硬件系统以FPGA为核心芯片,外围配搭高可靠性和低附加失真的下变频电路以及高性能模数和数模转换芯片。目前,本系统已应用到实际工程项目中,测试指标表明了系统的可靠性和稳定性。

[1]郭阳,唐友喜.高效射频功率放大器数字预失真关键技术研究[D].成都:电子科技大学,2011.

[2]许高明,刘太君.射频数字预失真器设计与实现[D].宁波:宁波大学,2009.

[3]Xilinx.MULTI-MODE RADIO TARGETED DESIGN PLATFORM[EB/OL].http://www.xilinx.com/publications/prad mktg/Radio-TDP-SeUSheet.pdf,2009.

[4]Analog Device.Mixed Signal Digital Pre-Distortion Evaluation Platform.Wireless Personal Communications[EB/OL].http://www.analog.com/static/imported-files/eval boards/MSDPD EvalBroard.pdf,2010.

AHigh-performanceHardwareDesignandImplementationforDigitalPredistortionSystem

LI Xing-lin,ZENG Zhi-bin

(ECDAV,Communication University of China,Beijing 100024,China)

This paper designs a digital predistortion hardware system based on FPGA for broadband and high-frequency radio signals.High performance digital and analog devices are selected for this predistortion hardware system,and furthermore,electromagnetic compatibility and signal integrity are carefully designed in its pcb design.Engineering measurements prove that this predistortion hardware system is of high performance,stability and reliability.

power amplifier;digital predistortion;hardware design;downconversion

2013-04-24

李幸霖(1988—),男(汉族),天津人,中国传媒大学硕士研究生.E-mail:lixinlin@cuc.edu.cn

TN492

A

1673-4793(2013)04-0058-04

(责任编辑:王谦)