多轴联动高速运动控制网络的设计与实现*

张建华 葛红宇 李宏胜 方 力

(南京工程学院自动化学院,江苏南京 211167)

网络化是运动控制、数控技术等领域的重要发展方向。结合商业化的CAN总线、485总线等技术,相关的研究人员与机构推出一系列的网络化运动控制器、数控系统网络等工业化产品[1-2]。近年来,以太网技术的飞速进步,使基于串行通信协议的运动控制网络受到业内各界的广泛重视,先后出现了SERCOSII、Powerlink、Profinet等专用运动控制网络协议。其硬件传输媒介主要采用RS-485、光纤、Fire Wire与以太网4种,各有自身独特的优势,同时也都拥有一定的市场份额[3-5]。其中Synqnet运动控制网络采用全双工传输模式,通信周期小于25 μs,双向传输速度可达200 Mb/s,突出的性能优势使其迅速得到相关专业厂商的认可,并迅速被市场采用[6]。

根据上述发展,本文在多轴联动数控网络研究中,参考商业化的Synqnet控制网络结构与协议并进行适当的简化、修订,同时结合数控系统的技术特点,基于大规模可编程逻辑器件FPGA,研究多轴联动高速运动控制网络的拓扑结构、传输协议、联动控制方法及其实现技术[7-9]。

1 网络结构设计

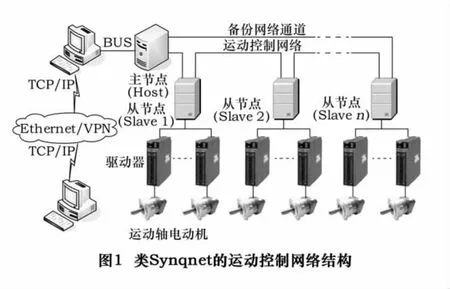

本文所用运动控制网络结构如图1,主控计算机在完成指令输入、译码、校验、刀具补偿后将得到的多轴运动控制指令直接通过局部总线传给主节点Host,再由主节点Host通过本文所设计的类Synqnet协议传至各从节点Slave。从节点不仅完成指令数据的接收、通信功能,还负责各运动轴的联动控制。Slave节点上,各运动轴的插补控制信号由运动控制器内带有类Synqnet协议的运动控制芯片实现。相对现有运动控制网络,图示的网络结构将节点上各运动轴的插补控制算法集成到节点控制中,因此节点上的各轴联动操作不需要额外的插补控制器;同时,节点间各轴的插补运动通过网络的高速数据传输保证。因而,该种网络结构易于实现多轴运动的强实时控制。

上述的控制网络中,主节点通过主控芯片接收CPU送来的并行数据,计算校验码,将二者转换为网络介质要求的四位数据,根据专用数据传输协议发送至类Synqnet网络。从节点利用运动控制芯片接收来自类Synqnet网络的数据,同时进行数据转换、校验,而后根据数据指令初始化运动参数,驱动插补控制模块,发出指令脉冲至相应驱动器。

2 主节点控制逻辑设计

本文的类Synqnet总线沿用商业以太网的双绞线与物理层接口PHY,同时设计专门的通讯协议与节点逻辑控制电路与芯片,以简化传输,提高效率。

2.1 主节点控制芯片的逻辑结构

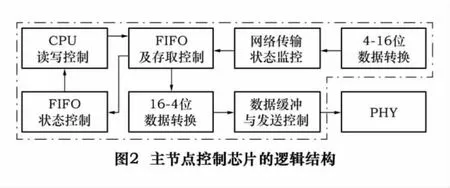

主节点的逻辑控制电路基本结构如图2,它主要完成数据发送及状态监控等功能,通过专门设计的专用节点控制芯片实现。整个控制芯片由CPU读写控制、FIFO、16-4位数据转换、FIFO状态监控,数据发送与发送状态监控等模块构成。

主控芯片通过CPU读写控制接收CPU的16位并行数据、计算16位循环冗余码,根据网络介质要求将其转换为四位数据,而后响应发送时钟TXC,将数据发至类Synqnet网络。从节点收到数据,进行串并转换、循环冗余校验,传输错误,向主节点发出重发请求,请求重发数据封包。

2.2 数据发送逻辑设计

2.2.1 数据格式

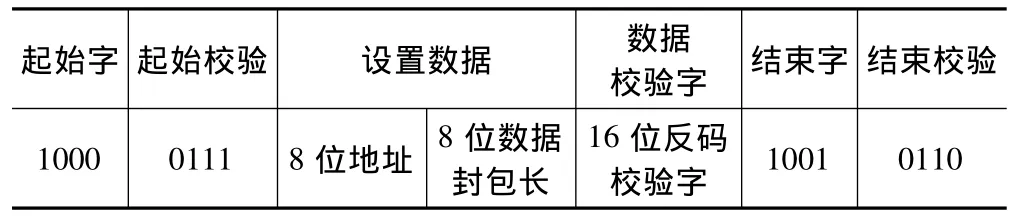

本文的数据传输过程分为参数设置与数据传输两个阶段,分别处理两类数据封包-设置封包与数据封包。设置封包的数据格式如表1,起始字为4位数据“1000”,结束字“1001”,校验采用取反校验,传送起始字、结束字、设置数据的同时,输出反码供校验。

表1 设置封包结构

数据封包的结构与设置封包类似,也包括起始字、数据与结束字3个段,且起始字、结束字与校验码均与设置封包相同,只是所传输的数据采用16位循环冗余校验。

2.2.2 发送时序逻辑设计

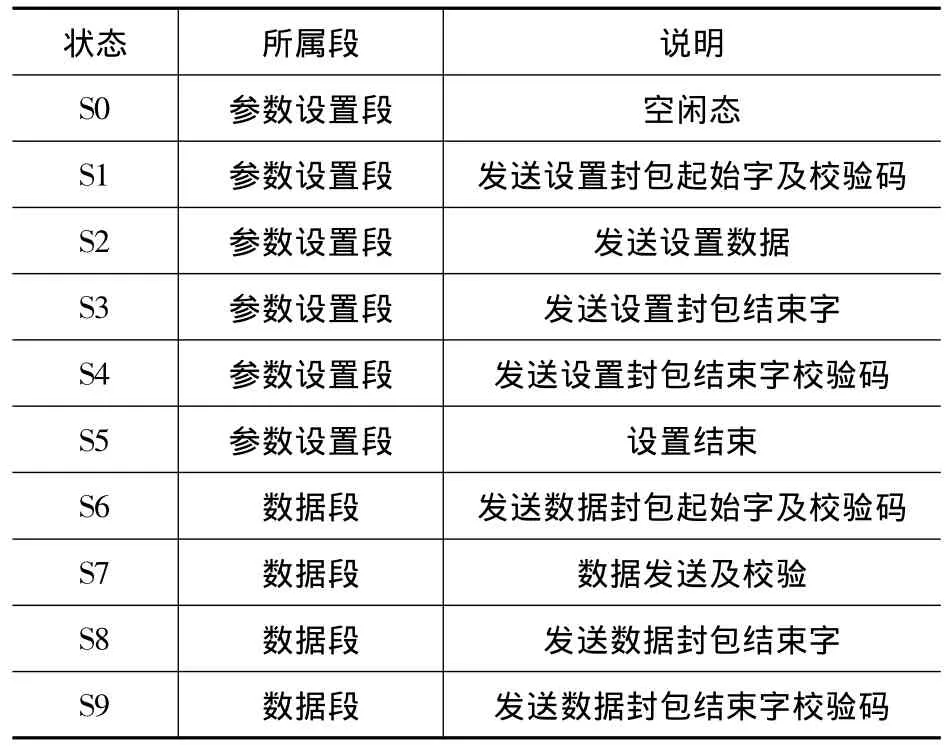

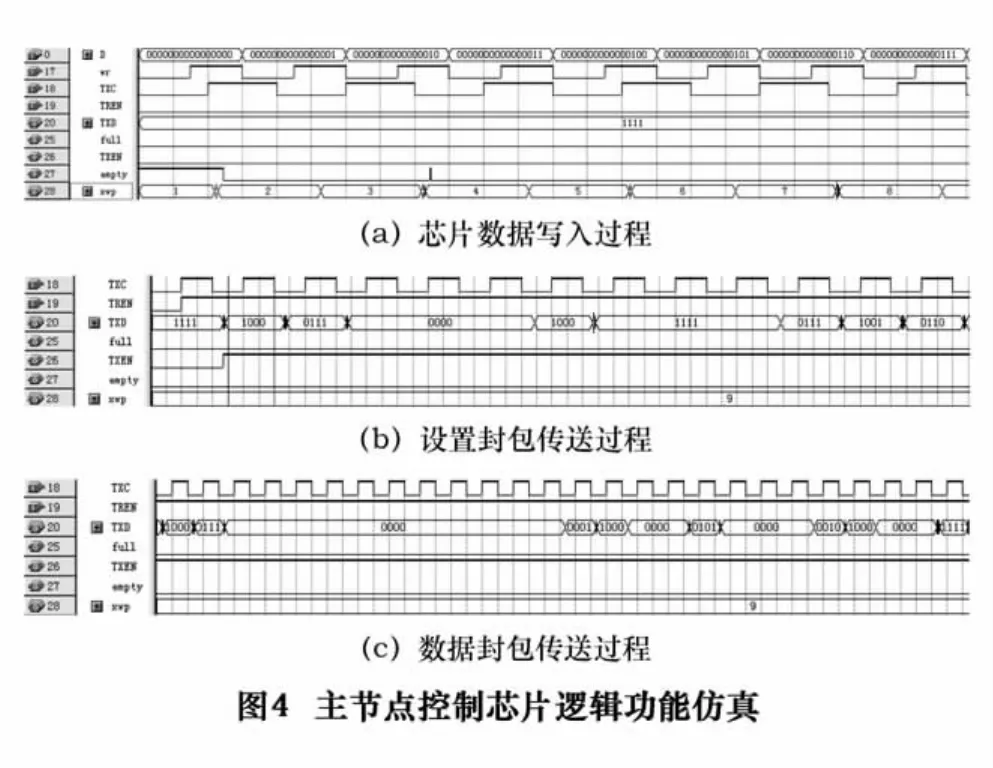

发送电路遵从IEEE802标准,响应发送时钟TXC发送数据。根据两类封包的数据格式,发送模块设置芯片的10个状态,分别对应设置封包与数据封包各数据的发送过程,如表2。

表2 发送过程控制芯片状态字

如果FIFO不空,主节点控制芯片根据FIFO读写指针计算待发数据长度(以字为单位),进入参数设置段,启动一次传送过程。而后,在发送时钟TXC下降沿上,控制芯片检测芯片状态与网络传输状态,若传输正常,根据状态依次送出起始字及校验码、设置数据及校验码、结束字及校验码,同时依次修改芯片的相应状态。发送过程中,检测到网络传输出错,芯片重置空闲状态S0,清出错标志,重复上述过程,重发设置封包。

数据传送段,控制芯片首先送出起始字与校验码,启动数据封包发送,校验无误,从FIFO中取一字(2字节)作为发送数据的高16位,同时计算16位循环冗余码作为发送数据的低16位,从高到低,依次从发送数据中截取4位,在TXC下降沿上送至TXD。数据发送中,接收端出错,芯片转状态S6,在下一个TXC降沿重发数据封包起始字“1000”,重新开始数据封包的传送。

数据发送结束,模块发送结束字“1001”及其校验码“0110”,完成整个数据封包的发送,实现一次完整的数据发送过程。

3 从节点控制逻辑设计

3.1 从节点控制芯片的逻辑结构

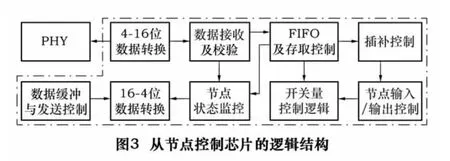

从节点控制电路的逻辑结构如图3,它主要完成数据接收、插补控制及节点开关控制等功能,通过专用的从节点控制芯片实现。

从节点控制芯片由数据转换、接收、校验、FIFO及存取控制、插补控制、节点输入/输出控制等模块构成。芯片接收来自运动控制网络的指令数据,而后进行16位转换与循环冗余码校验。接收数据出错,则置位通信出错标志位,同时向主控芯片发出重发请求。反之,数据接收无误,存入FIFO供插补控制或开关控制模块读取。取到轨迹控制指令,插补控制模块初始化运动参数,启动相应的圆弧或直线插补功能,送出指令脉冲给相应驱动器;取到开关控制指令,开关量控制逻辑通过节点输入/输出控制模块送出要求的开关量。

3.2 数据接收逻辑设计

与前述发送过程相对应,数据接收过程分为参数与数据接收两个阶段。根据两阶段网络所传输的数据及传输过程,接收电路同样设定电路的10个相应状态,如表3。

表3 数据接收过程控制芯片状态字

网络数据接收过程中,控制芯片响应接收时钟RXC的上升沿,从RXD接收数据,进行4-16位数据转换,取得数据及其校验码。空闲状态下,数据接收模块收到传送起始字及其校验码,根据FIFO的读写指针计算芯片中的的空余存储空间,进入参数设置段。而后,接收16位设置数据及校验码,校验无误,取设置数据高8位作为本次传送地址,低8位作为数据封包长(以字为单位),若取得本机地址,接收模块等待结束字及校验码,完成参数设置封包的接收;若非本机地址,接收电路恢复芯片空闲态S0,不作任何处理。校验出错,从节点错误标志位置‘1’,节点状态监控模块发送重传请求“1010”及校验码“0101”,请求发送端重发设置封包,从节点状态转空闲态S0。

参数设置段结束,接收电路等待数据封包起始字“1000”及校验码“0111”。而后响应RXC上升沿,按照先高后低的顺序,依次读入8组4位数,得到16位的数据及循环冗余码。校验无误,继续传输过程直至数据传送完成。与参数设置段类似,传输中数据出错,节点错误标志位置位,节点状态监控模块发送重传请求,节点状态转S6,等待数据封包起始字与校验码,重新开始数据段的传送。

数据传送结束,模块等待传送结束字“1001”及其校验码“0110”,收到后调整接收队列的读写指针,恢复各信号与寄存器,准备接收新的传送请求。

4 网络实现及仿真实验

4.1 节点控制芯片功能仿真实验

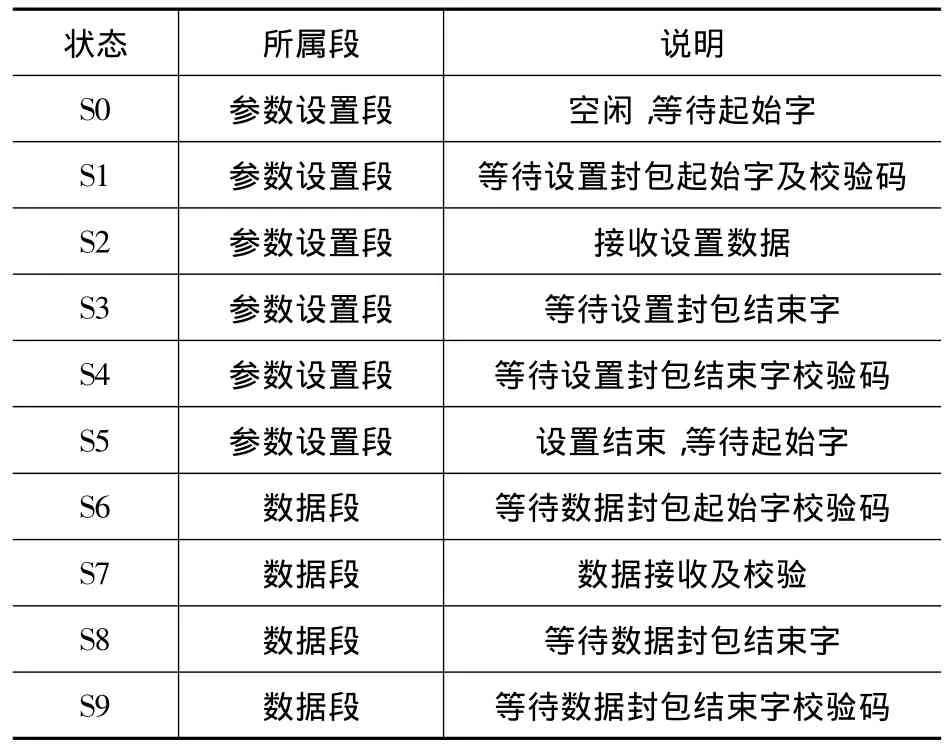

利用上述逻辑控制芯片的逻辑结构、数据格式、状态字以及数据传输过程,根据模块设计不同的VHDL进程Process,完成主/从控制芯片逻辑设计。主节点控制芯片逻辑功能仿真如图4所示。

图4a为数据写入过程,发送队列空标志empty迅速拉低。WR的升沿上,16位数据总线将数据0000H-0007H依次写入芯片FIFO,指针XWP递加。图4b的参数设置,发送允许TREN为高,TXD响应发送时钟TXC降沿,依次送出封包起始字“1000”与校验字“0111”,而后送出节点地址00H与数据封包长08H及其组合后的反码0FFF7H,最后送出结束字“1001”与校验码“0110”,结束参数设置段。

数据封包的发送如图4c,在TXC的降沿上,TXD依次送出起始字与校验码“1000”、“0111”,数据0000H及校验码0000H,数据0001H及16位循环冗余码8005H,数据0002H及冗余码800FH,输出顺序与图4a中写入的数据及顺序严格对应。

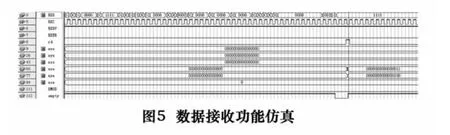

从节点控制芯片功能仿真如图5,图中所述为空间直线运动指令的传输。传输结束前接收队列空标志empty为1,实际上此时数据已经写入队列,为保证数据可靠性,此时不允许读取正在传送的数据封包。传输结束,队列空标志复位,读信号RD上升沿,接收队列中数据送出,图中运动模式XMOD=0,即直线运动,终点x坐标xxe=3(0011B),y坐标xye=4(0100B),z坐标xze=0,起点坐标全为0。

4.2 硬件实现

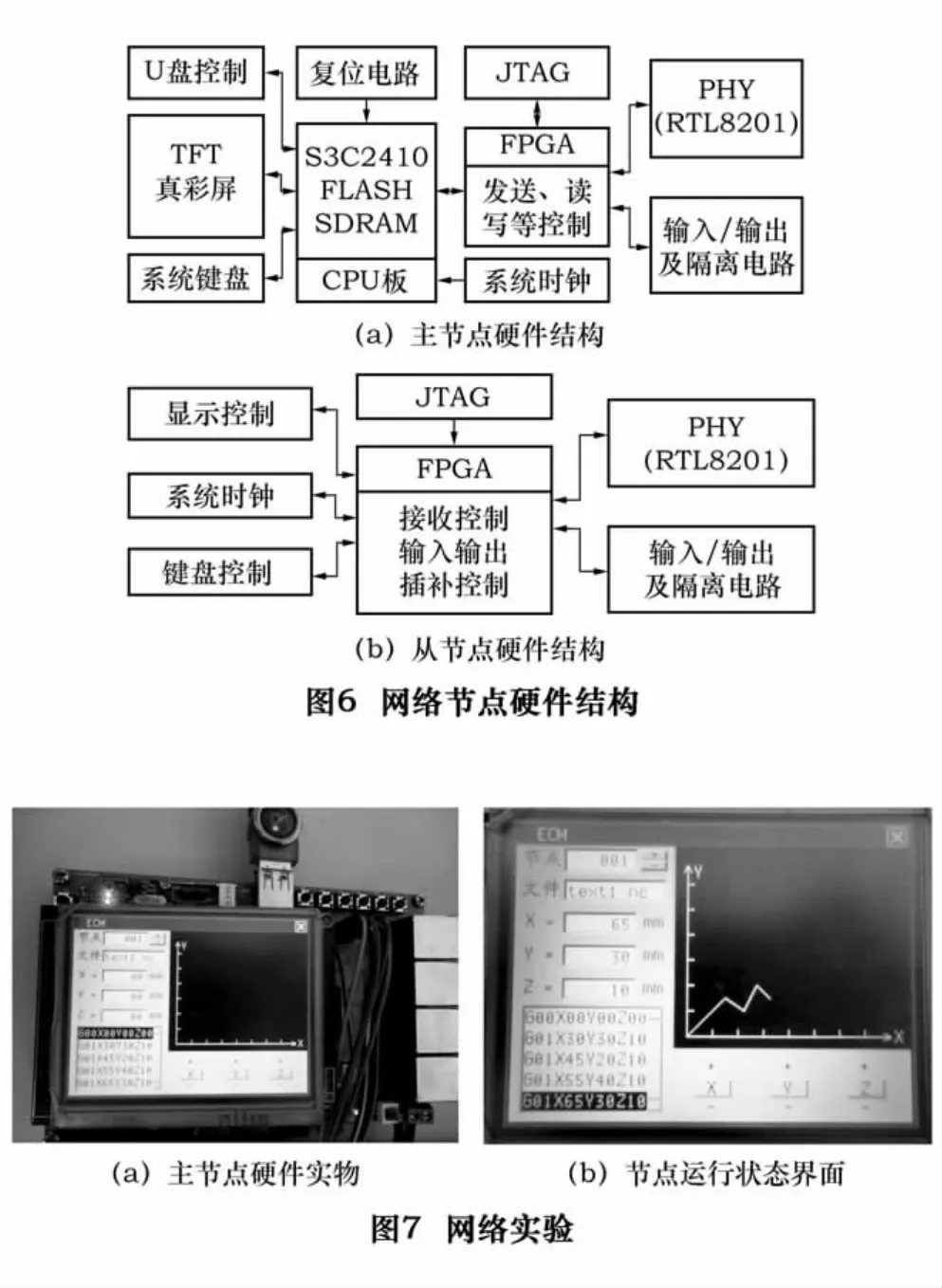

网络节点的硬件结构如图6所示。主节点硬件由CPU模块、主节点控制芯片(FPGA)、USB控制、系统键盘、物理层接口PHY及必要的IO电路构成。CPU采用集成的 CPU板,板上集成嵌入式处理器S3C2410、64 MB 的 SDRAM、2 MB 的 Nor Flash与 64 MB的Nand Flash,显示模块为商用的3.5英寸TFT真彩屏,PHY器件采用常用网络接口器件RTL8201。

上述硬件结构中,主节点处理器S3C2410通过U盘控制获取U盘中的指令数据,译码后将结果写入主节点控制芯片(FPGA)的FIFO,经过网络发至从节点,由从节点输出相应的插补脉冲、方向信号以及其他开关控制信号。网络硬件设计中采用两组收发器,形成冗余网络,增强网络的可靠性。主节点TFT模块显示主节点以及从节点的状态信息、正在运行的程序段等内容,节点选择、文件操作等的通过主节点键盘完成。

图7为网络实验的结果。根据图6描述的硬件结构,不考虑CPU模块,主/从节点具有相似的硬件结构,因而,本文的网络实验中从节点硬件与主节点的采用了同样的控制板,只是从节点上省去了CPU板和TFT模块。

5 结语

根据运动控制网络的发展,结合其在数控技术领域的应用,参考现有运动控制总线Synqnet网络,提出适于数控领域的一套类Synqnet网络结构及其实现技术,这种结构在节点上固化多轴联动控制逻辑,使每个运动控制网络节点成为一个独立的多轴运动控制器,节点上的多轴联动通过节点控制芯片实现,无需专门的CPU。同时,节点带有FIFO,能够满足联动控制的高实时性要求及网络化要求;结合数控技术,提出一整套的类Synqnet协议并提出其VHDL实现方法;在此基础上,采用硬件描述语言VHDL,完成了主节点逻辑控制芯片与具有多轴联动功能的从节点逻辑控制芯片设计。最后,利用商用的嵌入式S3C2410 CPU板,开发节点硬件对所提出的网络与通信协议进行了验证。

[1]刘丽松,殷苏民,林新华,等.基于CAN总线的开放式数控系统控制网络的设计[J].机床与液压,2007,35(2):164-166.

[2]舒志兵,张杰.基于CAN总线的网络化运动控制系统的研究[J].机械设计与制造,2008,30(1):181-183.

[3]许万,陈幼平,陈冰,等.基于实时以太网的多轴运动控制网络的研究[J].制造业自动化,2008,30(11):71-75.

[4]曹政,李磊,陈明宇.万兆以太网媒体访问控制层研究[J].计算机工程,2007,33(17):31-33.

[5]云利军,孙鹤旭,雷兆明,等.运动控制网络的研究现状及发展趋势[J].控制工程,2006,13(4):290-292.

[6]许俊,林水生.基于FPGA的以太网MII接口扩展设计与实现[J].电子设计应用,2005(5):110-113.

[7]云利军,孙鹤旭,雷兆明,等.基于SynqNet的网络化运动控制器研究[J].制造技术与机床,2006(2):40-43.

[8]叶懋,刘宇红,刘桥.CRC码的 FPGA实现[J].重庆工学院学报,2007,21(3):85-87.

[9]毕占坤,黄芝平,张羿猛,等.循环冗余校验分布式算法的理论推导及 FPGA 实现[J].兵工学报,2006,27(6):1121-1125.