高速图像采集系统的研制

张彦铎,陈 驰,于宝成,王春梅

(1.武汉工程大学计算机科学与工程学院,湖北 武汉 430074;2.智能机器人湖北省重点实验室,湖北 武汉 430074)

0 引 言

在图像采集系统中,处理的实时性是系统的核心所在.在传统的图像采集系统中,通常采用“摄像机-图像卡-计算机”的系统设计方式,在图像算法方面通过计算机软件实现,这在低速、单传感器的图像采集时能满足实际应用.然而在高速图像采集系统中,高速摄像机帧频通常能达到100~200帧/秒(Frame Per Second,以下简称:fps),基于多传感器的视觉测试系统中,受到传感器串行工作方式、输入输出端口(Input/Output,以下简称:I/O)传输速度以及全部算法仅能由软件实现等诸多方面的限制,使得系统实时性很难得到保证[1].因此,需要研制一种既能实时采集高速的图像数据,又能实时将采集得到的数据传递给计算机进行处理的专用的图像采集系统.

在本系统中,使用面向仪器系统的外设部件互连标准(Peripheral Component Interconnect,以下简称:PCI)扩展平台(PCI Extensions For Instrumentation,以下简称:PXI)将采集得到的低电压差分信号(Low-Voltage Differential Signaling,以下简称:LVDS)交给在LabVIEW编译环境实现的上位机进行处理.LVDS是为了克服传统电平方式传输带宽高、码率数据功耗大、抗电磁干扰能力弱而研制出的一种数字视频信号传输方式.采用LVDS输出接口的视频信号在差分印制电路板 (Printed Circuit Board,以下简称:PCB)线缆或平衡电缆上可以以几百兆位/秒(Million Bits Per Second,以下简称:Mbps)的速率传输.LVDS是采用极低的电压摆幅高速差动传输数据,它使得信号能在差分PCB线缆或平衡电缆上以几百Mbps的速率传输,可实现点对点与点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点.LVDS在对信号完整性、低抖动即共模特性要求较高的系统中得到越来越广泛的应用[2].LabVIEW是一种使用图像化编程方式的虚拟仪器软件开发环境.它采用数据流编程方式,以图表表示函数,以连线表示数据流,测试测量是LabVIEW最核心的应用领域,也是LabVIEW相比于其他编程语言的优势所在.LabVIEW广泛的被工业界、学术界和研究实验室所采用,视为一种标准的数据采集和仪器控制软件[3].

1 系统总体设计

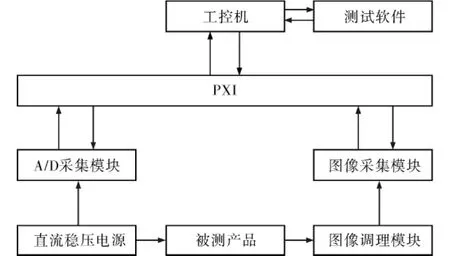

系统总体设计结构如图1所示,该测试系统以工控机为控制平台,内嵌有测试软件,通过测试软件控制整个系统的工作.被测产品通过直流稳压电源供电工作,数模(Analog/Digital,以下简称:A/D)采集模块用来采集被测产品工作时的电流值和电压值,并通过PXI总线将采集值上传到工控机的测试软件中,同时被测产品会发送带有特定协议的多路并行的LVDS信号,图像调理模块用来将采集得到的LVDS信号按照协议标准调理成为单路串行LVDS信号.图像采集模块采集调理LVDS信号,并通过PXI总线将采集的信号上传给工控机,供测试软件分析和处理.

图1 系统总体设计图Fig.1 Overall design of the system

2 硬件接口设计

2.1 硬件接口总体设计

在对标准化仪器或通用规范进行硬件接口设计时,通常采用的是购买市场上通用的标准设备,购买标准设备有稳定性好、精度高、扩展性强、节约开发周期和成本等诸多优点.在对非标准仪器进行接口设计时,则需根据设备自身接口定义自行开发研制.

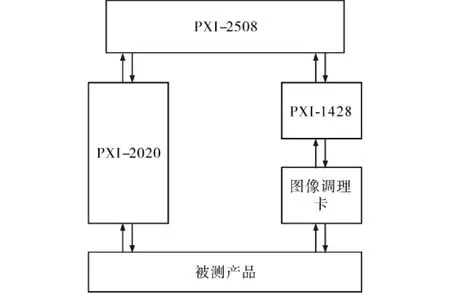

工控机采用的是凌华(ADLINK)的PXI-2508的机箱搭配PXI-3950的主控器,采用这种配置的工控机具有性能强、体积小、重量轻且方便携带等诸多优点,是一种专门为工业数据采集和自动化应用而量身定制的工控机配置.

A/D采集模块选用的是ADLINK PXI-2020采集卡,该采集卡提供8通道模拟输入通道,分辨率为16位,可以满足对被测产品电流电压实时监控的需求.

图像采集模块采用的NI PXI-1428图像采集卡进行图像信号采集,PXI-1428可通过LVDS接口接收数码摄像机或其它兼容图像采集设备的数据,可以捕捉高速、高分辨率的大型数字图像.该设备可以在40MHz采样时钟下以16位数据宽度采集数据,总采集速率高达80兆字节每秒(Million Byte Per Second,以下简称:MB/s).16兆字节(Million Byte,以下称简:MB)的板载内存为板卡上的图像提供了缓存,便于采集大型图像并持续进行实时采集.PXI-1428卡的缓存支持80 MB/s的数据输入和133MB/s的PXI总线吞吐率,因此图像采集、存储都能满足系统要求.

本系统中,被测产品的图像数据采用的是并行多通道输出,每一路通道上的数据都采用标准的LVDS信号格式进行传输,因此根据实际情况研制图像调理模块将多路图像信号调理成为可以供图像采集卡采集的单路图像信号.系统硬件总体设计如图2所示.

图2 系统硬件总体设计Fig.2 Overall design of the system hardware

2.2 图像调理模块设计

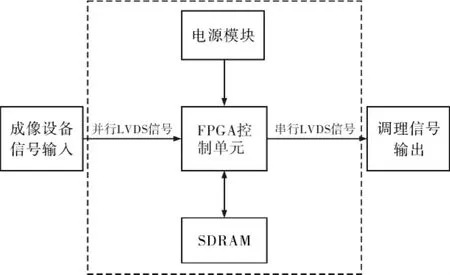

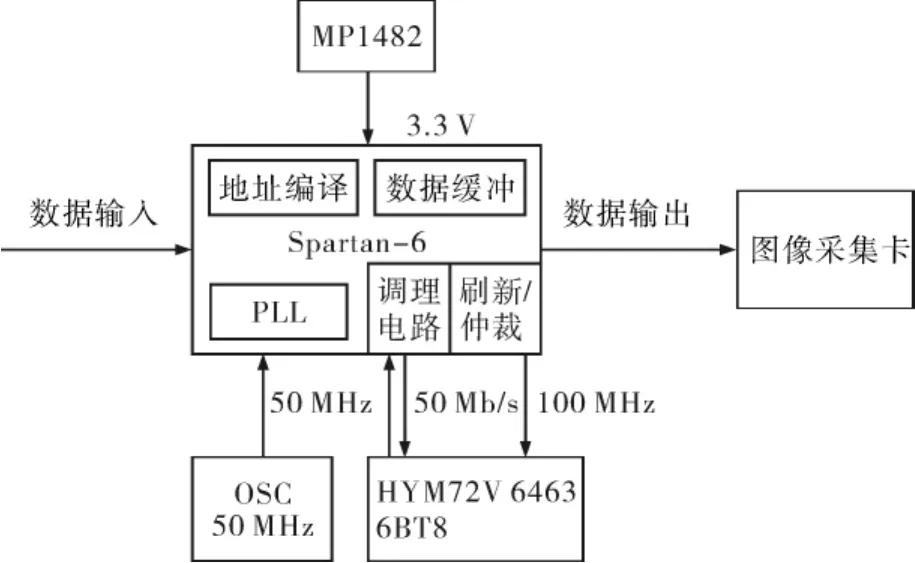

在多通道高速数据采集过程中,由于采集的数据量大、速度快,若采用在上位机对各个信号进行处理会增加软件工作负担,而导致系统实时性无法保证,因此需要研制专用硬件电路将多路信号实时转换成单路信号供上位机使用.现场可编程门阵列(Field-Programmable Gate Array,以下简称:FPGA),全部的控制逻辑都由硬件实现,因此能有效地应用在多通道高速图像数据采集处理中[4-5],图像调理卡的总体设计如图3所示.

图3 图像调理卡总体设计(虚线内)Fig.3 Overall design of image processing card(dashed line)

同步动态随机存储器(Synchronous Dynamic Random Access Memory,以下简称:SDRAM)采用的是HYNIX公司的HYM72V64636BT8,该芯片容量为32M×8bit×4bank.FPGA采用的是由Xilinx公司生产的Spartan-6,该芯片采用低功耗的45nm制作工艺,含有150000个逻辑单元.电源采用的是 MP1482,50MHz的晶振,FPGA逻辑图如图4所示.

图4 FPGA逻辑图Fig.4 Logic diagram of FPGA

FPGA硬件资源进行如下分配:

①地址编译:完成地址的编码和译码;

②数据缓冲:完成输入数据到SDRAM得数据缓冲;

③锁相环(Phase Locked Loop,PLL):用于完成时钟管理;

④调理电路:通过硬件编程语言实现的逻辑电路,用于将多路信号合并成单路信号;

⑤刷新/仲裁:SDRAM 工作时钟为100 MHz,需要在64ms内刷新8192行数据,刷新电路用于刷新计时,完成计时后向仲裁电路发送请求用于向SDRAM发送刷新命令.

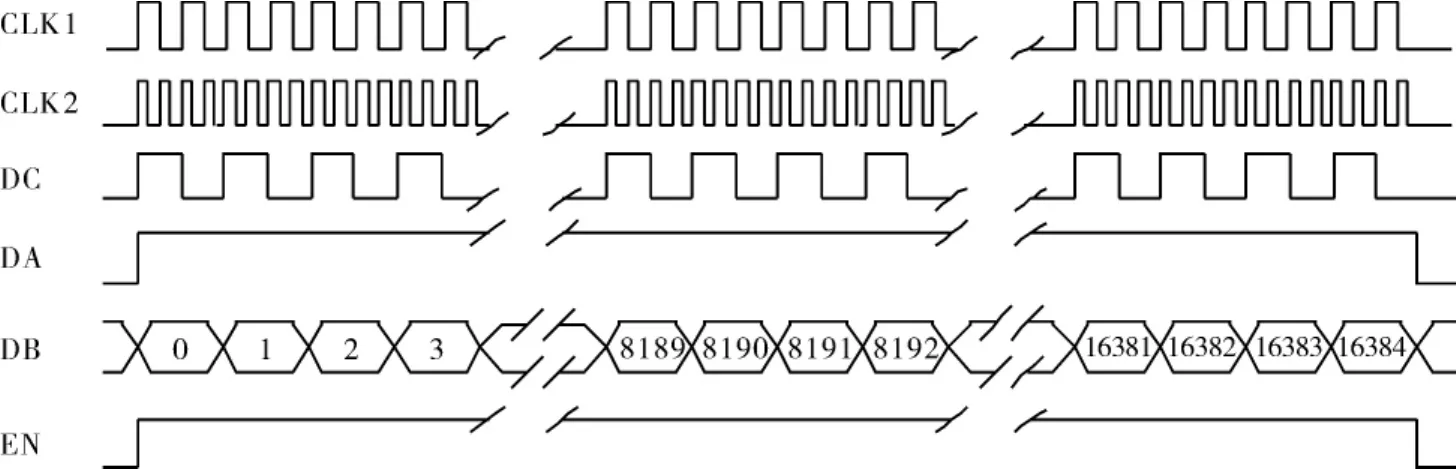

本系统中共有三路传感器信号,其中DA信号用作帧同步信号,DB信号用作图像信号,DC信号用作字同步信号,CLK1为50MHz时钟,CLK2是倍频后的时钟,为100MHz,EN为数据有效信号.在本系统中,帧同步信号DA每帧出现一次,使用上升沿触发;DC每个字出现一次,也使用上升沿触发.当EN信号有效时,FPGA对数据进行接收和处理,将DA、DB、DC三路信号调理成为一路信号,并将该信号写入到SDRAM缓存中.接收信号的时序图如图5所示.

图5 信号时序图Fig.5 Timing diagram of signal

3 软件设计

3.1 软件总体设计

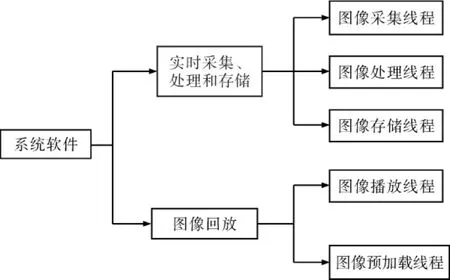

采集系统软件总体设计如图6所示.系统软件由两部分组成,第一部分用于实现图像的实时采集、处理和存储功能,采集图像数据,并经过一系列处理提供给用户观察,同时将采集得到的数据进行保存;第二部分用于实现事后回放功能,提供用户详细观察采集数据的功能.

3.2 实时采集、处理和存储

图6 系统软件总体设计图Fig.6 Overall design of the system software

图像经过PXI总线送到计算机内存中,经过一系列处理后将数据导到显示器上提供给客户实时观察,并将该数据转移到硬盘中进行存储,在这个过程中,共涉及到了三个线程.因此采用“生产者/消费者”结构,“生产者/消费者”结构是多线程编程中一种最常见的设计模式.从软件的角度看,生产者是数据的提供方,消费者是数据的消费方,生产者和消费者之间存在一个数据缓存区,大小一般固定,当生产过剩而消费不足时,缓存区的空间将被耗尽,此时生产者必须停止生产直到缓存区出现剩余空间.同理,当消费能力大于生产能力时,缓存区内的数据会逐渐减少,直到缓存区内再无数据可用,此时,消费者处于等待状态[6-7].在此图像采集线程作为生产者,而图像处理线程和图像存储线程作为消费者.

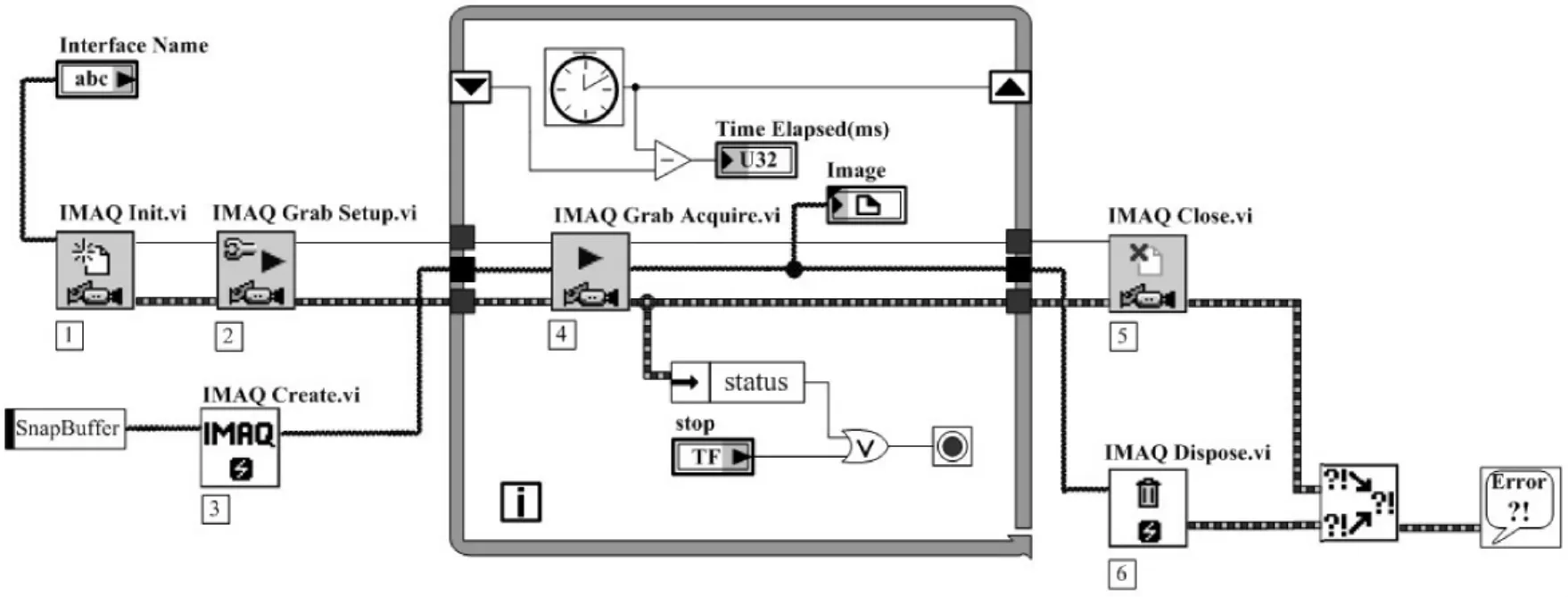

3.2.1 数据采集 图像采集卡将采集得到的图像数据放入先入先出(First Input First Output,FIFO)缓存区中,然后驱动程序通过PXI总线将图像卡缓存中的数据送到计算机内存中.使用LabVIEW进行采集的步骤如下所示:

①调用IMAQ Init.vi完成图像采集卡的初始化工作;

②调用IMAQ Grab Setup.vi初始化连续采集过程;

③调用IMAQ Create.vi创建图像数据缓冲区;

④调用IMAQ Grab Acquire.vi快速采集图像数据;

⑤调用IMAQ Close.vi关闭占用的图像采集板卡;

⑥调用IMAQ Dispose.vi释放占用的图像数据缓冲区.

采集程序的程序流程图如图7所示.

图7 采集程序流程图Fig.7 Flow char of acquisition program

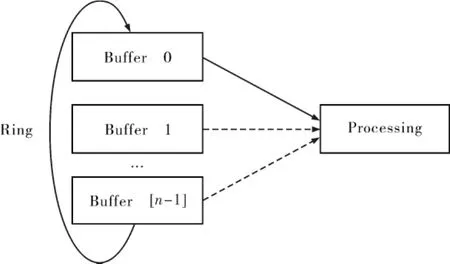

当图像采集速度非常高时,可以适当的将一个大的缓存区划分成若干个小的缓存区,采集得到的数据分步式写入缓存区或从缓存区中读出,如图8所示,这样就可以有效地预防缓冲区中的图像数据还没有被处理干净的情况下就被新的图像数据覆盖.

图8 分步缓存写入/读出Fig.8 Cache read/write step by step

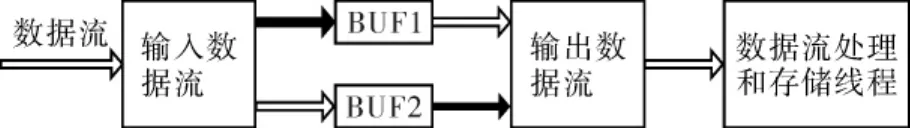

3.2.2 数据处理 应用程序建立两个线程分别来实现数据从图像卡到内存的操作和数据由内存到显示器显示的操作.两个线程以低耦合的方式运作,最大限度地调动了中央处理器(Central Processing Unit,CPU)和内存的执行效率,实现了实时的采集、处理功能.LabVIEW以其特有的自动多线程的编程特点,可以合理的分配两个线程之间的时间片,实现两个线程并发进行.采集线程用来接收图像采集卡采集得到的数据,采用乒乓读写方式[8],将该数据送到处理进程和存储进程中去,在此线程中设置两个数据缓冲区(Buffer,以下简称:BUF)BUF1和BUF2,当一个缓冲区缓冲从图像采集卡接受的数据时,另一个缓冲区将采集得到的图像数据输出到处理和存储线程中,如图9所示.

图9 乒乓读写Fig.9 Table tennis to read and write

数据采集时,在帧同步信号为高时,将采集得到的数据写入缓存BUF1中,与此同时,将缓存BUF2中的数据读出,并将该数据流处理和存储线程.在帧同步信号为低时,将采集得到的数据写入缓存BUF2中,与此同时,将缓存BUF1中的数据读出,并将该数据流处理和存储线程.通过这种乒乓读写方式实现数据流的无缝缓存.

处理线程用于将采集得到的图像数据进行分析和显示,考虑到计算机运行的效率以及人类视觉的滞留时间,需要选择适当帧数用于显示和观察,通常设置为25~30Hz.

3.2.3 数据存储 数据存储线程用来实现数据由内存到硬盘存储的操作,考虑到硬盘的读写速度和每次写操作完成的时间,在此线程中开辟一个能存储100帧图像的缓存区,让每次写操作完成100帧数据的存储.

3.3 数据回放

没有经过任何处理的图像数据通常特别巨大,而提供给应用程序的内存的容量却是有限的,因此需要合理分配内存资源.

应用程序在此建立两个线程分别完成数据的显示和加载,显示线程将所需数据从内存中取出后并加以分析和显示.加载线程主要实现内存的管理,该线程将下一时刻内存中所需数据从硬盘中取出,并将使用过的数据从内存中清空,在此采用块加载,每次加载100帧数据,这样可以有效地提高程序的运行效率.

4 系统实现

该系统中使用的高速摄像机的帧频为100 fps,图像分辨率为128×128×16位,图像的采集、存储速度约为26Mbps,连续存储时间不低于2h,工控机为酷睿双核T7500,1024吉字节(Gigabyte,GB)硬盘,2GB内存,图像采集卡为 NI PXI-1428.操作系统为微软XP SP3,采集时的频率不能低于100fps,回放时能够以100fps的频率连续播放存储两小时以上的图像数据.

经过实验证明,在2个小时的采集存储中,采集得到的图像清晰稳定,没有出现丢帧现象,采集的帧频稳定在100fps.在此采集过程中CPU的占用率稳定在40%以下,内存使用率低于35%,基于LabVIEW的LVDS高速图像采集系统完全可以满足速度为26Mbps的图像采集要求,并且还为更加高速的图像采集提供了可能.

5 结 语

本文在对LabVIEW编译环境下的基于PXI平台的图像采集系统的基本工作原理做了一个基本的介绍,并讲述了如何使用LabVIEW编程语言实现高速图像数据的采集和处理.经过实际的反复测试,证明采用LabVIEW的编程环境,不仅使得编程效率大幅提升,而且实现了稳定的高速图像采集和处理功能,使得该系统不仅实现了预期的效果,并且还有进一步挖掘其潜力的空间.

[1]黄立胜,刘月花.遥感数据的高速实时记录器[J].遥感学报,2003,7(1):19-25.HUANG Li-sheng,LIU Yue-hua.A High-Speed Real-Time Digital Recorder Based on Personal Computer[J].Journal of Remote Sensing,2003,7(1):19-25.(in Chinese)

[2]王胜,王新宇.LVDS技术及其在高速系统中的应用[J].遥测遥控,2005,26(4):41-46.Wang Sheng,Wang Xinyu.LVDS and It's Application in High Speed System [J].Telemetry &Telecontrol,2005,26(4):41-46.(in Chinese)

[3]陈煜.一种专用光机组件测控系统的设计与开发[D].武汉:武汉工程大学,2011.CHEN Yu.The Design and Development of a Special Ray Machine Components Control System[D].Wuhan:Wuhan Institute of Technology,2011.(in Chinese)

[4]侯朝勇,胡学浩,庒童.基于FPGA的多路同步实时数据采集系统[J].电子技术应用,2009,35(10):103-105,108.HOU Chao Yong,HU Xue Hao,ZHUANG Tong.Multi-channel synchronal real-time data acquisition system based on FPGA[J].Application of Electronic Technique,2009,35(10):103-105,108.(in Chinese)

[5]胡宏平,胡兵.基于FPGA的双口RAM在信号采集中的应用[J].微计算机信息,2007,23(7-2):223-224,229.HU HONGPING,HU BING.Application of Dualport RAM Based on FPGA in the Signal Acquisition[J].Microcomputer Information,2007,23(7-2):223-224,229.(in Chinese)

[6]雷晏瑶,李智.基于生产者/消费者的数据采集系统设计[J].机械,2011,38(9):39-43.LEI Yan-yao,LI Zhi.Design of data acquisition system based on producer/consumer[J].Machinery,2011,38(9):39-43.(in Chinese)

[7]张秀娟.生产者-消费者采集建模与行为分析方法研究[J].微电子学与计算机,2004,21(5):97-100.Zhang Xiu-juan.Modeling and Behavior Analysis for Producer-Consumer System[J].Microelectronics &Computer,2004,21(5):97-100.(in Chinese)

[8]Hennessy J L,Patterson D A.Computer Architecture: A Quantitative Approach [M].San Francisco:Morgan Kaufmann Publishers,1996.