基于FPGA的运动控制系统串口扩展设计

赵兵,黄晓华

(南京理工大学机械工程学院,江苏南京 210094)

0 引言

串口通讯因为其协议简单,操作方便,如今已在工业控制系统、仪器测量系统等各个领域被越来越广泛地应用[1]。而现代计算机、各种处理芯片等其他控制终端仅仅配备了少量的通用串口,在很多需要多串口的系统中并不能满足需求。为了解决在所研究的全向移动机器人运动控制系统中出现的串口个数不能满足的问题,现使用FPGA(field-programmable gate array)芯片进行逻辑编程,实现了扩展多个串口进行通信的功能。

1 运动控制系统结构

在全向移动机器人的运动控制中,使用伺服电动机控制底盘驱动机器人可以进行精密的运动控制,本文使用MAXON电动机搭载以色列公司生产的Elmo伺服控制器进行伺服控制。Elmo伺服驱动器提供了串口与控制芯片通信进行命令地接收和反馈。在运动控制系统中,微处理器采集各种传感器的信息进行分析综合,判定机器人当前所处的状态,根据目前自身所处的状态(包括姿态,方向角,位置点,加速度,速度等其他方面),对安装于机器人底盘的三个电动机发出不同的运动命令,使各个电动机带动机器人的三个全向轮协同工作,达到所需要的运动轨迹,速度,姿态等。

本文的运动控制系统采用了美国公司德州仪器所生产的DSP2812作为主控制器,DSP2812拥有两个串行通信口SCIA和SCIB,但是,在该全向定位控制系统中,不仅需要控制三个伺服电动机的运动,而且还需要与其他传感器和一些监测设备(例如监测状态的电脑终端等)进行通讯,因此,为了实现这些扩展的功能,利用FPGA设计了中间扩展模块。全向机器人运动控制系统结构如图1所示。

图1 控制系统结构图

该系统中的DSP2812与FPGA之间的数据传输采用了并口通信,将扩展的子串口映射到不同的地址中,需要往哪个子串口传输数据时往相应的地址中写入数据即可,读取时,当可读信号脉冲来时,给予中断并通过控制线判定读取的串口号。

考虑到并行通信口要比串口速度快,速度级并不一致,所以设计了缓存模块,在发送和接收系统中加入16×8的FIFO(first input first output)。

另外,FPGA是TTL电平,而串口协议规定的逻辑1电平是-3V~-15V,逻辑0电平是+3V~+15V,两者使用了max232进行电平转换。

2 FPGA扩展模块的设计

为了实现上述的控制要求,本次设计的FPGA使用Altera公司的Cyclone II系列的EP2C5Q208C8芯片,软件设计在Quartus II开发集成设计环境中完成。通过Verilog硬件描述语言实现的功能设计。设计的一些主要模块有全局控制模块,时钟发生器模块,发送模块,接收模块。通过对这些模块的设计编程实现相应的时序控制,完成串口扩展的功能。

2.1 时钟发生模块设计(图2)

图2 时钟模块程序块图

对频率为40MHz的晶振源进行分频,产生所需要的各种时钟频率。将串口通信的波特率设为9600bit/s,在具体的实现过程中,发送和接收模块工作频率设为波特率的16倍,具体分频时,创建一个发送器时钟变量和一个计数变量,初始化为零,每当系统时钟上升沿到来时,计数变量自加1,当计数到130时,发送器时钟变量电平立即反转,计数清零,这样循环往复,就产生了所需的发送接收模块的工作频率。同理,还可以用它产生其他所需要的各种时钟频率。

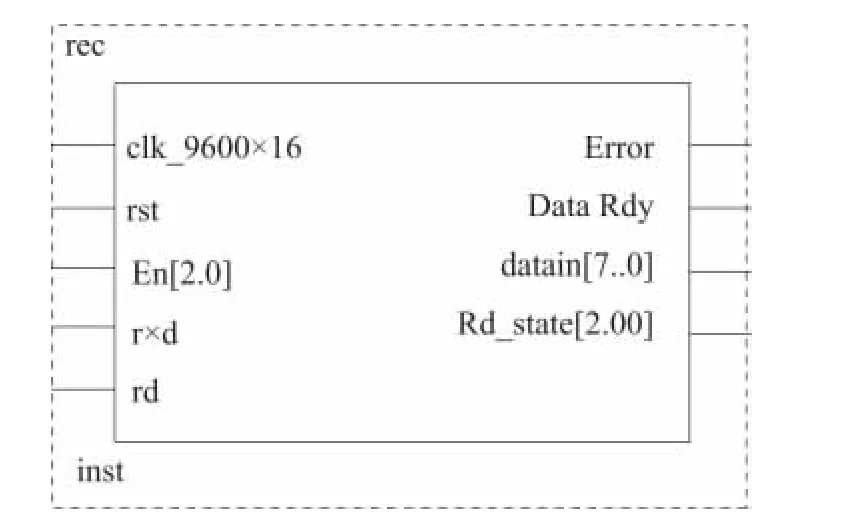

2.2 接收模块设计(图3)

通过时钟发生模块得到的接收模块的工作时钟频率为波特率的16倍,接收模块首先等待数据的到来,串口通信在空闲时为高电平,当有数据进行通讯时首先发送一个低电平的起始位,接收模块在每个工作频率的上升沿到来时检测输入是否为低电平,若是则开始计数,如果连续8个工作频率都检测为低电平,则确认接收到了起始位,此后每隔16个时钟接收一位数据,并将接收到的数据通过移位寄存器转化成并行数据。最后通过并行口传输给主控制器。若接收过程中发现错误接收,Error线拉低,并且丢弃此次所接收数据。

图3 接收模块程序块图

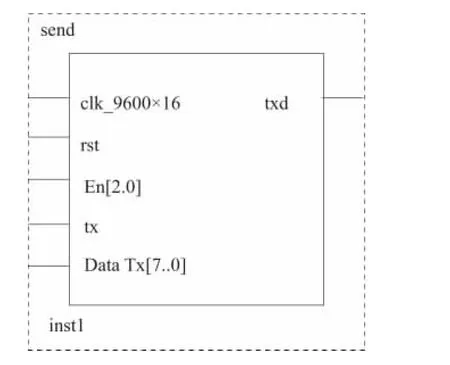

2.3 发送模块设计(图4)

图4 发送模块程序块图

从DSP输出的并行数据在发送模块里转化成串行数据从相对应的串口输出。当发送数据信号电平为高,则将并行数据锁存放入特定寄存器,判定发送寄存器是否有数据,如果有将数据放入FIFO模块,等待发送。对于要发送的数据,在时钟的控制下移位寄存器将它按照从低到高依次发出。

2.4 全局模块

完成上述各子模块的设计后,需要考虑如何使这些子模块在完成自己的功能的同时相互之间配合完成所需的功能。为此,设计了一个全局模块负责这些子模块的协调调度。并口的读写时序与DSP的读写时序同步,需要发送数据时,DSP先拉低FPGA的WR信号线,通过地址线和数据线往相应的地址发送相应的数据。FPGA接收到数据后,由于地址的不同,端口选择线CS[2∶0]将需要发送的端口线拉低。在时序的推动下,并行数据发送给相应分端口的发送模块,然后发送模块通过将数据移位按照一定的波特率串行发送出去。接收数据时,FPGA在接收模块中将串行数据接收转化并行数据,并拉低自身的状态线,全局控制模块通过对状态线的读取获取数据来自于哪一个端口。整个FPGA串口扩展系统的程序图如图5所示。

图5 Quartus II中各模块连接程序图

3 结语

本文成功地在运动控制系统中实现了基于FPGA的串口扩展,解决了处理器串口较少的问题。用Labview编写的上位机测试软件对此系统进行了长达数个小时的发送和接收测试,结果表明效果良好。并且此设计还可以运用到其他需要串口扩展的平台或系统中去,应用面广,实用前景好。

[1]樊正方,罗晖.基于FPGA的串口集线器设计[J].工业控制计算机,2008,21(9):54-55.

[2]张羽,胡玉贵,等.基于FPGA的多串口扩展实现[J].电子器件,2009,32(1):233-236.

[3]张伟,谈良.串行通信接口的扩展在电台组网控制系统中的应用[J].指挥信息系统与技术,2010,01(1):46-49,81.

[4]周之炎,毛玉良.机器人多路传感器数据采集系统的实现[J].机械制造与自动化,2009,38(1):157-159.

[5]杨茂林.基于FPGA的智能串口模块设计[J]工业控制计算机.,2010,23(5):4-5,8.