集成化图像控制引擎的研究与实现

李奇,刘宇红,金海陆

(贵州大学 理学院,贵州 贵阳 550025)

SOPC是Altera公司提出来的一种灵活、高效的SOC解决方案,它是一种特殊的嵌入式系统:首先它是片上系统SOC;其次它是可编程系统,具有灵活的设计方式,可裁剪、可扩充、可升级,并具备软硬件在系统可编程的功能。NIOS II是由硬件描述语言编写的基于FPGA的软核CPU。NIOS II嵌入式处理器不仅提供更高的性能、更低的成本,还提供了齐全的软件开发工具以及系统灵活性设计。本文将结合Nios II处理器的总线架构,分析SD卡的接口协议和驱动程序设计方法;由于FPGA片内的存储资源可能满足不了系统的设计需求,在设计中使用了片外SDRAM作为程序存储和数据存储器。通过SOPC中的Avalon总线接口与Nios II处理器和SDRAM控制器通信,构建了基于Nios II的SOPC,使之能显示图片格式为JPEG的图像 ,并实现各种控制操作,能较好的模拟类似于引擎的操作,并给出基于Nios II处理器的设计实例。

1 NIOS II处理器的Avalon总线架构

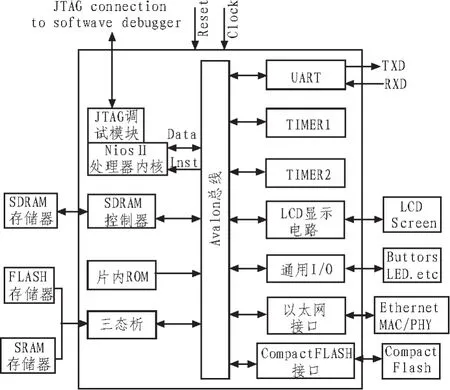

Avalon总线模块是系统模块的主干,是SOPC设计中外设之间通信的主要通道。Avalon总线模块由各类控制、数据和地址信号以及仲裁逻辑组成,它将系统模块的外设连接起来,并描述了主从构件的端口连接关系,以及构件间通信的时序关系。以构成可编程片上系统(SOPC)[1],Avalon总线系统结构如图1所示。

图1 Avalon总线系统结构Fig.1 Avalon-bus system architecture

Avalon总线模块是一种可配置的总线结构,它可以随着用户的不同互联要求而改变。Nios II处理器的片内系统互联主要靠的就是Avalon总线,Nios II处理器和各外设之间都是通过Avalon总线进行交互。Avalon定义了5种不同的传输方式,包括从端口传输、主端口传输、流水线读传输、流传输控制和三态传输。本文仅分析和讨论SD卡设备所使用的从端口传输方式。

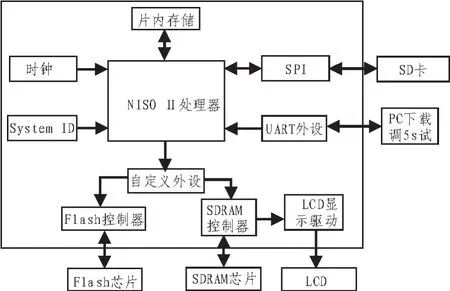

一个Nios II处理器系统可以说是包含了一个可配置CPU软核、FPGA片上存储器和片外存储器、外设以及外设接口等的一个片上可编程系统,所有的Nios II处理器系统都用同一的指令和编程模式[6]。一个典型的Nios II处理器系统如图2所示。

图2 NIOS II处理器系统Fig.2 NIOS II processor system

Nios II处理器系统[2]根据不同用户的要求,其设计类型也不同,在设计中,CPU为主要部件,需要强大的性能,除了实现Nios II处理器系统外,剩下的逻辑资源可以用作粘贴和逻辑使用;而在另一些设计中,Nios II处理器系统只占FPGA一小部分资源,性能要求不高,剩下的逻辑资源可实现主要的逻辑功能。在这些系统中,如果用户逻辑需要和Nios II处理器系统相互通信,用户逻辑可以直接挂在片内的Avalon总线上。Nios II是一个可灵活配置的软核处理器,是用户根据自己设计的性能或成本要求,灵活的增加或裁剪一些系统特性和外设。用户甚至可以在系统中放置多个Nios II处理器内核,以满足应用的要求。本设计中由于要处理图片信息,故选用的是快速型内核“Nios II/f”。其系统架构如图3所示。

图3 系统架构Fig.3 system architecture

本设计中根据Nios II处理器系统配置的SOPC系统如图4所示。

图4 SOPC系统Fig.4 SOPC system

由此产生的设计原理图模块如图5所示。

图5 原理图模块Fig.5 Schematic module

2 SD卡读写控制设计

SD卡(SecureDigitalMemoryCard)是一种常见的存储器件,以FlashMemory为存储体,SD卡允许两个可选的通信协议:SD模式和SPI模式。文中所研究的是SPI协议下的SD卡设计。

2.1 SD卡的接口-SPI协议分析

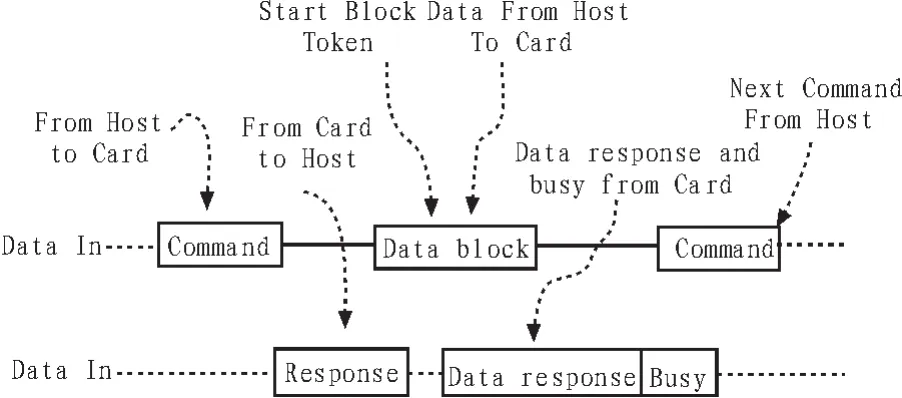

在SPI模式下,SD卡支持单块的或是多块的写操作,在接收到一个合法的写指令时,SD卡件响应一个应答标记的等待主控制器发送这个数据块。

图6 单个块的读取操作Fig.6 Single block read operation

在SPI模式下,SD卡支持单块的或是多块的写操作[3],在接收到一个合法的写指令时,SD卡将响应一个应答标记和等待主控制器发送这个数据块。

图7 单个块的写入操作Fig.7 Single block write operation

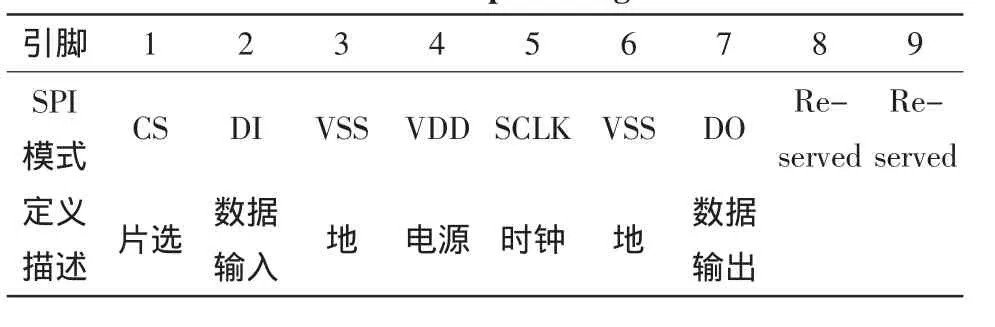

SPI模式下SD卡引脚定义如表1所示。

表1 SD卡引脚定义Tab.1 SD card pin configuration

SPI总线允许通过 DI(数据输入)和 DO(数据输出)两个通道传输数据,数据为串行模式,每8位数据为一组。输入数据和输出数据在SCLK的上升沿是锁存。SD卡的复位、初始化、写操作和读操作等都是通过DI端口发送SPI命令进行控制的,SPI命令由 6个字节组成,其格式如表2所示。

表2 SPI命令格式Tab.2 SPI command format

字节1由“命令号+0x40”组成。例如,CMD55,55的16进制为 0x37,0x37+0X40=0X77,二进制为 01110111。

字节2-5为命令参数,共32为宽度。有些命令有参数,有些命令没有参数。对于没有参数的命令可以直接置0x00、0x00、0x00、0x00、0x00。

字节6为“CRC校验位+停止位”,对于SPI模式下的命令不需要进行CRC校验,可直接置为0xff。

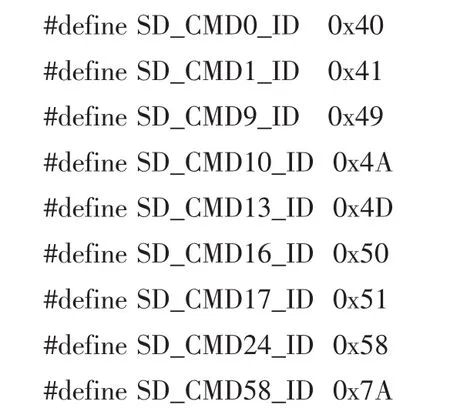

本设计中使用到的命令如下:

2.2 SPI内核

SPI内核集成在SOPC Builder内部,SPI内核的结构如图8所示。

图8 SPI内核结构Fig.8 SPI core construction

由图可知,SPI内核的接口信号有两条数据线、一条同步时钟和一条控制线,它们分别表示如下。

Master Out Slave In(mosi):主设备输出数据到从设备的数据线。

Master In Slave Out(miso):从设备输出数据到主设备的数据线。

Serial Clock(SCLK):主设备与从设备之间的数据同步时钟。

Slave Select(SS_n):主设备驱动选择从设备的选择信号,低电平时有效。

SPI内核有 5 个存储器应像的寄存器:rxdata、txdata、status、control和slaveselect。寄存器提供了用户与SPI内核的设计接口,SPI内核支持流传输,设计中与DMA控制器相连接。

在 Nios II中,Alter提供了一个函数 int alt_avalon_spi_command(),该函数提供了对配置为主设备的SPI内核的通用接口访问,该函数原型为[4]:

int alt_avalon_spi_command(alt_u32 base, alt_u32 slave,alt_u32 write_length, const alt_u8 * write_data,alt_u32 read_length, alt_u8*read_data,alt_u32 flags);

调用该函数可以写一个或多个字节的数据到数据缓冲区并通过mosi端口发送,然后从miso端口读回一个或多个字节的数据。

函数的参数说明如下。

alt_u32 base:选择主设备

alt_u32 slave:选择从设备,0为第一个从设备,1为第二个从设备,以此类推。

alt_u32 write_length:设置主设备发送数据的字节数。

const alt_u8*write_data:待发送缓冲数据,函数将数组中的数据依次发出。

alt_u32 read_length:设置主设备接收数据的字节数。

alt_u8*read_data:接收的数据缓冲。

alt_u32 flags:如果从不连续的数据缓冲区发送数据,可以多次调用该函数,每次指明访问的合并标志(merge flag),则访问从设备之后不会释放从设备,即SS_n为低电平。如果flag=0,则访问从设备之后会释放从设备,即SS_n为高电平。

3 SOPC中TFT LCD控制器核与驱动设计

本设计中使用Nios II软核对TFT-LCD进行驱动时,片内的存储器资源满足不了系统的设计需求,因此在设计中将使用片外SDRAM作为程序存储器和数据存储器。

3.1 SDRAM控制器内核

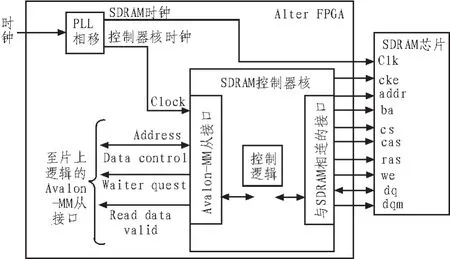

SDRAM控制器内核为FPGA片外的SDRAM提供了一个Avalon_MM接口,可以使用SDRAM控制器将片外的SDRAM芯片连接到自定制的Nios II系统中。如图9所示为SDRAM控制器内核与片外SDRAM芯片连接的框图。

图9 SDRAM控制器内核与外设的连接Fig.9 SDRAM controller core and peripherals connection

3.2 TFT-LCD组件设计

LCD控制器主要由Avalon总线接口、寄存器组、控制模块,DMA、FIFO以及时序生成模块组成。每个寄存器独立编址。处理器通过Avalon总线读写寄存器,从而完成对LCD控制器工作状态的设定与控制。控制器启动后,DMA Master通过Avalon总线读取SDRAM中的数据,然后存入FIFO中,外部的SDRAM控制器在每一场的开始都会清空FIFO,然后保持FIFO中有数据(但不溢出)可供当前显示。在每次FIFO读请求信号有效后,相应的FIFO输出数据也会送到该模块内部进行锁存。时序生成模块按照TFT时序要求从FIFO中读取数据,然后送出去显示。由于DMA读取的速度与TFT时序发生器输出的速度不一致,所以在DMA与TFT时序发生器之间加入FIFO用来缓冲数据,DMA由控制模块控制其工作,控制器不断检测FIFO状态,当FIFO快满是,暂停DMA,当FIFO快空时,重新启动DMA,如此循环,保证显示画面的连续性与稳定性。

3.3 TFT-LCD控制的实现

设计中利用取模软件将图片格式为JPEG的图像转化成从上到下、从左到右的RGB像素点色彩数据[5],然后将这些数据以并行的方式传递给LCD显示,器驱动原理如图10所示。

图10 LCD驱动原理Fig.10 LCD drive

本设计中使用的LCD有一个16位的数据接口,设定要显示的点的XY坐标,以及显示什么颜色。触摸屏为4线式触摸触摸屏,四线触摸屏包含两个阻性层。其中一层在屏幕的左右边缘各有一条垂直总线,另一层在屏幕的底部和顶部各有一条水平总线,为了在X轴方向进行测量,将左侧总线偏置为0 V,右侧总线偏置为VREF。将顶部或底部总线连接到ADC,当顶层和底层相接触时即可作一次测量。为了在Y轴方向进行测量,将顶部总线偏置为VREF,底部总线偏置为0 V。将ADC输入端接左侧总线或右侧总线,当顶层与底层相接触时即可对电压进行测量。

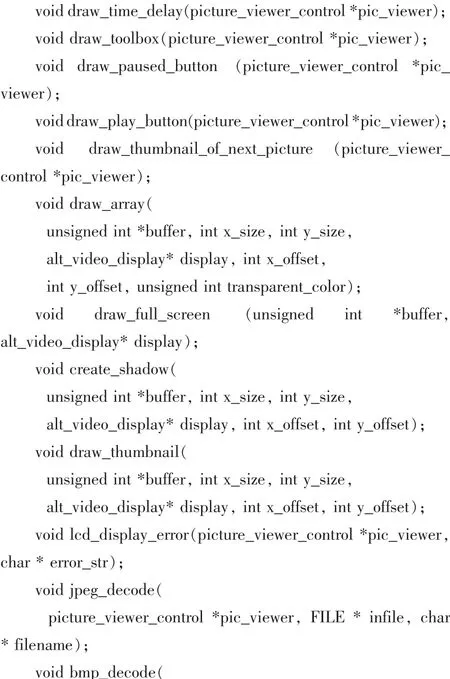

设计中使用软件编程的方法实行控制,利用C程序在触摸屏中的相应的位置画上相应的控制图标。

4 结束语

基于NIOS II软核处理器的设备驱动设计方案具有良好的稳定性与灵活性,可以按照设计者的需要去设计每个细节,使整个系统结构清晰明朗,设计比较灵活,设计中深刻的理解了FPGA的体系结构与各部件协同的工作方式。设计中成功的实现的图片格式为JPEG图像的显示与控制。并对SD卡的接口协议与LCD显示有了较深刻的理解。

[1]孙恺,程世恒.NiosⅡ系统开发设计与实例》[M].北京:北京航空航天大学出版社,2007.

[2]赫建国,倪德克,郑燕.基于Nios II内核的FPGA电路系统设计[M].北京:电子工业出版社,2010.

[3]王黎明,陈双娇,闫晓玲,等.ARM9嵌入式系统开发与实践[M].北京:北京航空航天大学出版社,2008.

[4]Altera Corporation.Nios II softerware developer’Handbook[S].2009.

[5]吴厚航.爱上FPGA开发-特权同学和你一起学NIOS II[M].北京:北京航空航天大学出版社,2011.

[6]Altera Corporation.Nios II processor reference handbook[S].2009.