SOI电路可靠性筛选技术及失效机理研究*

黄 龙,刘 迪,陆 坚,顾晓峰

(1.轻工过程先进控制教育部重点实验室,江南大学电子工程系,江苏 无锡 214122;2.中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

与传统体硅器件相比,绝缘体上硅(SOI)器件具有许多优良的性能,例如无闩锁效应、集成度高、源漏寄生电容小、工作速度快、功耗低、易形成浅结、抗辐射及耐高温特性好等。因此,SOI常被誉为“21世纪的硅集成电路技术”[1],受到了广泛的关注和应用。然而,随着器件特征尺寸不断缩小,SOI电路遇到越来越多可靠性问题的困扰[2]。高效的可靠性筛选试验及相应的失效机理分析,对提高SOI产品的良率有重要的意义[3]。本文通过实验对比,归纳了SOI电路最常用的三种可靠性筛选试验方法,并利用光发射显微镜(EMMI)、扫描电子显微镜(SEM)、聚焦离子束(FIB)及激励源诱导故障测试(SIFT)等常规及先进失效分析手段,对筛选出的失效样品进行了失效模式及机理分析。

2 常用可靠性筛选技术

可靠性筛选试验是指对电子器件按一定要求施加一种或多种应力进行试验,揭示器件的质量缺陷及其他潜在缺陷,并剔除早期失效的器件,它是提高电子产品良率的重要技术手段[4]。可靠性筛选试验常包括老炼应力、高温贮存、温度循环、机械冲击、恒定加速度、噪声颗粒碰撞、气密性等试验。但是,在实际工程中,受时间和经济效益的约束,难以对产品实施每一项可靠性筛选试验。因此,提高SOI电路可靠性筛选试验效率,寻求高效的筛选方法十分重要。表1给出了经过大量可靠性筛选试验与失效分析总结出的失效模式与筛选方法之间的对应关系。可以看出,对于大部分SOI电路的失效产品来说,老炼应力、高温贮存和恒定加速度试验为较常用的筛选方法,利用它们可实现对成批产品的快速高效筛选。

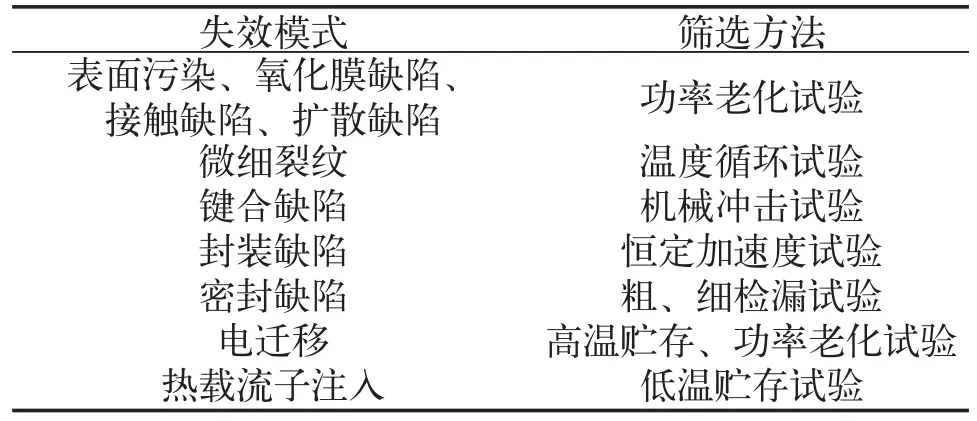

表1 失效模式与筛选方法之间的对应关系

3 三种SOI电路的筛选试验及失效分析

下面针对三款SOI电路分别进行老炼应力、高温贮存及恒定加速度可靠性筛选试验,对比失效样品和合格样品,结合多种电学与物理失效分析手段,分析失效机理及根源。

3.1 老炼应力筛选试验及失效分析

老炼应力筛选试验是对电路或器件施加超过其额定工作条件的应力,以更高的灵敏度暴露出与时间和应力有关的失效模式的筛选试验。实际常把电应力试验和温度试验结合起来,测试器件抵抗和适应剧烈温度变化的能力,以加速暴露出器件或电路中的潜在缺陷。

针对某SOI高速DDS (Direct Digital Synthesizer)产品进行功率老炼筛选试验,试验环境温度为125 ℃,老炼板上施加的反偏电压为5.5 V,持续时间为120 h。终点电性能测试发现电路功能异常,样品失效。老炼试验的结果表明电路内部发生了损伤,为进一步确认失效模式,利用J750集成电路测试系统上对样品作全面的功能和性质测试。结果表明,失效样品工作电流为192 mA,明显超出规范值(<150 mA)。正常产品的输出为正弦波形,而失效样品输出的波形杂乱无规律,如图1所示。利用半导体参数分析仪测试正常产品及失效样品各端口和GND端的伏安(I-V)特性,发现失效由电源和GND端短路引起。

图1 正常产品与失效产品的输出波形

确认失效模式后,对失效样品作电学分析。在开盖前对电路做X光分析,检查是否因样品管腔内存在异物短路或键合搭丝等异常而导致失效。X光检查结果如图2所示,发现样品腔内无异物,芯片也未出现断裂等异常。然后对失效样品进行开盖处理,利用光学显微镜观察样品全貌,发现各管脚焊点正常,键合丝无断裂;再观察电路内部结构和I/O端口等细节,也未发现异常。因此,需要利用具有高分辨率的微观缺陷定位技术EMMI进一步分析此失效样品。

图2 失效样品的X光检查结果

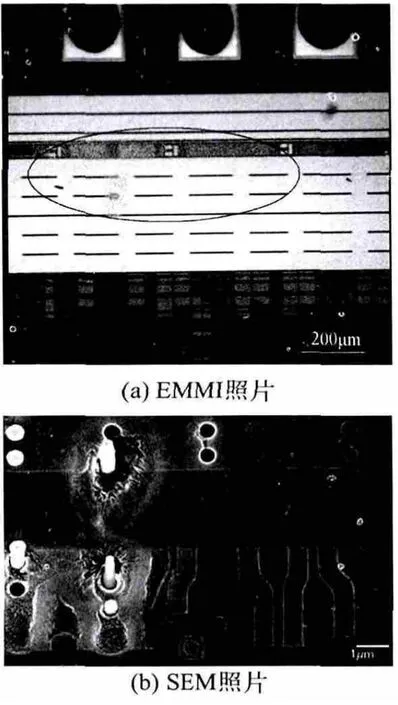

EMMI能在较大范围内迅速准确地定位缺陷,在失效分析中应用广泛,尤其适用于存在漏电、击穿、热载流子效应的器件[5]。对整个芯片的EMMI观测表明,电路的发光点集中在数字部分的GND端口区域。图3 (a)给出了失效区域的EMMI照片,由于失效电路顶层金属层较密,样品发出的光无法完全透过金属层,只能探测到从表面金属层间隙透出的光点(如图中圆圈所示),但已足够精确定位失效位置。

确定失效位置后接着进行物理分析。根据SOI电路的制造工艺参数采取相应的去层步骤,利用反应离子刻蚀(RIE)、研磨机台及化学腐蚀逐一剥除各层,每去除一层即利用SEM观察,直至发现缺陷。在剥除金属层、氧化层后均未见异常,但去除多晶层后,在衬底上发现了异常:PN结严重击穿,硅衬底发生了局部熔融,如图3 (b)所示。

图3 芯片失效区域的EMMI及SEM照片

考虑到该样品进行老炼筛选试验时的工作环境(125 ℃高温、5.5 V反偏、持续120 h),试验时电路工作的功率过大(正常功耗约3 W)且工作在高温下,导致电路内部产生较大的热量,使芯片温度急剧升高。当芯片上的峰值温度超出最大允许结温时,电源和地之间的PN结产生了大量热载流子。随着结温继续上升,热载流子进一步增多,形成不断加剧的正反馈,最终在电应力和热应力的共同作用下,PN结击穿烧毁,导致电路功能失效。可见,良好的散热条件对该电路的正常工作非常重要,而试验芯片采用的是塑料封装,散热能力较差。因此,对于这类功率较大的SOI芯片,改用陶瓷封装能更好地保证散热能力,提高芯片的可靠性。

3.2 高温贮存筛选试验及失效分析

SOI产品常使用在高温等恶劣环境下,因此对SOI电路进行高温贮存筛选试验,研究其高温失效机理十分重要。高温贮存试验可加速产品内部的化学变化,快速暴露出潜在缺陷[6]。当高温配合电压源一起作用于样品时,对剔除由器件体内、表面和金属化系统存在的潜在缺陷所引起的失效有较显著的效果。在热和电的共同作用下进行高温反偏试验是此类筛选中常用的方法,比单纯的高温贮存筛选效果更佳。

对某SOI译码器芯片进行高温贮存试验,环境温度135 ℃,反偏电压5 V,贮存时间480 h。终点电性能测试发现样品失效,表现为输出管脚无信号输出。为进一步确定失效模式,用半导体参数分析仪对失效芯片进行直流测试,测试结果显示输出管脚开路。

首先进行电学失效分析。对失效模式为开路的失效产品,运用SIFT技术进行失效区域定位[7]。SIFT是一种新型高分辨率微观缺陷定位技术,具有灵敏度高、可定位微弱漏电流、扫描范围广、不受显微镜头视场限制等优点。本文选用主要用于开路、高阻等失效点定位的645 nm激励源扫描样品。先对芯片进行全局扫描寻找失效位置,如图4 (a)所示,在逻辑区边缘发现存在异常点;然后扫描失效区域,可以更清晰地观察到失效位置,如图4 (b)所示。

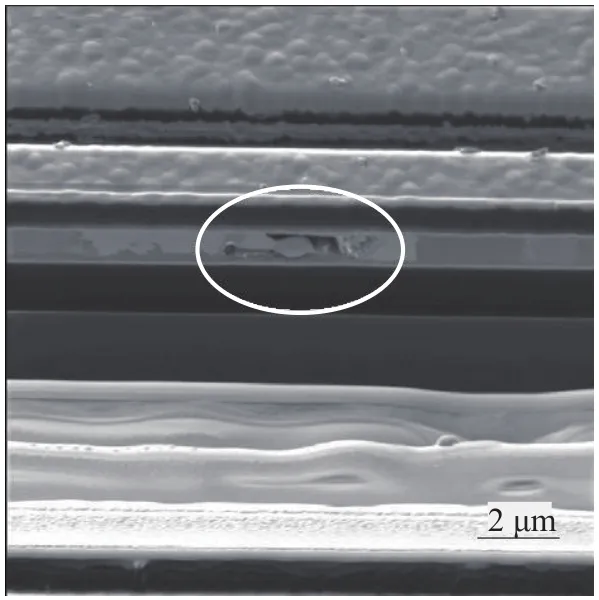

定位失效区域后再进行物理失效分析。利用FIB对失效区域实施切割,以观察缺陷、分析失效机理。FIB技术不仅具有扫描成像功能,还可对器件进行刻蚀、淀积、离子注入等微纳加工,是失效分析中常用的技术手段[8,9]。从图5所示失效区域的FIB剖面图中,可观察到金属互连线之间存在较大面积的空洞,这是造成芯片开路、失效的主要原因。

结合该芯片的试验条件,由上述电学与物理失效分析可知,当芯片在高温恶劣环境下工作时,由于铝的抗电迁移能力较差,在温度大于100 ℃、电流密度大于106A·cm-2的情况下,铝层将发生电迁移,金属连线形成小空洞,容易造成电路开路、样品失效。鉴于其他试验样品均未出现失效,可推断该失效样品是由于铝线在制造过程中可能有过划伤,致使通过铝条的电流密度变大,发生了电迁移所致的失效。因此,对于SOI电路要特别注意避免损伤或划伤,即使微小的受损也可能导致失效或留下潜在缺陷。

图4 全芯片及失效区域的SIFT扫描结果

图5 失效区域的FIB剖面图

3.3 恒定加速度筛选试验及失效分析

SOI电路封装过程中常会引入一些杂质,对可靠性造成潜在威胁[10]。通过恒定加速度试验不仅能很好地筛选出这类失效产品,而且还可用来测定封装、内部金属化和引线系统、芯片和基板的焊接以及器件其他部件的机械强度极限值。研究的样品是某SOI专用集成电路,对其进行恒定加速度筛选试验后,终点电性能测试发现失效芯片地址输入端口漏电流为103 μA,远大于正常样品的漏电流参考值(10 μA),而其他电学参数及功能均正常。为进一步确认失效模式,利用电源和万用表对失效电路地址输入端口进行漏电测试,发现该管脚对地和电源的击穿电压正常,对电源无明显漏电,但对地有较大的漏电(~500 μA),因此判断失效原因是地址输入端口发生短路。

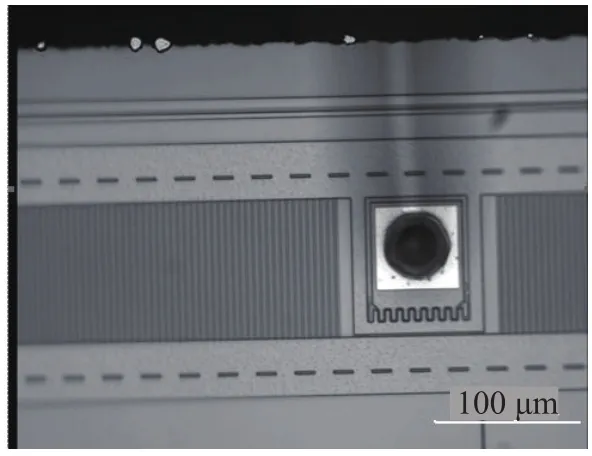

确认失效模式后进行电学失效分析。类似地,开盖前对电路做X光分析,未发现存在异物短路或键合搭丝等异常。开盖后在光学显微镜下观察电路表面,包括漏电管脚在内的各端口均未损伤,但观察金属基板时发现有几条明显的划痕,且发现数条残留金属丝,其中一条搭在失效管脚的键合金属丝上。为精确定位失效位置,在失效管脚与地之间施加5 V电压进行EMMI分析,结果如图6所示,漏电点的位置全部出现在硅衬底与金属基板之间。

图6 失效芯片的EMMI观测结果

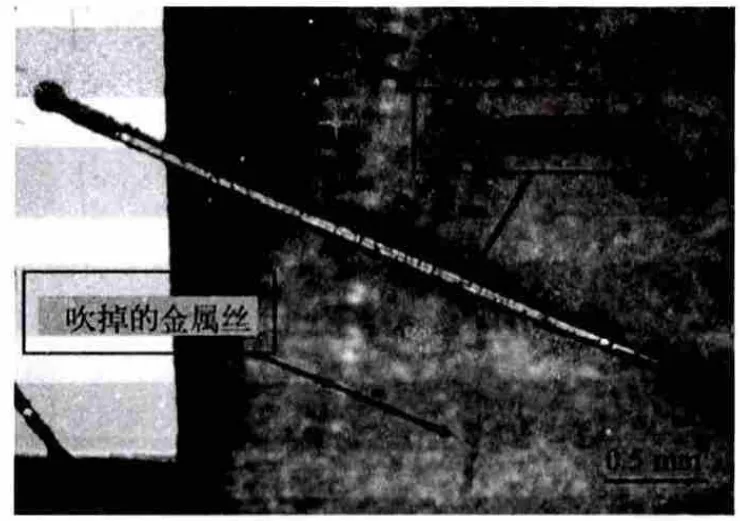

结合该样品的试验条件可得到如下判断:经过恒定加速度的作用,封装后残留的杂质金属丝搭在失效管脚键合金丝上,使基板与失效管脚连接,导致硅衬底与基板接触处出现较大漏电流。为验证上述判断,如图7所示,用风枪将失效管脚键合金属丝上的杂质吹掉,再对电路进行测试,发现漏电仅为1.1 nA,其他所有参数也都合格。因此可确认,引起该芯片失效的根源是封装时残留的金属丝与芯片键合金丝搭丝,引起短路,导致电路失效。

图7 风枪处理后的键合情况

4 结论

文章分析了SOI电路可靠性筛选试验中各种试验作用与失效模式的对应关系,侧重讨论了功率老炼、高温贮存及恒定加速度三种常用的高效可靠性筛选方法,并利用它们对三款SOI电路进行了筛选试验。综合运用EMMI、SIFT、SEM、FIB、光学显微镜及X光等失效分析手段,澄清了失效样品相应的失效模式和失效机理,包括热电应力引起的PN结热击穿、电迁移引起的芯片开路及封装失效等,为改进工艺、提高SOI电路的可靠性提供了有益的参考。

[1]COLINGE J P.Silicon-On-Insulator Technology: Materials to VLSI[M].Boston: Kluwer Academic Publishers,2004.

[2]HAO Y,ZHU J G.The gate-oxide breakdown effect couple by channel hot-carrier-effect in SOI MOSFET's[J].Chinese Journal of Electronics,2001,10: 204-209.

[3]BALESTR F.Impact of Device Architecture on Performance and Reliability of Deep Submicron SOI MOSFETs[J].半导体学报,2000,21(10): 937-954.

[4]丁继善.国内半导体器件的可靠性筛选技术[J].半导体技术,1999,24(3): 55-57.

[5]陈兆轶,方培源,王家楫.CMOS器件及其结构的显微红外发光现象研究[J].固体电子学研究与进展,2006,26(4):460-465.

[6]黄云,恩云飞,杨丹.混合电路贮存可靠性及评价方法[J].微电子学,2007,37(2): 173-176.

[7]刘迪,顾晓峰,陆坚,等.基于SIFT技术的集成电路失效缺陷分析[J].固体电子学研究与进展,2012,32(4): 336-340.

[8]PHANEUF M W.Application of Focused ion Beam microscopy to Materials Science Specimens[J].Micron,1999,30(3): 277-288.

[9]BISCHOFF L,TEICHERT J.Application of Highly Focused Ion Beam[J].Materials Science Forum,1997,248-249: 445-450.

[10]马丽丽,包生祥,彭晶,等.微波电路中In/Al合金焊点的失效分析[J].电子器件,2007,30(3): 766-769.