一种射频识别卡电路的可测性设计

李 环,居水荣,景为平

(南通大学江苏省专用集成电路设计重点实验室,江苏 南通 226000)

1 引言

PMD801是一个非接触式射频识别卡电路,支持ISO 4443A的标准;工作频率为13.56 MHz,能够进行快速数据传输,传输速率为106 kbit/s;也可以进行快速的数据处理,单个票务检测不超过35 ms;通过采用奇偶校验、位编码、位计数等技术,使得这一芯片具有数据安全性高的优点;电路具有防冲撞功能,也使得具体应用非常可靠;电路内部根据ISO/IEC14443A-3第二级协议设置了7字节序列号;内含512 bit的EEPROM存储单元,可以进行数据的读写操作,其中512 bit分成16页,每页4字节,每页可编程,具有写保护功能,并提供了12页共384 bit用户读写区。该电路主要用来制作电子标签等一些非接触式射频识别卡,适用于物流、大型超市、门禁、公交卡等场合,具有非常广阔的应用前景。

PMD801是依靠非接触卡内部嵌入的天线感应到的电流作为该电路的电源,属于无源电路,因此在电路设计中采取低功耗设计是必须的;同时为了测试电路内部的功能模块,在可测性设计方面采取了比较灵巧的设计方案,整个电路有两个射频端口、一个地;另外就是一个测试输出端,通过对这个输出端口的一些信号进行测试,可以清楚知道电路内部各个模块的功能和性能,本文重点描述这一类电路的可测性设计。

2 PMD801总体工作原理和功能模块

2.1 电路总体功能框图

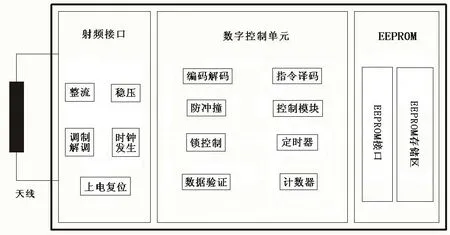

非接触式射频识别卡电路PMD801主要由射频接口电路、数字控制单元和EEPROM电路三部分组成,该电路的功能框图如图1所示。

图1 PMD801功能框图

2.2 电路总体工作原理及流程描述

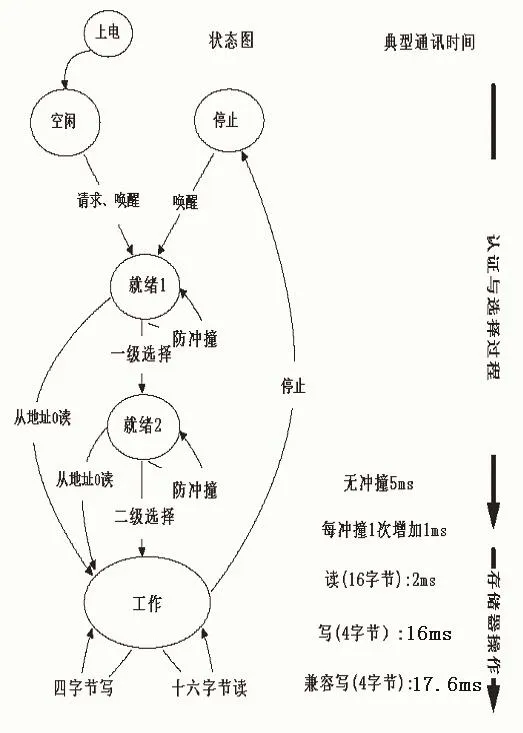

在PMD801进入阅读器(读卡器)的有效范围内后,通过交流磁场耦合,该电路从阅读器获得能量,产生电路工作所需的电源。当电路的电源电压超过2 V时,电路上电复位,只要PMD801保持在阅读器的有效范围内,对电路的内部寄存器进行初始化操作,在复位完成后,电路进入空闲状态(IDLE),等待阅读器发送请求。如果阅读器发送请求指令,电路将应答,并且如果型号匹配,电路进入准备好状态。此后,如要进行通信,阅读器需要发送一级防冲撞指令,PMD801接收指令,并把序列号的低三位字节回复给阅读器。防冲撞指令是为了避免许多智能卡电路同时对阅读器响应,进行一个选择而使用的指令。在阅读器接收到序列号的低三位字节后,阅读器作出判断,选择其中一组序列号低三位字节作为后面的选择,对应其他序列号的电路,将不再响应任何指令。此后,阅读器把刚才选择的序列号低三位字节发送返回给PMD801,PMD801将进行应答。阅读器获得应答后,发送二级防冲撞指令,刚才序列号低三位字节被选中的电路将把序列号的高四位字节回复给阅读器,这样,阅读器再次作出判断,选择唯一的一个七字节序列号,并将这个唯一序列号的高四位字节发送返回给PMD801,将有唯一一个PMD801进行应答,此PMD801就是后面通信被选择的电路,此时,防冲撞操作完成。最后,阅读器可以与这个被选择的PMD801进行读、写操作了。电路工作过程的状态如图2所示。

图2 PMD801工作状态图

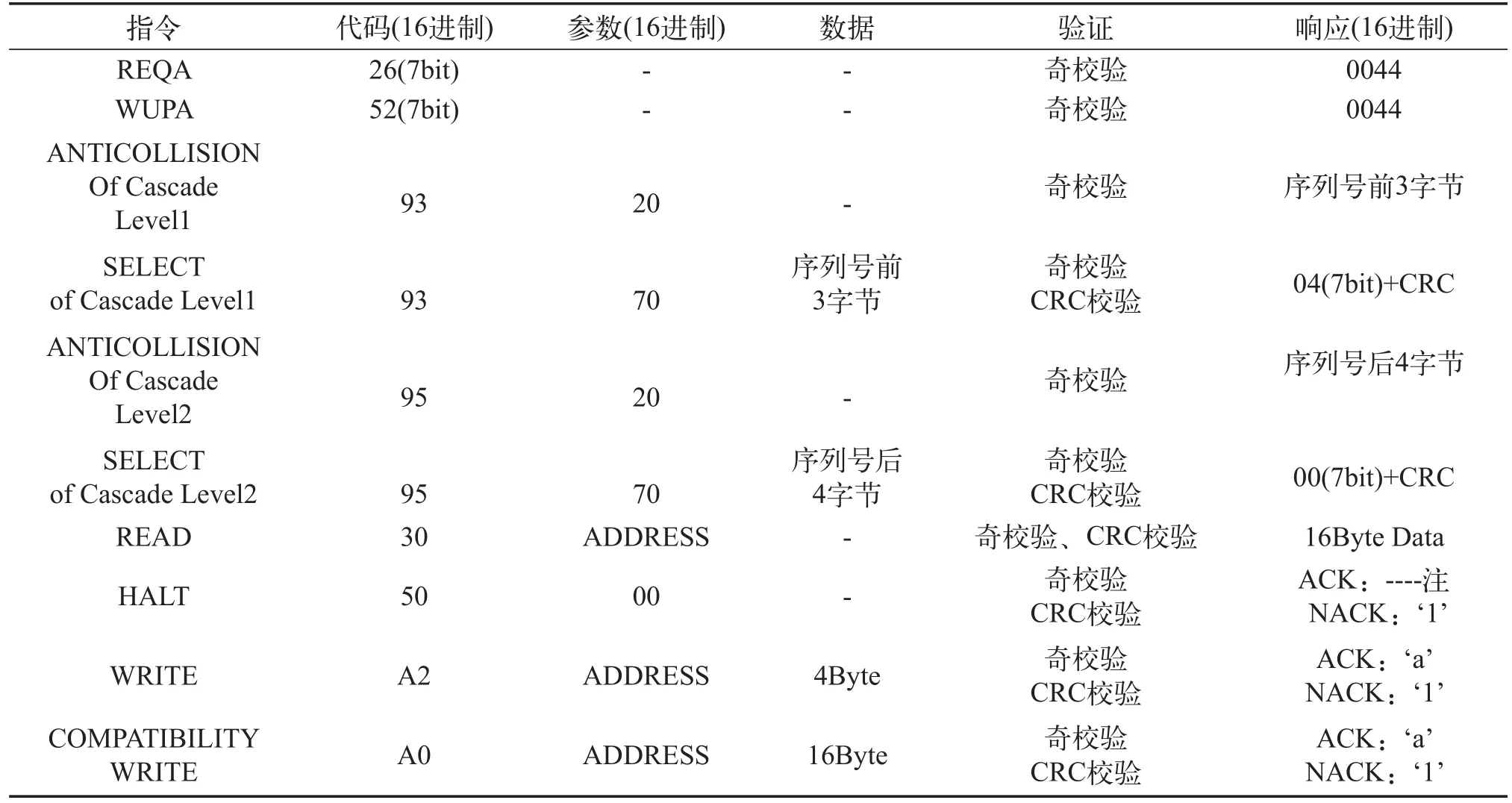

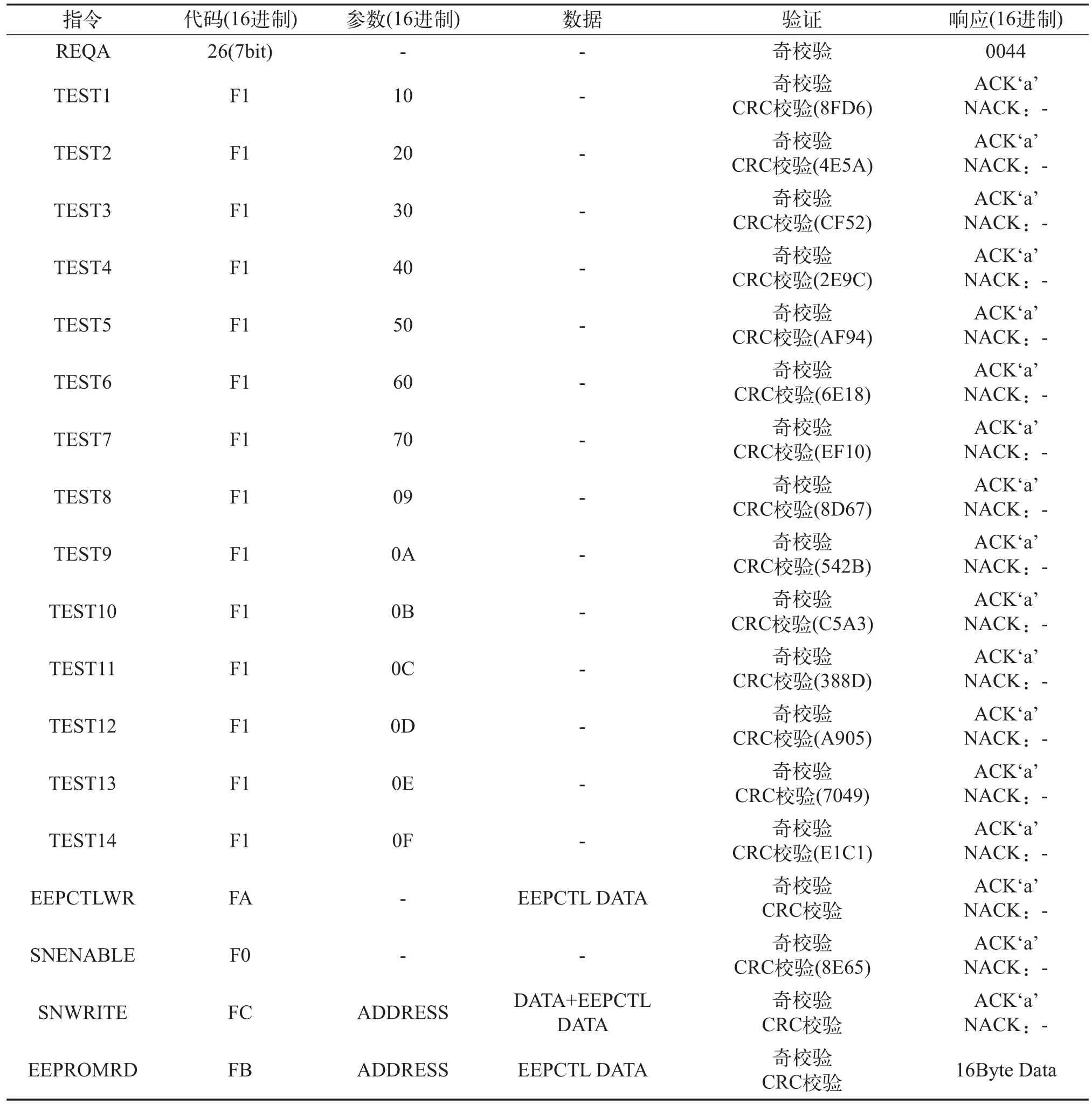

2.3 PMD801指令介绍

在以上电路工作流程中提到了指令,这里把本电路涉及到的指令作一个列表,见表1。

下面以读指令(READ)为例,给出我们做的Verilog仿真波形图,如图3所示。

图3 读指令(READ)的Verilog仿真波形

表1 PMD801指令列表

2.4 电路主要功能模块介绍

2.4.1 数字控制单元

数字控制单元主要包括编解码电路、数据验证、时钟分频电路、地址译码与地址锁控制、指令译码、计数器、写周期定时器等。从射频接口产生的时钟信号将在时钟电路部分被分频,作为其他数字电路工作的时钟,而数据信号则将由解码电路解码,作为指令、地址以及数据送入指令译码电路和地址锁控制部分等电路。同时,数字部分的编码电路,对需要从PMD801发送出去的数据,先进行曼彻斯特编码,再送调制电路,通过高频负载波发送给PCD。

2.4.2 模拟电路(射频接口)

PMD801的模拟部分主要包括上电复位、参考电平发生电路、整流稳压电路、调制解调电路以及时钟发生电路等。

3 PMD801测试电路介绍

PMD801的测试主要包括功能测试与性能测试,功能测试主要是通过对内部数字信号的测试来判断电路的功能是否正常,性能测试主要是通过对内部模拟信号的测试来验证电路的性能如何。

具体来说,在电路内部增加testpad,可以将电路内部的关键模拟信号或数字信号通过多选器的形式选通输出到testpad,数字信号的输出包括:输入的未解码数据、输入的调码后的数据、输出的调制数据以及对电源电压检测的结果。模拟信号的输出包括:数据的未解调信号、内部带隙基准源的电平、内部三极管的VBE电平以及电源电压经过电阻分压获得的电压输出信号等。

3.1 测试电路结构

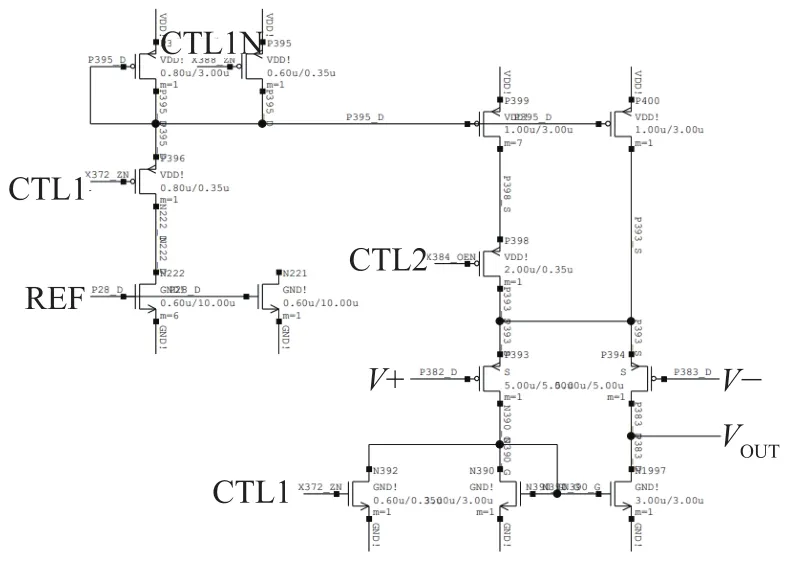

对数字信号的测试分为8个通道,对模拟信号的测试分为7个通道。为准确测试内部输出的模拟信号,电路内部的模拟信号在输出到TEST端前,需要经过一个跟随器,目的是去除干扰信号同时增加驱动能力。具体的测试电路如图4所示。

图4 测试电路结构

如图4,测试输出电路分为两部分,包括数字信号测试输出端和模拟信号输出端,他们的选通电路由地址译码电路复用产生。当选择数字信号测试输出时,模拟输出部分的跟随器将不工作,模拟输出端的传输门关闭。当选择模拟信号测试输出时,上面的推挽输出将关闭,上面的输出为高阻态,下面的模拟输出端的传输门打开。数字信号的输出包括:输入的未解码数据、输入的调码后的数据、输出的调制数据以及对电源电压检测的结果。模拟信号的输出包括:数据的未解调信号、内部带隙基准源的电平、内部三极管的VBE电平以及电源电压经过电阻分压获得的电压输出信号,根据输出四个分压信号可以计算获得准确的VDD电平。

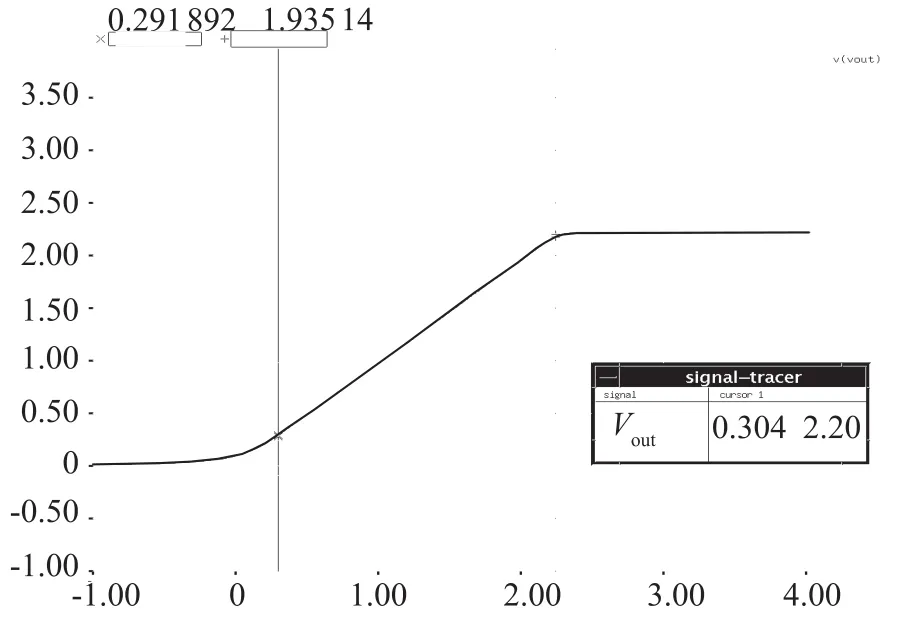

图4中的跟随器电路逻辑图如图5所示,对跟随器电路,主要是关注对输入的信号电路能够正常跟随输出的输入电压范围,对输入电压进行DC扫描,仿真获得输入电压在0.2~2.2 V内,电路都能够准确地跟随输出。

图5 电压跟随器逻辑图

图6是对输入电压进行DC扫描的hspice仿真获得的波形图。

图6 输入电压DC扫描波形图

测试输出端结构如图7。

3.2 测试过程及测试指令

在PMD801进入测试状态前,PMD801接收阅读器发送的请求(REQA)指令,同时PMD801响应请求,应答ATQA(0x0044),阅读器接收ATQA,并确认建立与PMD801的连接关系,允许阅读器向PMD801发送测试指令。

图7 测试输出端结构

表2为测试中用到的指令列表。

下面分别介绍各测试小项:

(1)TEST1:判断电路的工作电压,当VDD>2.60 V,从测试端输出高电平;

(2)TEST2:执行该指令后,PMD801向阅读器发送的数据,编码后从测试端输出;

(3)TEST3:判断电路的工作电压,当VDD>1.75 V,从测试端输出高电平;

(4)TEST4:执行该指令阅读器向PMD801发送的数据,在PMD801解码前,从测试端输出;

(5)TEST5:执行该指令后,当电路允许接收阅读器发送的数据时,阅读器向PMD801发送的数据,在 PMD801解码前,从测试端输出;

(6)TEST6:执行该指令,阅读器向PMD801发送的数据经PMD801解码后,从测试端输出;

(7)TEST7:执行该指令后,如果解码电路正常工作,则从测试端输出高电平;

(8)TEST8:执行该指令后,VDD经过内部电阻分压输出电平,从测试端输出;

(9)TEST9:执行该指令后,VDD经过内部电阻分压输出电平,从测试端输出;

(10)TEST10:执行后内部发射区面积为50 μm2的PNP管的VBE电平,从测试端输出;

(11)TEST11:执行该指令后,VDD经过内部电阻分压输出电平,从测试端输出;

(12)TEST12:执行该指令后,VDD经过内部电阻分压输出电平,从测试端输出;

(13)TEST13:执行该指令后,带隙基准源电平从测试端输出;

(14)TEST14:执行该指令后,射频接口解调后的模拟信号,从测试端输出;

(15)EEPCTLWR:指向电路写入EEPROM的控制数据;

(16)SNENABLE:指通过向电路发送该指令,允许向电路写入序列号;

(17)SNWRITE指令:写入序列号的EEPROM地址以及序列号数据;

(18)EEPROMRD,可以读出刚写入的序列号数据。

表2 测试用指令列表

如果拿到的样品电路已经通过厂家的测试并被写入了序列号,则以上测试无法进行。以上测试项目都是基于样品电路未写入序列号的情况下进行的。在电路被制造出来后,厂家将对每个芯片写入唯一的序列号,在写入序列号的同时对特定的内部数据位写入高电平,将永久禁止再次写入序列号。下面说明一下写入序列号的过程。首先,阅读器向电路发送SNENABLE指令,电路应答“a”,表明允许向电路写入序列号;其次,阅读器向电路发送SNWRITE指令,在该指令中包括需要写入序列号的EEPROM地址以及序列号数据,在完成每次的SNWRITE指令后电路将应答“a”,写入序列号的指令需执行三次才能完成序列号的写入,同时对EEPROM的特定位写入高电平,禁止再次写入序列号。通过执行指令EEPROMRD,可以读出刚写入的序列号数据。

下面以写指令为例,给出我们对该指令所做的Verilog仿真波形图,见图8。

图8 写序列号仿真波形

4 总结

本文通过对一种工作于13.56 MHz的非接触式射频卡电路进行可测试性分析,介绍其工作原理与功能模块,通过对输出端信息的测试可以很清楚地知道各模块的功能及其电路性能;介绍了出厂电路写序列号的过程,并对序列号的写入与写出做了Verilog仿真,验证了电路的正确性,达到了预期的效果。

[1]刘悦.非接触IC卡及其读写模块的设计和ASIC实现[D].上海:复旦大学,2003.

[2]虞致国,魏敬和.一种SOC片上调试与可测试性的整合设计[J].电子与封装,2010,10(2).

[3]陈敏.无线射频识别(RFID)应答芯片的研究和设计实现[D].广州:华南理工大学,2005.

[4]胡瑜,韩银和,李晓维.SOC可测试性设计与测试技术[J].计算机研究与发展,2005,01.

[5]R.W.Waugh.Desing Detectors for RFID Tags[M].Proceeding of RF ExPo West.1995.

[6]ISO/IEC 1443-3.Identification cards-contactless integrated circuit(s) cards-proximity cards,2001.