钛酸铋压电陶瓷厚膜的制备

赵欣欣,张 帆

(沈阳化工大学 材料科学与工程学院, 辽宁 沈阳 110142)

随着电子元器件向小型、高灵敏、集成、多功能化方向发展,厚膜材料及器件逐渐成为研究的重点。压电厚膜的厚度通常为10~100 μm,能产生很大的驱动力,具有更宽的工作频率,且工作电压低,与半导体工艺兼容[1]。因此,压电厚膜已引起了世界各国研究者广泛的关注,并且广泛用于各种微型器件中,如微泵,超声马达,谐振器等[2,3]。多层晶粒定向技术是制备厚膜材料主要方法[4],其利用丝网印刷把纳米尺度(30~80 nm)的原料制成厚膜,从而获得沿一定方向取向生长的压电陶瓷。与热处理技术和模板晶粒取向生长技术相比,该方法不需要制备模板粒子,并且制备的陶瓷样品取向度高,制备工艺简单,成本低。钛酸铋(Bi4Ti3O12, 简称BIT)具有适中的介电常数、较高的居里温度和较小的矫顽电场,在集成铁电学和集成光学方面具有广阔的应用前景[5-7]。本文首先以化学共沉淀法制备纳米BIT粉体,然后采用多层晶粒生长法,通过丝网印刷制备BIT厚膜,并讨论了烧结温度、对陶瓷取向度的影响。

1 实验部分

1.1 BIT粉体的制备

以五水硝酸铋 ﹑ 草酸和钛酸四丁酯为原料,采用化学共沉淀法制备纳米BIT粉体。其具体步骤是:在磁力搅拌条件下,将钛酸四丁酯溶于无水乙醇溶液中,逐滴滴加到草酸的无水乙醇溶液中,可得到无色澄清溶液;再将五水硝酸铋的硝酸溶液逐滴滴入上述的混合溶液中,产生乳白色浑浊共沉淀产物。用氨水调节体系 pH值约为 2,充分反应一个小时后,在60oC下陈化4 h,经洗涤至中性后,恒温80oC干燥24 h,将得到的粉体充分研磨后,在650oC下煅烧2 h得到BIT粉体。

1.2 BIT厚膜的制备

选择松油醇为溶剂,乙基纤维素为粘结剂。将称量好的乙基纤维素缓慢放入松油醇充分混合,得粘稠状透明混合物。将上述制得的BIT粉体与此混合物一起放入球磨罐中,用行星球磨机球磨一小时,得到淡黄色的粘稠状浆料。用丝网印刷技术,把浆料刷到硅单晶片上,经过200oC排塑后,在1 000 ~1 200oC烧结 2~5 h,升温速率为 2oC/min和 10oC/min,最终制备出BIT厚膜。

1.3 表征

采用日本电子的日立S-3400N型扫描电子显微镜(SEM)来观察粉体的表观形貌,采用日本理学株式会社的D/MAX 2400型X射线衍射仪(XRD)对产物进行晶体结构分析并计算其取向度。

2 结果与讨论

2.1 BIT粉体的制备

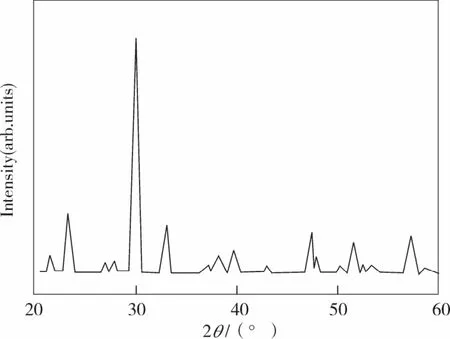

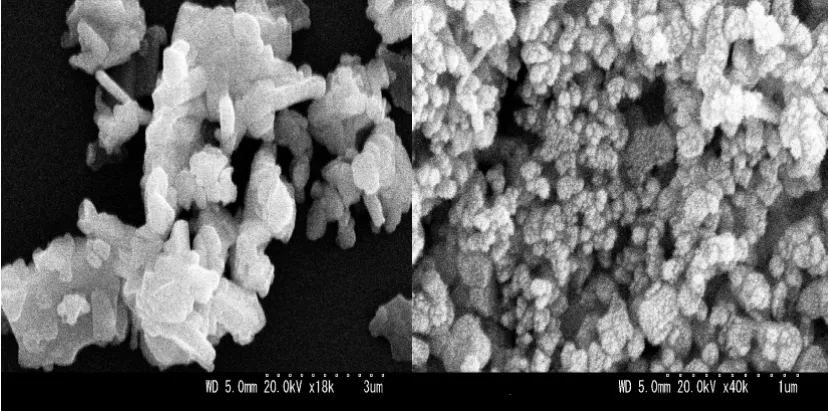

图1是650oC煅烧2 h制得的BIT粉体的XRD谱图。通过与标准 PDF卡片对照可知,所生成的BIT粉体的XRD谱图与单一的斜方晶相的Bi4Ti3O12对应,说明生成了单一晶相的BIT粉体。图2是BIT粉体的SEM图片,由图2可以看出,BIT粉体在球磨前呈片状,球磨后为小于1 μm纳米粉体。说明厚度为纳米级尺寸的BIT片状颗粒在球磨后,纳米级尺寸的BIT片层被破坏,最终得到纳米级粒径尺寸的BIT粉体,这符合丝网印刷法制备陶瓷厚膜对原料的要求。

图1 650 oC煅烧2 h制得的BIT粉体的XRD谱图Fig. 1. XRD patterns of BIT powders obtained at 650 oC for 2 h

图2 BIT粉体的SEM图片Fig. 2 SEM photos of BIT powders.

2.2 BIT厚膜的制备

BIT陶瓷在 a/(b)方向上的自发极化强度大,在c方向上的自发极化强度小。择优取向的钛酸铋陶瓷铁电性能有明显的各向异性。因此可以通过制备高取向度的钛酸铋压电陶瓷来提高BIT压电陶瓷的压电性能。本文以纳米BIT粉体为原料,利用丝网印刷法制备取向BIT厚膜,通过XRD计算出取向度f。取向度f用公式f=(P–P0)/(1–P0)计算,其中P=∑(00k)/∑(hlk),即(00k)晶面的反射强度之和∑(00k)与所有晶面反射强度之和∑(hlk)的比值,P0对应于钛酸铋PDF卡片上的P值。取向度数值从0(完全无取向)到1(完全取向)[8]。

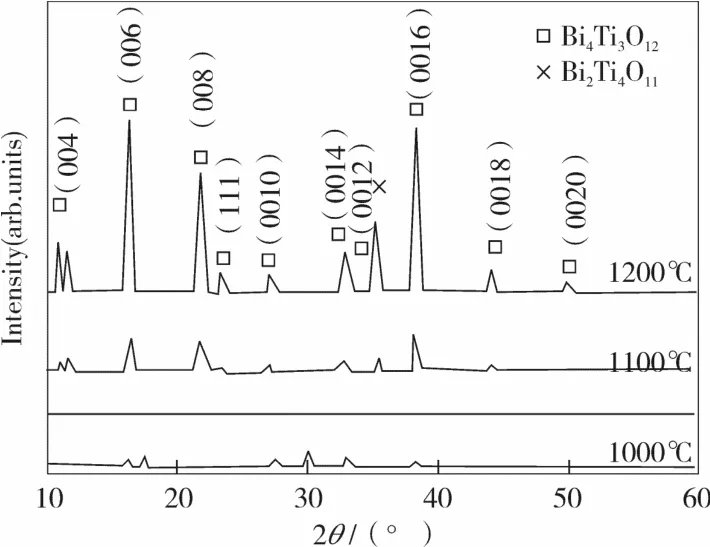

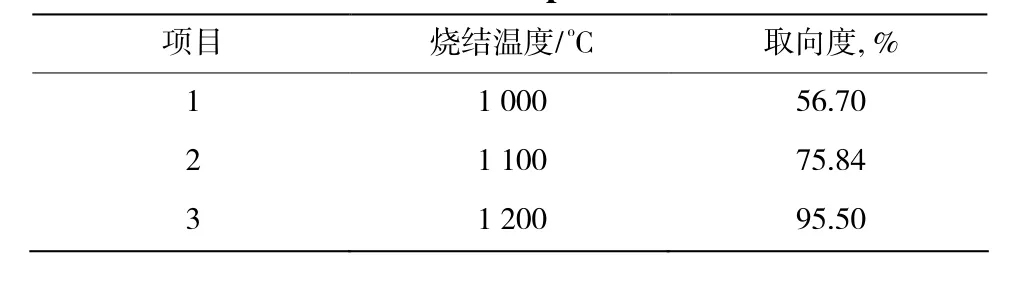

图3为不同烧结温度下,升温速率为10oC/min,保温2 h的BIT厚膜的XRD谱图。如图3所示,在1 000oC烧结,BIT取向生长不明显,且衍射峰强较弱。随着烧结温度的升高,(00k)方向的衍射峰强度明显呈增大的趋势,BIT取向明显增强,这说明随着烧结温度的升高,BIT厚膜(00k)方向定向生长更完全。由取向度的计算公式f=(P–P0)/(1–P0),计算得出如表1所示,以升温速率为10oC/min,烧结温度为1 000oC,保温2 h的BIT厚膜(00k)方向上取向度为56.70%。随着烧结温度的升高,1 100oC和1 200oC时,BIT厚膜在(00k)方向上取向度分别可达75.84%和95.50%。但是,由图3中可以看出,1 000oC及以上温度烧结BIT厚膜时,有杂相Bi2Ti4O11存在,说明高温烧结条件下,Bi元素有挥发,且杂相 Bi2Ti4O11的衍射峰强度随烧结温度的升高而增大,因此需要采取措施减少或避免Bi元素的挥发,如在多Bi环境中烧结。

图3 不同烧结温度的BIT厚膜的XRD谱图Fig. 3 XRD patterns of BIT thick film obtained at different temperatures.

表1 BIT陶瓷厚膜的取向度Table 1 orientation degree of BIT thick film obtained at different temperature

3 结 论

(1)以草酸、钛酸四丁酯和五水硝酸铋为原料,经化学共沉淀法成功制得单一晶相的BIT粉体,650oC煅烧2 h获得的BIT粉体为片状形貌,经过球磨以后,得到粒径小于1 μm纳米球状BIT粉体。

(2)制备BIT厚膜时,随着烧结温度的升高,BIT厚膜在(00k)方向上取向度增大。当烧结温度为1 200oC时,升温速率为10oC/min,保温2 h烧结的 BIT厚膜在(00k)方向上取向度最大可达95.50%。

[1] 伍盟佳,杨群保,李永祥.织构化工艺在无铅压电陶瓷中的应用[J]. 无机材料学报,2007,22(6):1025-1031.

[2] 刘光聪.压电陶瓷材料的新近走向[J].世界产品与技术,2001,122(26):41-43.

[3] 李文卓,赵万生.压电/电致伸缩材料及驱动器的新技术与应用[J].压电与声光,2001,23(11):259.

[4] 曾江涛,李永祥,杨群保,等.压电陶瓷晶粒定向技术[J]. 电子元件与材料,2004,23(11):60-70.

[5] 毛翔宇,王伟,王玮,等.不同晶粒取向钛酸铋陶瓷的铁电和压电性能[J]. 硅酸盐学报,2007,35(3):312-316.

[6] 郝华,刘韩星,等.铋层状结构铁电材料的性能与改性研究[J]. 硅酸盐通报,2004,2(7):52-56.

[7] 毛翔宇,陈小兵.Bi4Ti3O12取向陶瓷的铁电和介电性能[J]. 硅酸盐学报,2004,32(11):1330-1334.

[8] 李崇京.制备晶粒取向的压电陶瓷的新技术[J]. 压电与声光,1990,2(5):12-15.