应用CPLD实现火炮位置测量

盛小波,贾致红,杨 斐

(重庆望江工业有限公司,重庆 400071)

在火炮随动控制应用中,以往采用自整角机和受信仪等测量装置来实现位置测量,结构复杂,在数字系统中还需要双通道SDC转换。现采用绝对值编码器,其传输速度快,精度高,抗干扰能力强,不管编码器的分辨率多少,时钟线和数据线只有4根,硬件接线简单方便,从而省去了复杂的电路和昂贵的测量机构。而码盘一般采用的编码方式为格雷码制,在用户接口可以是格雷码,也可以是二进制码等,与其他编码方式比较,格雷码属于可靠性编码,是一种错误最小化的编码,因为它大大地减少了由一个状态到下一个状态时的混淆,可减少出错的可能性,这就允许代码电路能以较少的错误在较高的速度下工作。

采用格雷码制的同步串行接口绝对值编码器,就必须解决格雷码到二进制码的转换,还需要解决时钟脉冲发送和串行数据接收等数据处理问题。实现格雷码转换为二进制码和相关数据处理的方法有多种,例如采用处理器、FPGA或CPLD。利用处理器实现格雷码到二进制码的转换和相关数据转换,占用处理器资源,效率低下。FPGA是现场可编程门阵列,其内部可编程资源丰富,可以实现格雷码到二进制码和相关数据处理,但是和复杂可编程逻辑CPLD相比,FPGA时序不可预测,上电工作需要一个加载过程,而CPLD拥有上电即可工作的特性,并且CPLD在本质上很灵活、容易使用、时序可预测、速度高、路由性能极好,用户可以在线编程,改变他们的设计同时保持引脚输出不变。

1 SSI绝对值旋转编码器特性

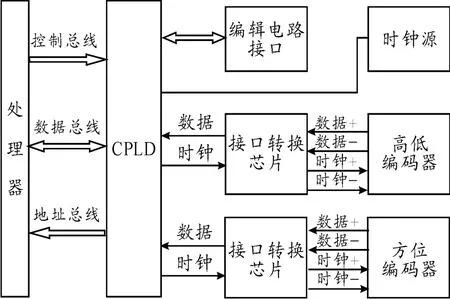

SSI接口用于传输编码器位置数据到控制器,控制模块发送一串时钟脉冲信号,绝对值编码器响应位置数据。SSI信号变化标准见图1。

1)丽水白云山森林公园气温日变化,午后14:00最高,早晨06:00最低。随着海拔的增加,气温逐渐降低的同时气温日较差也随之缩小。日平均气温随海拔的递减率约0.6 ℃/100 m,午后较高(0.8 ℃/100 m),夜间较低(0.5 ℃/100 m)。白天温度明显高于夜间,白天的温度随海拔递减率(0.7 ℃/100 m)也明显大于夜间。气温年变化,7月最高,1月最低,随着海拔的升高,年平均气温降低,同时气温年较差也减小。年平均气温随海拔递减率0.6 ℃/100 m,其中7—10月较高(约0.7 ℃/100 m)。

钢筋网安装就位后进行混凝土铺筑施工。采用5t或10t的混凝土运输车从拌和楼运料,料车车厢底部覆盖塑料薄膜,以防运输过程中有滴漏现象,出站时采用油布覆盖严密,防止混合料水分蒸发损失。自卸卡车到达现场后将混合料卸于料斗后,由料斗将混合料倒入已安装好钢筋网的模板中[3]。混凝土振捣采用自动排式振捣架,振捣棒振动频率在50~100Hz间,每次插入振动时间不超过10min,振捣时注意不能出现虚振、漏振现象,保证铺筑质量均匀。摊铺整平、碾压提浆采用三轮整平提浆机进行作业,抹面结束后采用毛刷拉毛。

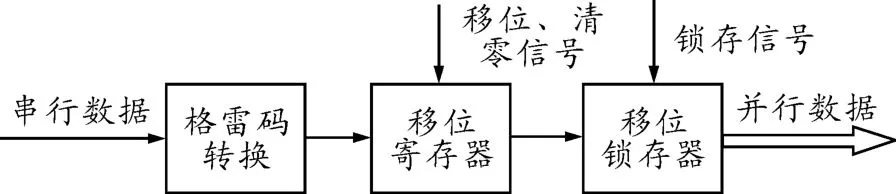

硬件电路结构图2中,有高低编码器和方位编码器两个不同位置方向的编码器,分别用来识别高低方向和方位方向的位置。两个旋转编码器与CPLD之间分别通过各自的接口转换芯片,实现422电平转换和数据的高速传输。选用ALTERA公司的MAX 7000S系列CPLD,它具有128个宏单元,其可编程资源满足本次设计所需。根据采集旋转编码器数据的需要,在线对CPLD进行编程。通过编程,在处理器数据采集允许情况下,产生同步脉冲信号发送给旋转编码器,编码器同步响应格雷码串行数据信号,CPLD对回传的数据信号进行一系列相应的处理,转换成二进制并行数据并缓存,同时向处理器发出数据采集是否好的标志位。图2中,处理器运行在100 MHz的工作主频,通过控制总线和数据采集好标志位,读取缓存在CPLD内部单元的旋转编码器位置数据。

图1 SSI信号变化标准

数据采集信号输入条件有效时,产生移位锁存采集信号,作为采集并且锁存旋转编码器回传的串行数据脉冲。移位信号上升沿触发移位,锁存信号低电平处于锁存期间,高电平则为锁存好状态。

2 硬件电路结构及工作原理

2.1 硬件电路结构

采集旋转编码器回传的数据信号,根据旋转编码器SSI信号变化标准特性,分离出数据末位后的特殊标志位,采集的数据有效时,特殊标志位为低电平,采集的数据无效时则表现出高电平,处理器通过读取特殊标志位的状态判断数据是否有效,便于确定旋转编码器物理线路是否有效连接。

咱都是亲妈,自然是想着把最有营养的提供给娃,菠菜补铁效果好必须得吃啊,胡萝卜护眼效果一流不应该放过啊。但很可能,宝宝对你提供的食物完全没有兴趣,千万不要因为某种食物营养高就强塞、硬喂,一旦宝宝有过不好的进食体验,就会更加抵触辅食。不喜欢吃胡萝卜没关系啊,过段时间也许就喜欢了呢,大不了换一种呗,世间的食材那么多,每种都有各自的营养。

图2 硬件电路结构示意图

2.2 工作原理

本设计与处理器接口采用并行接口,16位数据总线,3位地址总线,2位读写控制线,1位片选线,2位状态线,并行接口使系统读取位置数据的耗时开销最少。主要原理如下:

1)开机初始化,发送数据采集允许信号,判断CPLD是否工作正常,并启动CPLD采集当前数据量。CPLD接收到数据采集允许信号,即刻向旋转编码器发出可靠的同步脉冲信号,旋转编码器收到同步脉冲信号后同步响应格雷码制串行信号,CPLD则在发送同步脉冲的同时,接收旋转编码器回传的数据信号,并同时进行格雷码转换、数据的串-并转换,转换速度快,耗时相当少。转换好的并行二进制数据信号缓存于CPLD的宏单元当中,在非数据缓存期间,置数据采集好信号为有效状态。

2)根据地址总线,在CPLD内部实现地址译码后,依据控制总线,数据总线输出对应状态数据,从而实现处理器对当前数据的读取。处理器根据读取到的不同状态数据,判断旋转编码器硬件是否连接正常,定时读取CPLD采集到的位置数据,并且在空闲期间对连续多次采集到的数据进行判别,剔除非正常数据点保留有效数据,确保所读取数据的准确性。

3 CPLD内部电路设计和仿真

输入条件有效成立时,产生清零信号,每次存储新数据前进行清零,避免下次读取的数据不准确。

图3 CPLD内部电路结构框图

3.1 同步脉冲发生

要实现对旋转编码器的数据采集,首要前提是产生适合所选旋转编码器的时钟信号和接收数据信号所需的信号。同步脉冲发生部分以硅振荡器产生的稳固时钟源为时钟信号基准,以编码器SSI信号变化标准为依据,分析出时钟信号和数据信号的特点,根据实际采用图形编程,并灵活结合verilogHDL硬件语言编程,设计出相应的数据移位脉冲、数据锁存信号和数据清零信号,利用MAX+plus lI开发工具生成如图4所示的简化符号,左边的系统复位sys-reset信号、时钟基准信号clkin、数据采集允许信号pulse-turn-on为输入信号,右边的移位脉冲信号maich、数据锁存信号dhao、清零信号clear等为该部分的输出信号。

图4 同步脉冲发生符号

将1.84 MHz的稳固时钟源转换成0.46 MHz脉冲。数据采集信号输入条件有效时,产生符合旋转编码器特性的同步时钟脉冲信号,周期为113 μs。

病株上的叶脉、叶柄及茎均有黑褐色坏死条斑,并发脆易折。感病初期叶片呈现斑驳花叶或有枯斑,以后背面叶脉坏死,甚至沿叶柄蔓延至主茎。主茎发病时产生褐色条斑,导致全叶萎蔫,但不脱落。重花叶病由Y病毒侵染引起。Y病毒既可以通过汁液机械传染,又可以通过蚜虫传染。

图5 同步脉冲发生部分仿真波形

该同步脉冲发生块实现了如下功能:

图5为同步脉冲发生部分功能仿真波形,其中clkin为模拟振荡器产生的输入波形,clkout和clkout1为发送给旋转编码器的同步脉冲时钟信号,输出信号dhao、maich和clear用以做数据转换块的输入信号,分析该仿真波形信号,符合SSI旋转编码器的时钟信号和接收其数据信号的标准。

空载条件下信号线“数据+”和“时钟+”为高电平(5 V);当时钟信号第一次从高电平跳至低电平时,储存在编码器的当前信息(位置数据(Dn)和特殊标志位(S))的数据就进行传输;在第一个脉冲上升沿到来时,编码器串行数据 首位[MSB]输出;随着一个个脉冲上升沿的到来Dn-1,Dn-2…位就逐一传输;最后一位(LSB)传输完毕,单稳态触发时间Tm截止前,数据线跳至低电平;数据线跳至高电平之前或时钟中断Tp时间截止前,不会有数据传输进行;单稳态触发时间Tm决定了最低传输频率;周期时间T≤1MHz,单拍时间Tm(10 ~30 μs),时钟间隙 Tp≥Tm。

CPLD内部电路是采集编码器串行数据电路设计的重点。ALTERA公司的CPLD开发工具 MAX+plus lI,支持多种输入方式,给设计开发提供了极大的方便,因此本系统采用MAX+plus lI进行设计。系统的主体部分用原理图输入方式,由于库中提供现成的芯片,并且可以自己根据实际需要,灵活选择VerilogHDL、VHDL硬件编程语言等其它输入方式设计,设计出特定功能的部件,还可实现功能仿真,所以使用很方便。CPLD内部电路结构框图如图3所示。

3.2 有效数据判断

图2所示,为硬件电路结构示意图,处理器、CPLD芯片、接口转换芯片、编码器和时钟源是硬件电路的主要组成部分。采用具有较高的抗震动、电击及 EMI冲击的能力的硅振荡器作为时钟源,确保火箭炮在恶劣的环境下也可以稳定的工作。

3.3 数据转换

数据转换块属于寄存器传输级RTL采集位置数据设计。数据转换处理的设计影响数据处理的可靠性,是采集位置数据的重要部分。

采用的倍加福生产的SSI接口型格雷码制编码器,单圈最大精度为16位,多圈最大精度为30位。根据应用对象的技术指标要求,可灵活选取多圈的圈数,在此取多圈2位即可达到应用要求。在收到旋转编码器响应回传的格雷码制串行数据后,逻辑转换成为机器易识别的二进制码并行数据,转换法则是:保留格雷码的最高位作为自然二进制码的最高位,而次高位自然二进制码为高位自然二进制码与次高位格雷码相异或。利用产生的同步脉冲的数据移位脉冲、数据锁存信号和数据清零信号,作为该部分的输入控制信号,根据SSI时钟信号和数据信号的时序特点,设计出合理的采集位置数据机制,仅占用62个宏单元。数据转换部分结构框图如图6所示,利用开发工具生成的简化符号如图7所示。

图6 数据转换块结构框图

图7 数据转换块符号

在功能仿真环境的仿真测试中,得到如图8所示波形。其中,输入信号datainF和datainG表示模拟方位和高低编码器回传的串行数据信号,clkyiw、dhao和clear表示同步脉冲发生块产生的移位、锁存和清零信号。从如下仿真的输出信号 Gout[15:0]和 Fout[15:0]输出波形图看出,该模块的设计达到了预期效果。

⑤防浪墙变形缝。为避免防浪墙因温度应力或坝体不均匀沉降而产生裂缝,沿其长度方向每隔15m设一道变形缝,变形缝位置与面板接缝错开,缝内设一道橡胶止水带。

图8 数据转换模块仿真波形

3.4 数据输出控制

数据输出控制块是依据读写控制总线和地址总线,通过CPLD内部译码芯片74138译码生成对应的选通信号,数据传输期间选通对应的信号输出至数据总线上。在CPLD非数据传输期间,置数据总线的I/O口于三态,不影响处理器和系统其他部分的接口数据交换。

老年人日常照料的差序格局反映老年人在需要照料时所能够获得的资源的排序,差序格局以老年人为中心,如图1(老年人日常照顾结构)所示:各个不同角色围绕老年人中心形成一个个圈层,越靠近中心,对老年人的照料支持越大[6]。

4 结束语

火炮位置测量是火炮随动控制重要组成部分,其精确度和可靠性将直接影响到全武器系统的作战性能。该方案不同于传统的测量方法,通过实际应用证明有以下优点:数据处理速度高,测量位置的时间不大于200 μs,并且保证了所采集数据的准确性和可靠性,为处理器节省了宝贵的时间,适合于火炮随动控制;其结构实现简单,价格较传统实现低,具有经济价值和实用性。

[1]张卫宁.TMS320C280x系列DSP的CPU与外设[M].北京:清华大学出版社,2004.

[2]赵曙光,预万有,杨颂华.可编程逻辑器件原理、开发与应用[M].西安:西安电子科技大学出版社,2000.

[3]候伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,2002.

[4]黄正瑾.CPLD系统设计技术入门与应用[M].北京:电子工业出版社,2002.

[5]高国燊,余文烋.自动控制原理[M].广州:华南理工大学出版社,2003.