带自测功能的DDR2控制器设计

肖侃

(上海贝岭股份有限公司 数模混合设计部,上海 200233)

DDR2(Double Data Rate two)是 DDR2 SDRAM 的简称,是目前较主流的一种DRAM存储器件[1]。与上一代DDR相比,它依然采用了在时钟的上升/下降延同时进行数据传输的基本方式,但拥有两倍的预读取能力。换句话说,DDR2每个时钟能够以4倍外部总线的速度读/写数据[2]。

与SRAM相比,DRAM的结构决定了它有着较复杂的时序要求[1](包括需要上电初始化和定时刷新等),这对于一个嵌入式系统的设计而言,是一个不小的挑战。常见的解决方法是:单独设计一个DDR2控制器将DDR2的复杂时序转化成类似于SRAM的简单时序,同时完成初始化操作以及产生刷新指令以维持DDR2中的数据。

1 DDR2控制器设计原理

DDR2有若干芯片厂家生产,但都基于JEDEC的标准,所以DDR2控制器必须也满足该标准。考虑到整个系统采用的DDR2是ELPIDA公司的EDE1116AEBG芯片,故以该型号的芯片作为样本。

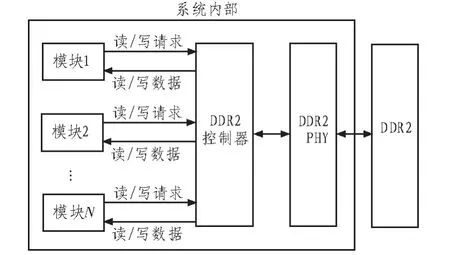

DDR2控制器作为整个系统中的一个模块,在系统中的位置如图1所示。

图1 系统框图Fig.1 System block diagram

DDR2控制器接收系统其他模块发出的读写DDR2的请求 (包括指令和地址),将其转变为DDR2可识别的控制信号;如果是读指令,待DDR2完成指令之后,将相应的读数据传输至发出请求的模块;如果是写指令,从发出请求的模块中取出数据将其写入DDR2;同时,要考虑DDR2自身的初始化和刷新等问题,保证其工作正常。

DDR2控制器与DDR2的接口部分的定义,如表1所示。

表1 控制器与DDR2的接口定义Tab.1 Interface of controller and DDR2

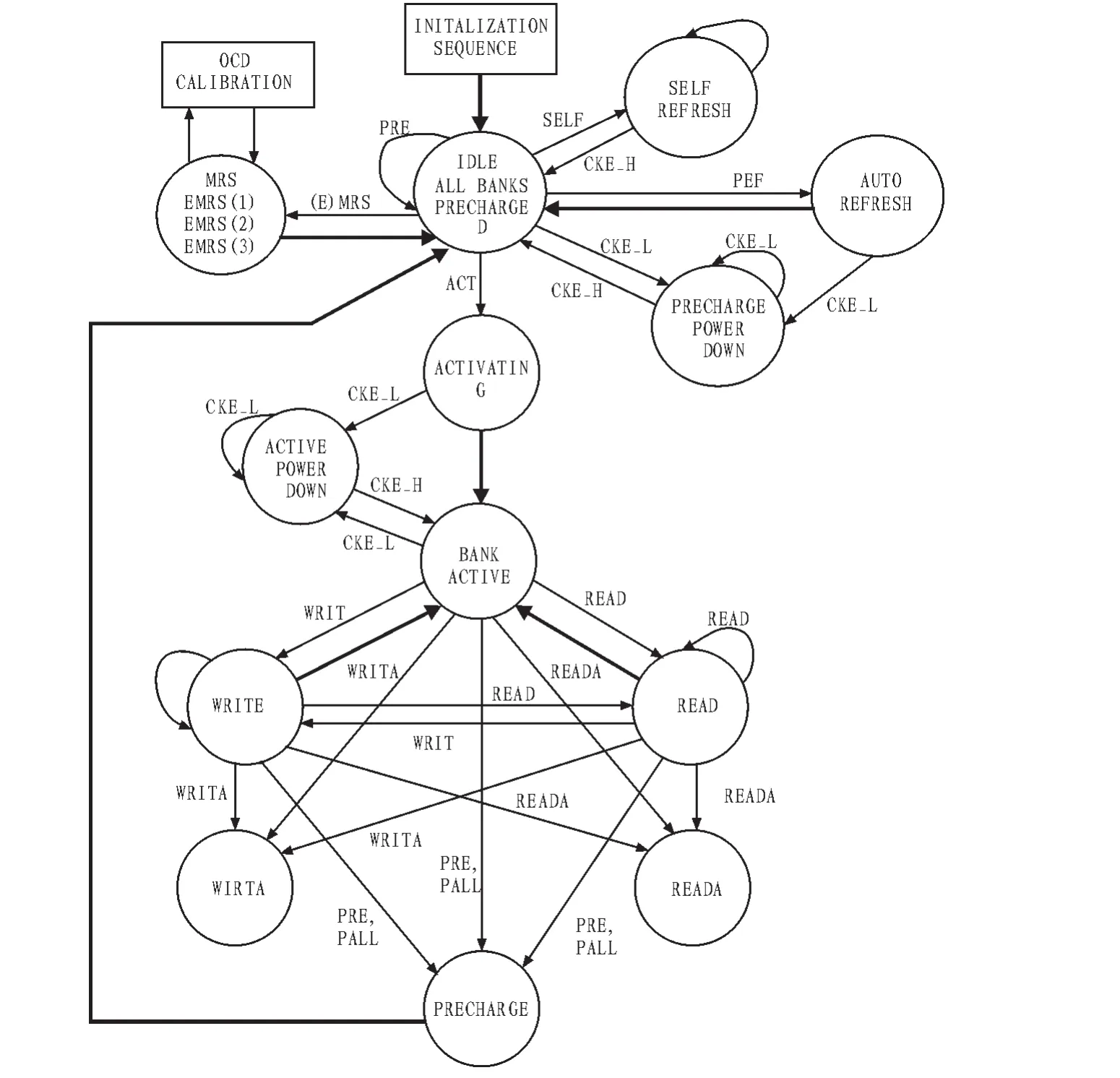

对DDR2的控制需依照JEDEC标准,有着严格的要求[3],其状态转换图(状态机)如图2所示。

在设计之初,需要考虑3个要点:

1)数据跨时钟域如何安全传输;

2)状态机如何设计;

3)如何验证。

本设计中跨时钟域的数据较多,宽度较大,所以采用了异步FIFO作为跨时钟域的接口。

状态机即控制逻辑,直接关系到设计的质量,本设计的状态机基本依照图2设计。

由于FPGA的软件可以方便的产生MCB(存储器控制块)模块和相应的testbench,该模块完全可以独立实现DDR2的控制功能[4]。只需要把本设计替换掉MCB中相应的部分,即可很方便的进行FPGA验证和仿真验证。当然,设计时要使得两者接口一致。

图2 DDR2状态机Fig.2 The finite state machine of DDR2

2 结构设计

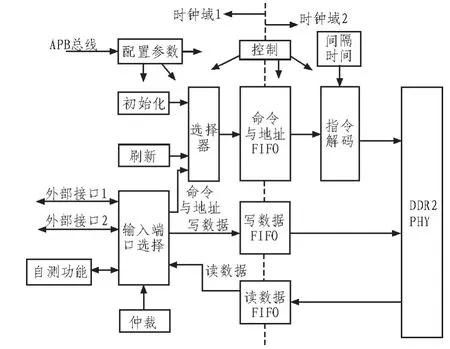

一般的DDR2控制器的设计只关注控制功能,DFT相关的事情留给DFT工程师考虑。但在某些特殊应用的情况下,比如试验性的芯片研发,需要对DDR2进行一个简单的测试,这就需要在DDR2的控制器[5-6]中集成自测功能。

如图3所示,整个DDR2控制器跨越两个时钟域,两个时钟域之间的通讯采用异步FIFO实现,共分为3个异步FIFO, 即 “命令与地址 FIFO”、“写数据 FIFO”、“读数据FIFO”。参数通过APB总线配置到模块内部,用以灵活控制模块功能。“初始化”是上电后的必要步骤,从硬件实现的角度看,初始化是按照要求发出一系列的指令。“刷新”的实质是一个计数器,定时向“命令与地址FIFO”发送刷新指令。外部接口指的是和外部模块的接口,本设计中共有两组外部接口。“指令解码”的作用是将指令转化为DDR2的具体控制信号。“间隔时间”用于控制指令与指令之间的时间间隔,这些时间间隔均需要符合标准。“自测功能”即产生一系列的写指令,将相关数据写入DDR2,然后再从DDR2中将这些数据读出,如果写入和读出的数据能够匹配,即认为DDR2基本功能正常。

图3 DDR2控制器结构图Fig.3 Structure of DDR2 controller

如果没有“自测功能”,也需要仲裁和输入端口选择等子模块;将“自测功能”置于与外部接口同等的位置,只需要增加很少的开销,即可实现自测功能。

经过性能/面积等综合考量,本设计采用了MARCH C+算法来实现“自测功能”。

图4 MARCH C+算法的状态机Fig.4 Finite state machine of MARCH C+

W0是指写入0;R0是指读出0;W1是指写入1;R1是指读出1;max是指地址最大,否则地址加1;min是指地址最小,否则地址减1。

为了使设计更加灵活,本设计可通过寄存器设置,来简化算法或使算法更复杂。比如:DDR2的位宽是16 bit,第一次执行 MARCH C+算法时,写入 16 bit的 0或 16 bit的 1;如果想使算法更加复杂,测试覆盖率更高,可以在第一次算法执行结束后,第二次执行算法,这时写入16 bit的数据为0000000011111111或1111111100000000。以此类推,可以较自由的调节测试时间和测试覆盖率之间的矛盾。

完成结构设计之后,用verilog语言完成了RTL描述[7-8],并通过仿真和FPGA验证。在200 M主频下,数据传输速率达到3.1 GB/s。与不增加自测功能的设计相比,本设计在综合后面积增加不到10%。

3 结 论

文中为了解决项目中的特殊需求,创造性的提出一种新型DDR2控制器的结构,无需增加太多开销,即可灵活的实现自测功能。该设计为相关设计提供了实例,具有良好的参考和应用价值。

[1]舒展.DDR控制器IP的设计与FPGA实现[D].合肥:合肥工业大学硕士学位论文,2009.

[2]夏军,庞征斌,李小芳,等.一种高性能DDR2控制器的设计与实现[J].计算机工程与科学,2010,7(7):1-3.

XIA Jun,PANG Zheng-bin,LI Xiao-fang,et al.Design and Implementation of a High-Performance DDR2 Controller[J].Computer Engineering&Science,2010,7(7):1-3.

[3]张凌.基于FPGA的DDR2 SDRAM控制器的设计与实现[D].北京:北京航空航天大学,2009.

[4]须文波,胡丹.DDR2 SDRAM控制器的FPGA实现[J].江南大学学报,2006,5(2):1-4.

XU Wen-bo,HU Dan.Implementation of DDR2 SDRAM controllerin a FPGA[J].JournalofSouthern Yangtze University,2006,5(2):1-4.

[5]王江荣,刘伟.基于Haar小波的一类模糊控制器的优化及应用[J].工业仪表与自动化装置,2011(5):30-32,49.

WANG Jiang-rong,LIU Wei.Haar wavelet-based fuzzy controller for a class of optimization and application[J].Industrial Instrumentation&Automation,2011(5):30-32,49.

[6]余萍.基于动态线性化方法的自适应PD控制器的设计[J].工业仪表与自动化装置,2012(1):32-34.

YU Ping.The design of adaptive PD controller based on dynamic linearization method[J].Industrial Instrumentation&Automation,2012(1):32-34.

[7]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

[8]赵倩.Verilog数字系统设计与FPGA应用[M].北京:清华大学出版社,2012.