C波段高增益放大器的设计

赵子岩,齐 敏,齐 榕,家建奎

(西北工业大学 陕西 西安 710129)

近年来随着通讯技术的急速发展,微波单片集成放大电路(MMIC)因其体积小、可靠性高、一致性好[1]等优点,已经越来越多的应用于各种无线通信系统中。MMIC主要应用于通信系统的发射机和接收机中,是各类微波接收系统前端的关键电路,故对其的研究也越来越深入。本文通过研究C波段高增益放大器的设计方法,设计了一个二级放大电路,其具有高增益的特点,满足通信系统的需要。

放大器的设计是相对比较复杂的,并且每种放大器用途不同,其各项指标也是不一样的。同时,一种放大器的各个指标有时是相互冲突的,因此在设计时一般要折中考虑,各方面都得兼顾。所以,在设计的时候需要考虑所使用的环境和要求,在此基础上进行相关的设计。

1 电路整体结构的设计

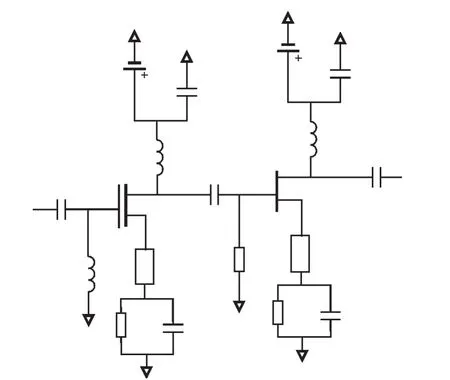

放大电路整体结构图如图1所示。

为了得到足够大的放大效果,整体放大电路采用二级放大的形式,如图1所示,其主要包括偏置电路、匹配电路等。偏置电路的作用是给放大器提供一个最佳的静态工作点,使放大器处于一个正常的工作状态,能够正常实现放大器的放大功能。同时,为了使信号更好的传递给下一级或者输出,必须在电路中加入匹配电路,另外一个就是它能够避免因不匹配而造成放大器的损坏,其重要性在放大电路中的作用是至关重要的。

图1 电路整体结构图Fig.1 Overall structure diagram of the amplifier circuit

2 偏置电路的设计

偏置电路决定着放大器的工作状态,合适的偏置电路会使放大器的工作状态更加稳定。砷化镓FET是由栅极电压控制漏极电流的,所以跨导的大小对漏极电流影响是很明显的,漏极电流越大也更容易产生自激。而大功率器件有很大的栅极外围和很大的跨导,因此偏置电路设计的好坏直接影响着放大器性能[2]。栅极电阻应尽可能靠近器件的栅极以进行静电保护和防止自激振荡。偏置电路和输入匹配电路是并联的,在基频上的阻抗应该是无穷大。由于栅极电流很小,所以第一级l/4波长高阻线的特性阻抗可以取值很高。然而,为了减小栅极电阻的直接并联对主输入电路的阻抗的影响,通常将偏置电路作为匹配电路的一部分,表现为一个阻抗为Z=j*Zotanθ(假设损耗很小)和输入匹配电路并联[3]。

栅极偏置电路中栅极电阻取值是很重要的,甚至会影响到器件是否能稳定工作。栅极电阻不是栅极偏置电路中直接连接到器件栅极的那个电阻,而是还应该包含其它电阻在内的总的一个等效电阻。如果漏极电路用做匹配电路的一部分,第一节线的长度应小于90度,该电路的阻抗为Z=j*Zotanθ(假设为低损耗),和输出匹配电路并联。如果该电路的功能仅是提供偏置,则θ=90°,其特性阻抗为无穷大。在第一节微带线的末端和地之间,并联去耦电容和一个电阻串联电路。这个电路中引入一个有耗元件和去耦电容并联,以改善放大器的稳定性[4-5]。

3 匹配电路的设计

阻抗匹配网络的设计是成功设计固态高效功率放大器的关键。如果电路匹配不佳,微波功率不能很好地传送到负载而是反射回来,甚至会产生振荡,导致晶体管烧毁。输入匹配网络是用来实现晶体管输入端口与信号源之间的匹配,它把晶体管呈现的复数阻抗变换为与信号源阻抗共轭匹配[6](即50 Ω电阻性的源阻抗),以获得最大功率增益匹配。输出匹配网络用来完成晶体管的输出端口与负载之间的匹配。

在获得了功率管大信号参数的基础上便可进行匹配电路的设计。由于大多数功率放大器都有带宽的指标要求,因此,匹配电路的设计应能满足放大器的带宽要求。典型的宽带匹配电路形式有:多节并联导纳匹配、渐变线阻抗变换器、四分之一波长多阶梯阻抗变换器、变阻滤波器阻抗变换器等。

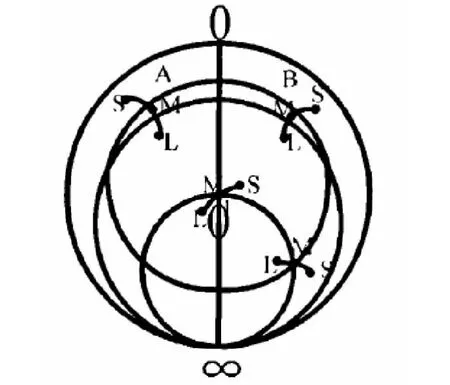

文中匹配电路的设计主要是采用多节并联导纳匹配法,多节并联导纳匹配法的设计思路如下:首先,测出晶体管在不同工作频率上的导纳值,再将测得的这些导纳值都描述在导纳圆图上;其次按频率顺序由低至高,将导纳值连成一条曲线。设计时根据此曲线形状选用多个并联电纳,从不同位置接入,以在宽频带内实现共轭匹配。

宽频带的共轭匹配一般通过Smith圆图法,如图2所示,晶体管在中心频率点导纳值为M,高频端导纳值为S,低频端导纳值为L。从弧线LMS,我们可以看出,若先接入微带线,让导纳曲线直接向信号源方向转,则L点更落后于S点,起不了压缩作用。因此,我们可在晶体管的输入端(或输出端)并接一容性电纳,使导纳曲线沿等电导圆往右移动,弧线LMS从A区转到B区,这时频带内,高、低端导纳值相对变化不同,如图中所示。这时再使L、M、S各点沿各自的等驻波系数圆向信号源方向移动到电导的单位圆附近。然后,并接一个感性电纳,就可将导纳值曲线移到圆图的1+i*0点附近达到匹配[7-8]。

图2 多节并联导纳匹配原理图Fig.2 Multiple parallel admittances matching

4 仿真与实际测量分析

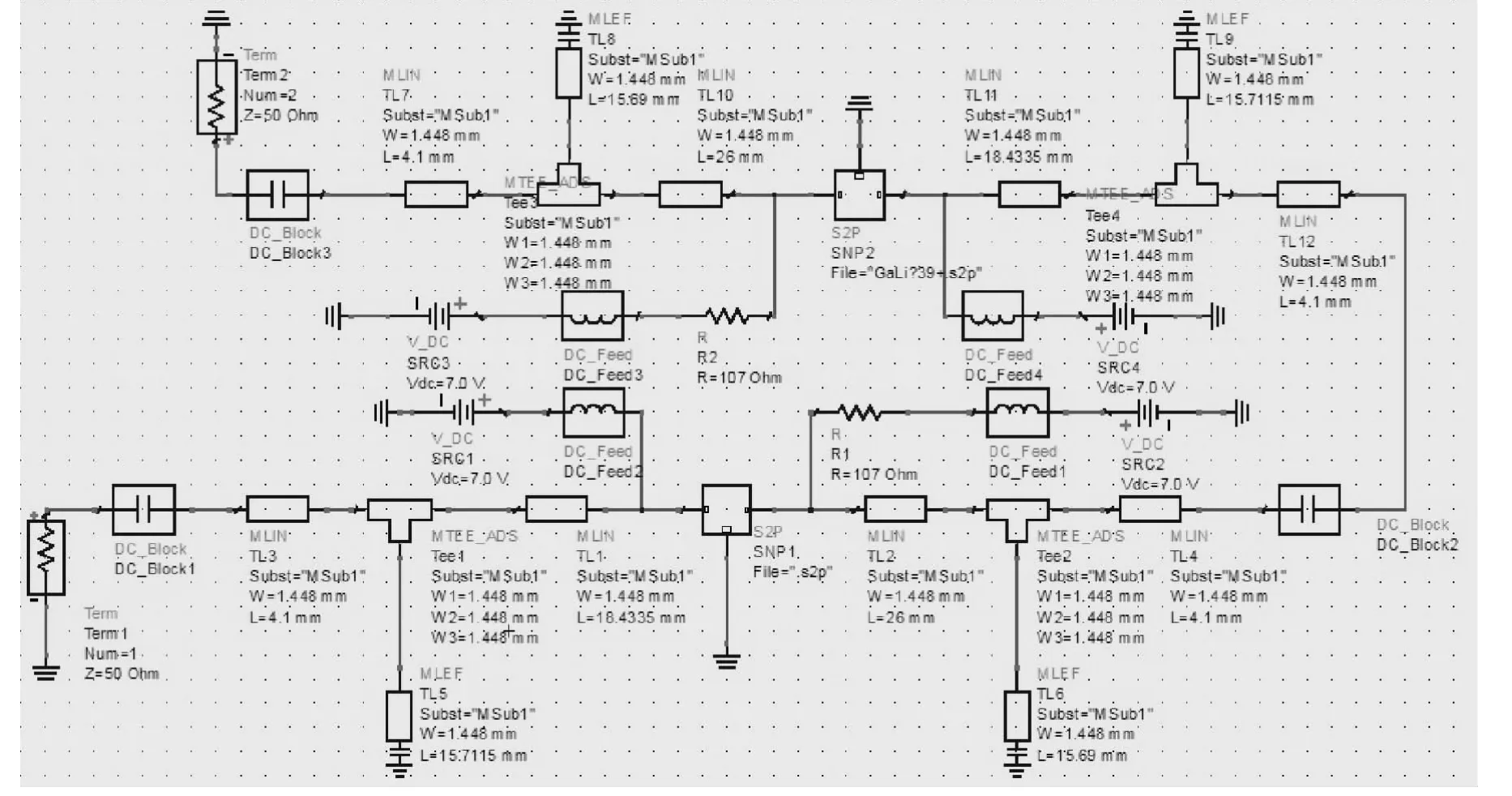

在做实物之前,本电路运用了ADS软件进行了仿真。为了使整个电路达到预期的效果,在此之前对放大器的匹配电路和偏置电路进行了仿真计算,计算出了各个微带线的尺寸。仿真电路图如图3所示。

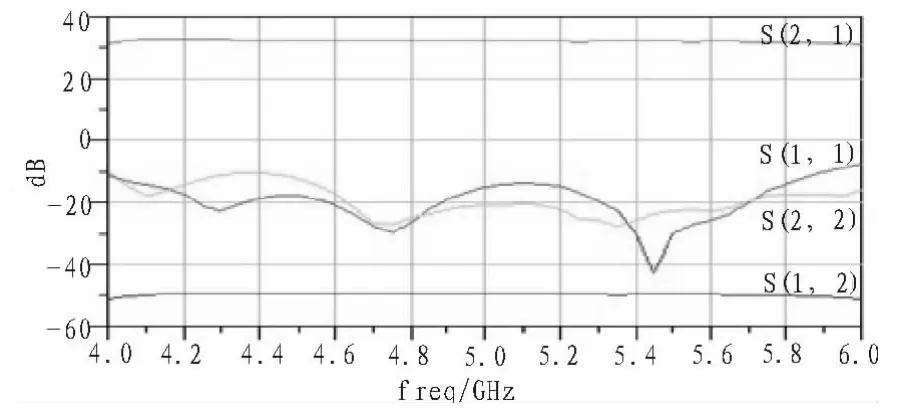

仿真结果如图4所示。

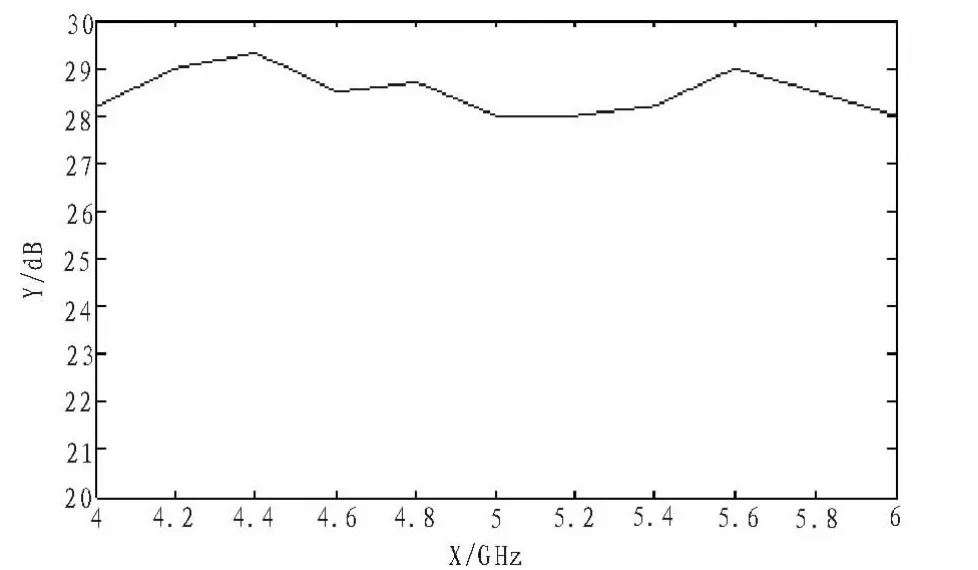

在实测时主要测量了电路的增益,实测结果如图5所示。

通过仿真结果和实测结果可知,C波段高增益单片功率放大器的设计增益为15 dB,而实际单片电路增益的测试结果略小于15 dB,对比图5中曲线,可以看出测试结果与放大器的设计增益比较吻合。

5 结 论

文中采用GaAs基InGaP HBT MMIC工艺制作了C波段高增益功率单片放大器。在本单片电路设计中,着重考虑放大电路的增益。经过实际测试,测量了电路的放大指标,对比测试结果和仿真结果来看,增益系数的测试值和仿真值相差不到6%,达到了设计要求。

[1]刘志军,高学邦,吴洪江.C波段高增益低噪声放大器单片电路设计[J].微纳电子技术,2009(7):437-440.

LIU Zhi-jun,GAO Xue-bang,WU Hong-jiang.Design of C-band High-gain low noise amplifier[J].Micronanoelectronic Technology,2009(7):437-440.

[2]邢靖.C波段固态功放设计和实验研究[J].现代雷达,2005(6):59-62

XING Jing.Design and experimental research of solid-state power amplifier[J].Modern Radar,2005(6):59-62.

[3]郑新,赵玉洁.微波同态电路设计[M].2版.北京:电子工业出版社,2006.

[4]张永慧.脉冲C类固态放大器中偏置馈电电路的研究[J].中国科技信息,2005,6(13):29.

ZHANG Yong-hui.The study of pulse C class I division in the amplifier offset feed circuit[J].Information Science and Technology of China,2005,6(13):29.

图3 仿真原理图Fig.3 Simulation diagram

图4 仿真结果Fig.4 Simulation result

图5 实测结果Fig.5 The measured results

[5]李红萍,马应魁,李泉,等.基于89C54的可控放大器设计[J].工业仪表与自动化装置,2013(1):82-84.

LI Hong-ping,MA Ying-kui,LI Quan,et al.A controllable amplifier design based on 89C54[J].Industrial Instrumentation&Automation,2013(1):82-84.

[6]袁孝康,王仕蹯,朱俊达.微带功率晶体管放大器[M].北京:人氏邮电出版社,1982.

[7]清华人学微带电路组编.微带电路[M].北京:人民邮电出版社,1976.

[8]朱素杰,周波,刘忠艳.一种基于相位的立体匹配算法[J].工业仪表与自动化装置,2013(2):101-104.

ZHU Su-jie,ZHOU Bo,LIU Zhong-yan.A phase-based stereo matching algorithm[J].Industrial Instrumentation&Automation,2013(2):101-104.