一种占空比可调的新型整数半整数分频器设计

靳 钊,乔丽萍,王聪华,王江安,郭 晨

(1.长安大学信息工程学院,陕西 西安 710064;2.西藏民族学院信息工程学院,陕西 咸阳 712082)

责任编辑:魏雨博

随着大规模集成电路、计算机网络以及全球化商业模式的发展,射频识别(RFID)技术得到了迅速发展,并被列为21世纪最有前途的重要产业和应用技术之一。在我国正在大力推进的物联网[1]建设中,RFID标签作为信息载体,在整个物联网系统中占据重要的地位,在物流、交通、安全等各个行业有着广阔的应用前景。在RFID标签芯片的数字逻辑电路设计中,分频器是一种重要的电路组成部分。分频通常包含整数分频和小数分频,但一些电路中并不只包含一种频率或一种占空比的时钟,如超高频RFID 的国 际标 准 ISO/IEC 18000—6C[2]和 EPCglobal Class1 Gen2[3]中,规定RFID标签的反向散射频率在40~640 kHz范围内变化,这就要求标签可以根据输入控制实时产生特定频率的编码时钟。在一些高频电源开关控制中也对多种占空比提出了要求。

任意数分频电路可由模数混合方式实现[4],但模数混合电路相对复杂,纯数字的分频电路得到了越来越多的应用,本文在分析常见分频电路的基础上,通过改进与优化,设计了一个新型通用分频器,该分频器支持整数和半整数分频,且占空比全范围可调,保证了电路时序和功能稳定可靠。该分频器通过FPGA硬件平台验证,给出了几个特征分频点的仿真波形,证明了设计的正确性和可行性。

1 分频原理

1.1 整数分频

整数分频可分为偶数分频和奇数分频。偶数分频通常可以通过计数器实现[5]。例如要对一个源时钟进行2K分频,则使用一个模2K计数器即可实现。分频关键参数如下

式中:mod_cnt为计数器模值;reverse_cnt为翻转输出时钟时的计数值;duty_cycle为所得到的分频时钟占空比。特别地,X取K-1时翻转输出时钟,如此循环即可得到占空比为50%的2K分频时钟。

奇数分频的原理[6-7]和偶数分频一致,只是计数器的模值做相应改变。如对源时钟做2K+1分频,分频关键参数如下

1.2 小数分频

在小数分频的设计中,目前广泛采用的方法是双模前置方式[8-9],通过设计两个不同分频比的整数分频器,控制单位时间内两种分频比出现的不同次数,从而在总体的平均意义上获得一个小数分频。例如前置m次分频系数D1分频,n次D2分频,则最终可以得到的分频系数为

从小数分频的原理可以看出,由于分频器的分频值在不断交替改变,分频后得到的信号抖动比较大。所以在对时钟相位敏感的设计中任意小数分频使用较少。

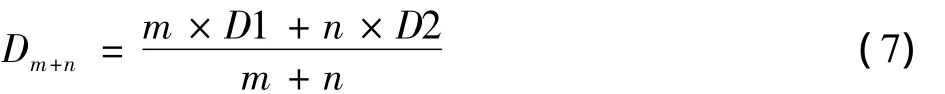

1.3 半整数分频

常见的半整数分频原理[10]如图1。基本设计思想是:对于进行K-0.5分频,首先进行模K的计数,在计数到K-1时,输出时钟置为1,下一个时钟沿计数器恢复0值,输出时钟变为0。即当计数值为K-1时,输出时钟才为1。如果计数值K-1对应着半个输入时钟周期时,将计数器值置为0,并将输出时钟置0,则输出时钟高电平时间只有半个输入时钟周期长度,即实现了K-0.5分频时钟。要保证这个特殊的半个周期时钟,采用K-0.5分频信号的2分频信号与输入时钟异或,反转输入时钟,将下一个触发时刻提前半个周期,相当于扣除掉了半个输入时钟周期。

图1 半整数分频器原理图

2 提出的通用分频器

2.1 电路设计

从上述半整数分频原理不难看出,clk_div2刚好是50%占空比的2 K-1分频时钟。进一步分析发现,如果在异或门上加上使能信号,当使能信号开启时,即是上面讨论的K-0.5半整数分频电路,当使能信号关闭时,计数器跟随输入时钟翻转,不会出现半个周期计数值的情况,即可实现K整数分频,同理在clock_div2处额外的得到了2K偶数分频。如果模K计数器的模值和输出波形翻转的位置可以通过用户输入参数实时设定和改变,即分频时钟的分频系数和占空比根据输入实时改变,则电路的实用性将大大提升。

图2 改进的通用分频器原理图

基于这一思路,本文对半整数分频电路进行改进和优化,设计了如图2所示的通用分频器。该分频器有4个输入,1个输出。其中M为分频系数的整数部分,理论取值为[1,∞),本文取4位位宽为例;N为分频系数小数部分,位宽为1,“0”表示整数分频,“1”表示半整数分频;H为占空比控制参数,表示分频时钟高电平所占原始时钟的周期数,位宽一般和M一致,取值为[1,M+N)之间的整数。例如(M,N,K)=(4,0,2)即表示4分频,占空比要求50%。

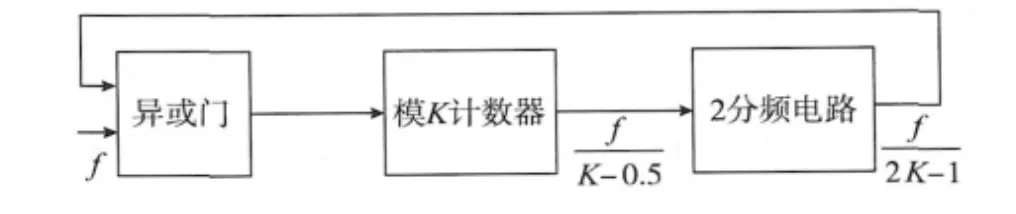

下面以2.5分频为例详细说明电路的工作原理和过程。分频器输入 (M,N,H)=(2,1,1),要求分频执行2.5分频,高电平占一个源时钟周期。输入处理电路首先对输入参数进行判断和处理,此处N为1,即要求半整数分频,则给出使能信号开启异或门。输入的分频系数为2.5,则预置变模计数器模值为M+N=3,并置最大计数值max_cnt为3-1=2。占空比要求高电平为1个源时钟周期,将计数器分频时钟clk_cnt翻转点设为H=1,当异或时钟clk_xor上升沿采样的计数值小于此值时,时钟输出高电平。clk_xor由低到高翻转,触发二分频电路输出时钟clk_div2由低到高翻转,由于电路自身的延迟,clk_div2的相位会比输入源时钟clk_in相位滞后,然后clk_div2和clk_in二者异或,在clk_in反转同时,产生一个窄脉冲,由此窄脉冲下降沿控制计数器计数值加1,从而在下一个clk_xor时钟上升沿时,采样到计数值1,随即翻转clk_cnt。如此循环即可得到2.5分频时钟,NC-Verilog仿真波形见图3。

图3 2.5分频软件仿真波形(H=1)(截图)

2.2 时序优化

为了提高电路时序的可靠性,采用了下降沿计数,上升沿采样计数值翻转输出时钟,以保证采样时有足够的建立保持时间。

其次关于图3中clk_xor的窄脉冲,由波形可以看出在半整数分频时,时钟异或出现的窄脉冲的主要功能是上升沿采样计数值,下降沿将计数值递增,目的是保证在下一个时钟上升沿来时,能正确采样到新计数值而决定输出时钟是否翻转。可以看出理论上只要小脉冲下降沿处在半个源时钟周期内,就能保证电路功能。所以为了进一步保证电路功能,规避此小脉冲可能受到干扰后对电路功能带来影响,将二分频电路的输出经过一定的延迟,再送入异或门运算,如图2中的延迟单元BUF。具体延迟值根据源时钟脉冲大小而定。这样处理后,电路时序更加稳定可靠,健壮性更强。

2.3 占空比调整

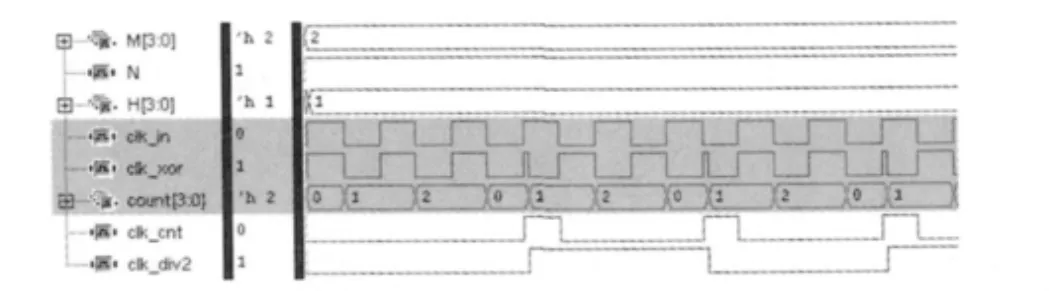

分频器的输入H为占空比调整参数,H的值控制输出时钟不同的相位翻转时刻,可实现不同的分频占空比。同样以上述2.5分频为例,将分频器占空比调整参数H由1改到2,即要求分频时钟高电平占两个源时钟周期,仿真波形见图4。

图4 2.5分频软件仿真波形(H=2)(截图)

不难发现图3、图4中,clk_cnt高电平都比预设值少了半个周期,并非和所设H参数一致。对于占空比调整参数H,需要补充的是:对于偶数分频H的值即准确反映高电平的周期数,而对于奇数和半整数分频H-0.5才是高电平的周期数,这分别和半整数分频中的脉冲扣除,奇数分频的占空比调整有关。特别地,当取得H≥(M+N)/2的第一个整数时,对于整数分频,占空比为50%;对于半整数分频,不能做到完全的50%,高电平与低电平相差半个周期。这存在一个规律:1)若是M为偶数的半整数分频,则高电平比低电平多半个周期,占空比≥50%;2)若是M为奇数的半整数分频,则高电平比低电平少半个周期,占空比≤50%;3)当整数部分越大时,占空比越趋近于50%。具体波形可参见下一节FPGA硬件验证结果。

另外,H参数取值为[1,M+N)之间的所有整数。且随着M+N的增大,H的取值也会越多,对应的占空比调整步长也越小,所以理论上本分频器的占空比调整跨越了几乎整个M+N分频系数下合法占空比的取值范围。

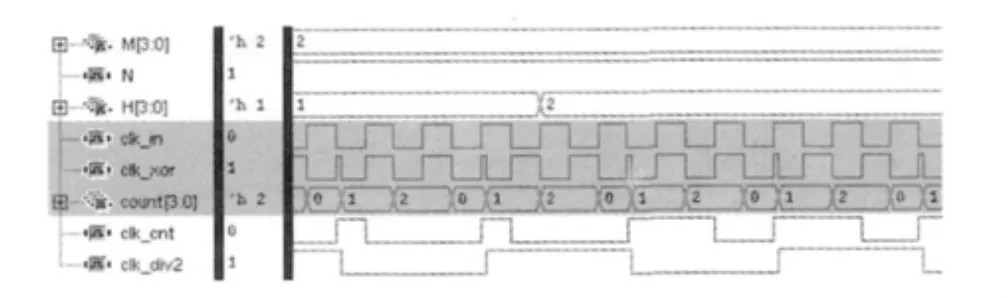

3 FPGA仿真实现及验证

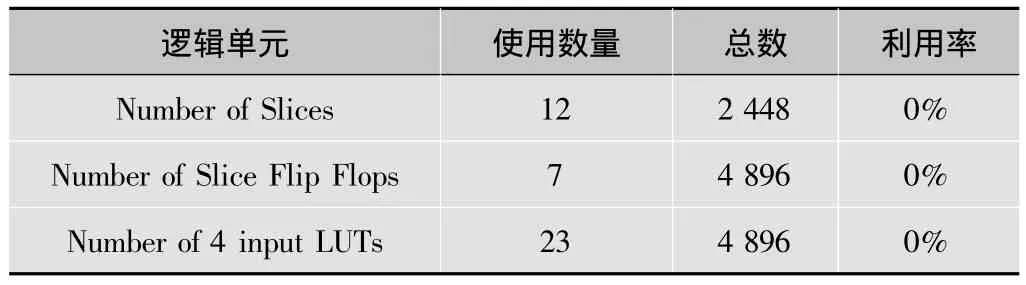

提出的分频器电路由Verilog HDL语言实现,顺利通过NC-Verilog软件仿真后,采用Xinlinx公司的ISE开发环境综合并下载到SPARTAN XC3S250E芯片上,通过ISE软件内嵌的逻辑分析仪ChipScope软件进行仿真验证。FPGA综合资源利用情况如表1所示。表1的7个寄存器中,有4个是被4位宽的计数器所占用,这是由用户可输入的分频控制参数M的位宽所决定的,而其余电路控制结构只使用了3个寄存器,可以看出整个电路占用资源很少。

表1 FPGA综合利用情况

本文分频系数M位宽为4,N位宽为1,所以选取了从1~15.5的多个具有代表性的分频系数和占空比参数进行测试。仿真结果表明电路功能和设计功能一致。另外分频系数越大,可选择的占空比调整范围越宽,如果在时钟输出端再加入一级反相器,则可能获得更多的占空比选择。例如5分频占空比为10%,30%,50%,70%,经过反相可以增加占空比为90%的选择。图5给出了部分分频系数下的FPGA测试波形,图中可以看出不同占空比效果。其中占空比的值为一个输出时钟周期内高电平所占输入时钟周期数和低电平所占时钟周期数的比值,图中以小数表示。如1.5分频中,一个clk_out周期高电平对应0.5个clk_in周期,低电平对应1个clk_in周期,所以占空比为0.5/1.5=33.3%。

图5 FPGA硬件测试波形(截图)

4 小结

本文提出一种基于半整数分频电路改进的通用分频器设计,能根据用户输入分频系数和占空比参数实时产生相应的分频时钟。电路支持整数分频和半整数分频,支持50%占空比,占空比全范围可调。对该电路时序上的处理优化,确保了电路时序可靠,功能稳定,并且电路结构简单,占用资源极少,具有很强的通用性和可移植性。

[1]游晓黔,周韫艺.可信物联网的研究[J].电视技术,2012,36(14):24-27.

[2]IS0/IEC18000—6,Radio Frequency for Item Management Part 6:Parameters for Air Interface Communications at 860 MHz to 960 MHz[S].2006.

[3]EPC radio-frequency identify protocols Class 1 Generation2 UHF RFID tag:Protocol for communications at 860 Mhz-960Mhz[EB/OL].[2012-10-30].http://www.epcglobalinc.org/home.

[4]KRISHNAPURA N,KINGET P.A 5.3 GHz programmable divider for HiPerLAN in 0.25μm CMOS[J].IEEE J.Solid-State Circuits,2000,35(7):1019-1024.

[5]郭桂良,赵兴.一种新型小数/整数分频器[J].微电子学,2008,38(3):420-423.

[6]高清运,李学初.CMOS高性能奇数分频器的设计[J].电子学报,2004,32(5):869-870.

[7]TIAN Hongli,SHI Shuo,ZHANG Jun.Controllable arbitrary integer frequency divider based on VHDL[C]//Proc.International Joint Conference on Artificial Intelligence,2009.[S.l.]:IEEE Press,2009:691-694.

[8]曾健平,谢海情,晏敏,等.高性能双模前置分频器设计[J].半导体技术,2007,32(1):65-67.

[9]何小虎,胡庆生,肖洁.0.18 μm CMOS PLL频率综合器中可编程分频器的设计与实现[J].微电子学与计算机,2007,24(5):61-65.

[10]白雪皎.基于CPLD半整数分频器的设计[J].长春大学学报,2006,16(1):13-15.