面向视频流的畸变矫正算法的FPGA实现

徐 晓,谢时岳

(华南理工大学理学院,广东广州 510641)

面向视频流的畸变矫正算法的FPGA实现

徐 晓,谢时岳

(华南理工大学理学院,广东广州 510641)

本设计用一款中低端的FPGA——Altera公司的EP3C40来实现一种通用的畸变矫正算法,主要用于对成本要求低、实时性要求高的视频流图像处理系统中的前端处理部分。FPGA具有强大的并行处理性能,因此相比PC处理平台或者DSP处理平台,FPGA更能保证视频流的实时性。经实际验证,该方法能达到畸变矫正的实时性要求。

FPGA;畸变矫正;实时性

【本文献信息】徐晓,谢时岳.面向视频流的畸变矫正算法的FPGA实现[J].电视技术,2013,37(13).

理论上定义的摄像机透镜是不引入任何畸变的,然而在现实生活中,不可能制造出完美的透镜,这主要是制造上的原因,因为制作一个“球形”透镜比制作一个数学上理想的透镜更容易。摄像机镜头畸变会导致摄像机成像面(即投影平面)上的坐标失准,直观上看就是拍摄出来的物体会有变形,而图像坐标准确性会直接影响图像的配准以及三维坐标重建等问题[1]。如今对于图像畸变矫正主要还是对于单幅或多幅静态图片的畸变矫正,而对于视频图像的畸变矫正方案较少。视频流图像矫正是基于静态图像畸变矫正的方法,加入了对图像处理实时性的要求和大数据量搬运和存储的要求,尤其对于高清视频流的矫正,实时处理的数据量非常大。目前市场上通常会选择用DSP或者FPGA为核心的图像处理系统来完成对视频流畸变的矫正。FPGA以其强大的并行处理能力著称,内部拥有非常丰富的时序逻辑单元[2],非常适合处理一些并行性强,但复杂度不高的简单算法,因此是处理视频流畸变矫正这种简单并行算法的最佳选择。对此,本文提供了一种使用目前市场上中低端FPGA产品Altera公司的EP3C40来进行视频流的图像畸变矫正方案。

1 畸变矫正系统硬件电路原理框图

如图1所示,基于FPGA的畸变矫正硬件系统主要由以下3个主要模块组成:1)视频数据编解码模块;2)DDR2存储器控制模块;3)畸变矫正模块。

图1 畸变矫正系统硬件电路原理框图

CCD摄像机输出的彩色电视信号经过视频解码器后以8 bit BT656(4∶2∶2)YCbCr SDTV(标清)数字视频信号格式存入DDR2存储器,当DDR2内存满一帧图像后(一帧图像共576行有效视频数据),畸变矫正模块开始从DDR2存储器中读取数据进行矫正工作,一次矫正一行有效视频数据,矫正后的一行图像数据存储在双口RAM(DPRAM)中作为缓存,最后DPRAM中的数据通过视频编码器后转化成PAL制式的电视信号在显示终端上输出[3]。

2 视频数据编解码模块

视频编解码模块主要由I2C控制模块和有效视频信号采集模块组成。视频编解码器分别通过I2C总线进行内部模式寄存器的配置,设置上电后的参数。

在本方案中,视频解码器TVP5150采用8 bit的BT656(4∶2∶2)YCbCr格式输入数字视频信号。电视信号采用隔行PAL制式。图像帧的图像分辨率为720×576。每场数据由288行行数据组成,每行数据包括EAV,SAV,行消隐信号和有效视频信号数据4个部分,具体格式如表1所示。

?

每行有效视频数据包含1 440 byte的Y,Cb,Cr数据,其中,亮度信号Y占720 byte,色度信号Cb,Cr各占360 byte。而每帧的有效视频数据为576行×1 440 byte共829 440 byte(810 kbyte),是本系统要进行存储和处理的一帧原始有效视频图像。

本系统用FPGA构建有效视频信号采集模块,目的是把每一帧的有效视频提取出来,以供畸变矫正模块使用。

2.1 有效视频信号采集子模块

视频数据编解码模块的子模块中的有效视频信号采集子模块能够准确地从TVP5150的输出端提取每一行的有效视频数据,时钟频率为27 MHz,同时给顶层的畸变矫正模块输出1个1位的信号ActiveVideo_flag,这个信号在解码器输出有效视频数据时为高电平,在输出非有效视频数据(例如EAV,SAV,场消隐信号等)时为低电平。视频编码器ADV7179内部设置了把SAV和EAV编码作为同步信息的软同步方式,因此ADV7179的同步信号输出管脚HSYNC,FIELD/VSYNC和BLANK悬空即可。有效视频信号采集子模块也采用了软同步的方式对有效视频数据的行进行了跟踪,即需要找到帧头并设置1位帧头标记,并把这1位帧头标记保存在FPGA内部的寄存器中,同时设置一个行计数器,从遇到帧头标记开始计为第0行,以后每遇到一个新的有效视频行的时候,计数器加1,共计数576行,循环计数,这样就可以控制FPGA对每一帧中特定行进行操作。找到帧头的具体方法是每当SAV编码为FF 00 00 AB,且下一个EAV的编码为FF 00 00 9D时,此时刻即可设置一个帧头标记。

2.2 DDR2存储器控制器子模块

本系统使用DDR2 SDRAM High Performance Controller v9.0 IP核来对2片外挂的DDR2存储器MT47H64M16进行配置,DDR2存储器负责将每一帧的原始图像数据保存下来,供畸变矫正模块使用。主要配置参数是存储器时钟周期为200 MHz,数据读写时钟为100 MHz,数据位宽为32 bit,地址宽度为26 bit,其中Bank address width为3 bit,Row address width 为 13 bit,Column address width 为10 bit。传输模式采用突发传输模式,拍数为4拍,突发传输方式为连续型,因此实际一次读写32 bit×4=128 bit数据。CAS Latency设为3个时钟周期,刷新间隔为7.8 μs。参数的配置均遵照MT47H64M16的器件手册以及Altera公司关于DDR2控制器的IP核用户手册进行配置,硬件测试DDR2读写正常。

3 畸变矫正模块

摄像机畸变矫正是在求解出相机投影矩阵的前提下,利用畸变模型(变换函数)将实际的图像点平面映射到理想图像点平面。核心的问题是选择一个合适的畸变模型并求解出畸变模型的各项参数。其中对成像影响最大的是透镜的径向畸变和切向畸变。要求取摄像机的投影矩阵和畸变参数,首先需要进行摄像机标定。

3.1 摄像机的标定

摄像机标定[4](Camera Calibration)的过程简单来说就是给摄像机建模的过程,用数学的方法来建立摄像机的自然单位(像素)和物理世界单位(米)的关系。过程中能得到摄像机的几何模型和透镜的畸变模型,这两个模型共同定义了摄像机的内参数。因为对于某一个特定的摄像机,几何模型和畸变模型是不会改变的,因此可以利用计算机计算出该摄像机的内参数(几何模型的参数)和畸变参数(畸变模型的参数),然后再使用这些内参数通过FPGA的畸变矫正模块来对摄像机透镜畸变进行矫正。

对于摄像机标定的具体过程的研究,本文不作论述。正如上节所说,摄像机的标定工作最后会得出摄像机的几何模型和畸变模型,标定工作在PC上完成,软件环境是Visual C++6.0,主要运用到的库是OpenCV库,OpenCV是Intel开源计算机视觉库。对于本系统中用到的摄像机求取的内参数和畸变参数的结果如下,摄像机的型号是奥德丽公司的OCC-3105。

相机内参数矩阵:

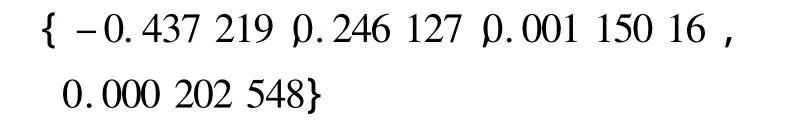

畸变系数:

3.2 畸变矫正坐标计算模块

利用上一节中的摄像机的内参数矩阵和畸变系数来计算畸变矫正坐标,由于计算出摄像机的内参数和畸变参数都是浮点数,切向畸变系数甚至只有104数量级的大小,因此计算畸变坐标时应全部用浮点计算来保证计算精度。本系统用到的是Altera公司Cyclone III系列的FPGA EP3C40C8,畸变矫正模块中运用的所有浮点计算单元的时钟频率均为100 MHz,小于Cyclone III器件浮点加减法模块的最高时钟频率150 MHz,因此完全在合理时钟频率范围之内。

由于计算出的畸变矫正坐标点并不一定落在原始图像的像素点上(大部分情况是落在原始图像4个像素点的中间),因此还要通过一定手段计算出畸变矫正坐标点的灰度值,常用的算法有最近邻点法,三次卷积法和双线性内插法[5]。本系统是为了验证引入畸变矫正算法在FPGA中的可行性,因此选用了较简单的最近邻点法。最近邻点法是用畸变矫正坐标点周围4个原始像素点中最靠近畸变矫正坐标的点的灰度值来作为畸变矫正坐标点的灰度值[6],显然该方法会引入最大半个像素的误差。

3.3 DDR2地址计算子模块

有了每一行的畸变矫正坐标后,就可以通过读取DDR2存储器中最靠近矫正坐标的像素点的地址(最近邻点法),来完成畸变矫正的工作。对于每一个畸变坐标对应的DDR2存储器中的原始像素点的地址,可以通过一个DDR2地址计算子模块来完成,原理图如图2所示。

图2 DDR2地址计算子模块原理图

4 系统的可行性分析及验证

4.1 DDR2读写数据的时间分析

如上节所说,本系统中DDR2的读写数据总线宽度为32 bit,传输模式为突发传输模式,突发传输长度为4,因此在FPGA内部给DDR2存储器控制模块定义的数据宽度为32 bit×4=128 bit,传输时钟设为有效视频采集子模块时钟的4倍,由于有效视频采集子模块一个时钟输出8 bit给FPGA,因此FPGA给DDR2传输数据的速度是有效视频采集速度的(128/8)×4=64倍,给畸变矫正部分留下了非常大的时间裕量。为了一次采集一行有效视频数据进行处理,有效视频数据采集子模块将未矫正的原始有效视频数据以行为单位存储到畸变矫正模块中定义的一个深度为4 096的DPRAM(双向端口RAM)中,这个DPRAM的容量可以存储两行的有效视频数据,可以用乒乓读写来使速度提高一倍。

4.2 畸变矫正模块的时间分析

计算出一个原始图像点的矫正坐标的频率为50 MHz,时间为1/50 MHz=20 ns,因此得到一行的矫正坐标的时间为720×20 ns=14 400 ns,此时间小于传输一行有效视频数据的时间((1/27 MHz)×1 440=53 333.333 ns),因此可以达到边传输原始图像,边计算矫正坐标的效果。利用上面提到的DPRAM乒乓读写思想,建立3个深度为2 048的DPRAM来存储每次矫正计算需要从DDR2存储器中读取的行、列和位区间信息。

4.3 系统实时性分析及验证

本系统将DDR2作为帧缓存器,存储当前帧有效视频数据的同时在DDR2内部缓存了上一帧的有效视频数据,畸变矫正模块用DDR2缓存的上一帧的数据来进行图像算法处理,这样实际上就引入了一帧的延时。PAL制式标准的全电视信号1 s能传输30帧图像,即延时为33 ms,满足实时性的要求。图3为Quartus II 9.0软件自带逻辑分析仪测试波形图,可以看到在有效视频数据传输的期间(即ActiveVideo_flag为高电平的时候),畸变矫正模块将矫正后的一行图像输出到输出视频缓存DPRAM(ram_40962)中,视频编码器同时读取DPRAM中的内容输出到显示器上。

图3 Quartus II 9.0内置逻辑分析仪SignalTap II实时测试波形(截图)

本系统验证了一种畸变矫正算法在市场中低端FPGA平台中的实现,合理利用和优化FPGA内部的逻辑单元和内存BLOCK RAM资源,提出了一种可用的满足实时性的、小成本的面向视频流的畸变矫正解决方案,可作为图像配准,三维坐标重建等复杂图像处理工作的基础。

:

[1]张静,秦文健,贾亮.摄像机畸变矫正研究的综述[J].科技创新导报,2011(7):5-7.

[2]吴继华,王诚.Altera FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2005.

[3]王德胜,康令州.基于FPGA的实时图像采集与预处理[J].电视技术,2011,35(3):32-35.

[4]崔莉娟,朱洪俊,王金鹏.基于畸变校正的双目立体摄像机线性标定[J].测控技术与仪器仪表,2011,37(1):84-87.

[5]牛建军,刘尚乾,姚荣辉,等.高准确度光电成像测量系统图像畸变校正算法[J].光子学报,2006,35(9):1317-1320.

[6]宋玲玲,谢洪波,陈晓冬,等.基于FPGA的MEE畸变实时校正系统设计[J].仪器仪表学报,2003,24(4):371-372.

Realization of Distortion Correction Algorithms for Streaming Video Based on FPGA

XU Xiao,XIE Shiyue

(School of Science,South China University of Technology,Guangzhou 510641,China)

It uses Altera’s FPGA EP3C40 to achieve a common correction algorithm for distortion effects,mainly used in the front-end processing part of video streaming image processing system which has requirements of low cost and real-time.Compared to the PC processing platform or DSP processing platform,FPGA can better ensure real-time video streaming because it has powerful parallel processing performance.By experimental tests,this method can achieve real-time requirements of the distortion correction.

FPGA;distortion correction;real-time requirement

TN911.73

A

徐 晓,硕士生导师,主要从事光电技术与住处技术方面的研究、工程开发和教学工作;

谢时岳,硕士生,主要从事FPGA平台下图像处理算法的研究工作。

责任编辑:魏雨博

2013-05-24