RTL 设计中的Verilog 代码风格

冯海涛,王 爽,周 刚

(中国电子科技集团公司第四十七研究所,沈阳 110032)

1 引言

每个代码编写者都有自己的编写习惯,而且都喜欢按照自己的习惯去编写代码。代码风格对综合后的硬件结构起至关重要的作用,相同功能不同风格的代码在综合后可能会产生不同的结构,具有不同的timing 和area。这就是RTL 设计工程师重视代码风格的原因所在。在这里主要讲述一下组合电路和时序电路中比较常用并需要特别注意的语句。

2 设计组合电路的代码风格

2.1 if 语句

(1)if 语句的比较条件不可以用“x”,仿真时“x”被看做unkown 而产生错误的仿真结果;综合时“x”被看做false,产生与仿真相同的错误。例如:

if(In_A[7:0]==8'b00xx11xx)D_Out=1'b1;

else D_Out=1'b0;

解决方法:

If((In _ A[7:6]==2'b00)&& (In _A[3:2]==2'b11))D_Out=1'b1;else D_Out=1'b0;

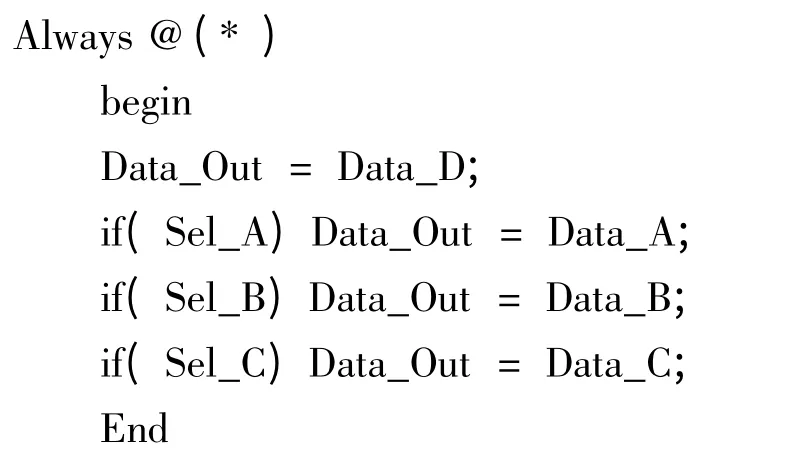

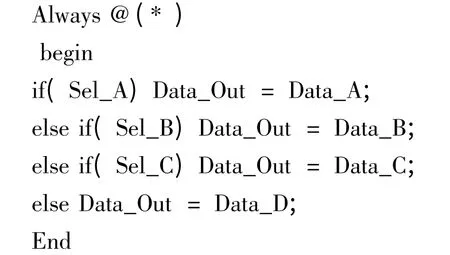

(2)if 语句优先级由下向上,越靠近下面的输入在综合时越靠近输出,如下例和图1 所示。

图1 if 语句优先级由下向上

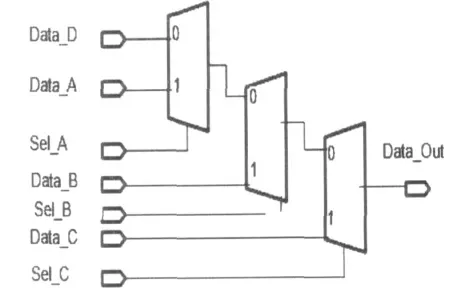

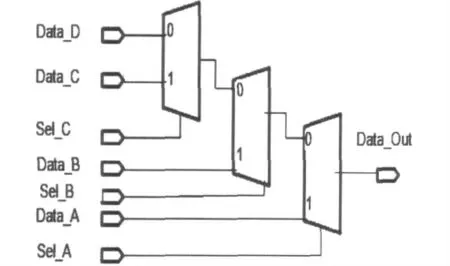

(3)if…else…if 语句优先级由上向下,越靠近上面的输入在综合时越靠近输出,如下例和图2 所示。

图2 if…else…if 语句优先级由上向下

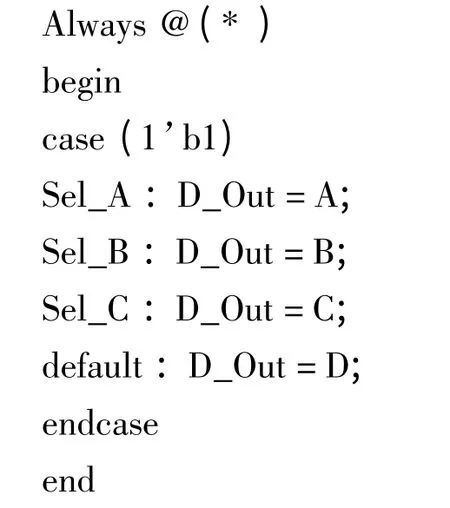

2.2 case 语句

无优先级,case的条件必须列全(full case),如果不能列全就写default 值,否则同样会产生latch。

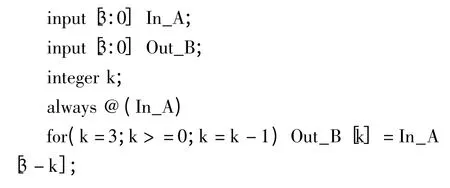

2.3 for 循环语句

for 循环语句可能被中止,而综合不会,综合会把for 循环全部条件下的电路翻译出来。同时for 循环语句不能被时钟沿触发,而RTL 设计中多数要时钟沿触发,这样的设计多用有限状态机来完成。故不建议在RTL 设计中使用for 循环,但是在testbench 中可以使用。For 循环语句示例如下:

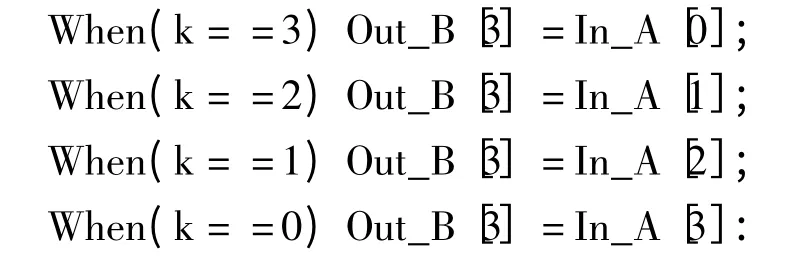

由于每次循环k 都被看做一个常数,所以不会综合出减法器。综合时循环链会被打开。上面的循环相当于下面的程序:

3 设计时序电路时的代码风格

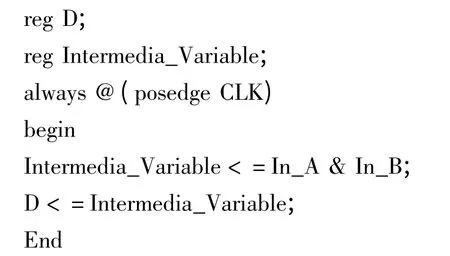

3.1 非阻塞赋值在时钟沿触发电路中

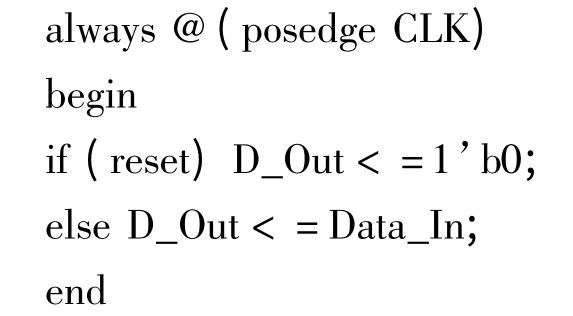

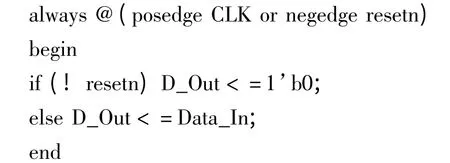

由时钟沿触发的电路分为时钟上升沿触发(posedge CLK)和时钟下降沿触发(negedge CLK);同时在时钟沿触发的电路中,赋值语句应该使用非阻塞型。如下例所示:

3.2 时钟沿触发中的同步复位

3.3 时钟沿触发中的异步复位

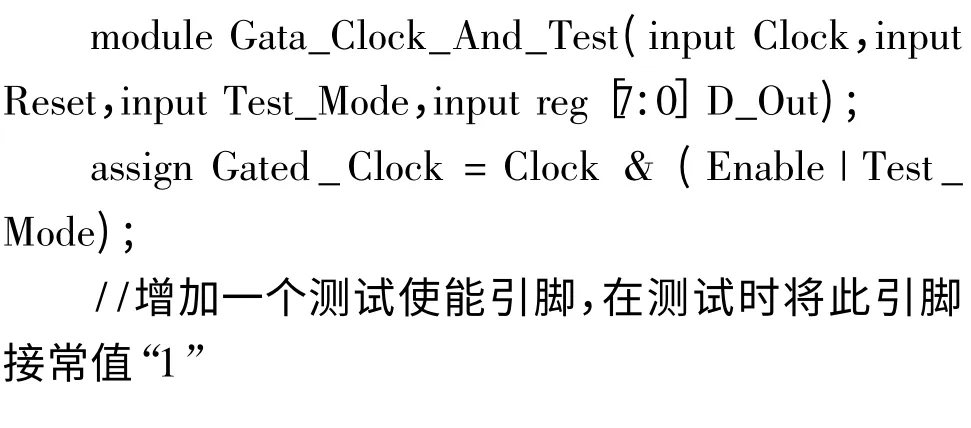

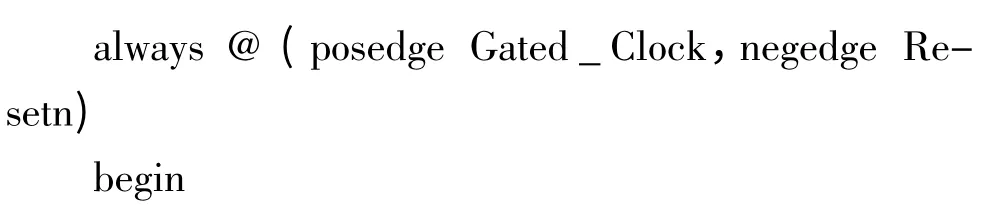

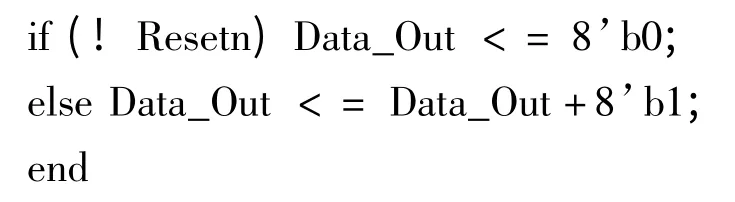

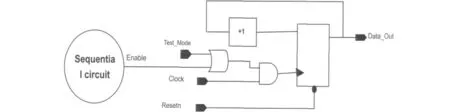

3.4 门控时钟

功耗的产生大部分在时钟状态转换时,通过门控时钟关闭空闲电路的时钟是减小功耗的有效方法。减小flip-flop时钟端的transitions,能够全面减小电路的功耗。如下例和图3 所示。

图3 门控时钟

4 结束语

RTL 设计中的Verilog 代码风格更偏重的是,某一个电路,用那一种形式的语言描述,才能将电路描述得更准确,综合以后产生的电路更合理。以上列出的代码编写实例无法覆盖代码编写的方方面面,还有很多细节问题,需要在实际编写过程中加以考虑。并且有些规定也不是绝对的,需要灵活处理。但其实代码风格还包括遵循代码编写规范书写的代码,以及容易阅读、理解、维护、修改、跟踪调试、整理文档等方面。总的方向是,努力写整洁、可读性好并且在综合后电路也很合理的代码。

[1]袁俊泉,孙敏琪,曹瑞,编著.Verilog HDL 数字系统设计及其应用[M].西安:西安电子科技大学出版社,2002.11.

[2]夏宇闻,编著.Verilog 数字系统设计教程[M].北京:北京航空航天大学出版社,2003.7.