MOSFET驱动电路分析与设计

包尔恒

(深圳麦格米特电气股份有限公司,广东 深圳518057)

功率场效应晶体管(简称Power Mosfet)是所有全控型电力电子器件中工作频带最宽的一种,因此在高频化进程中得到广泛应用。MOSFET使用中驱动电路的设计显得尤为关键,它直接关系到MOSFET的性能发挥及整体电路的效率和可靠性。

1 MOSFET开关模型及驱动基本要求

1.1 MOSFET开关特性模型

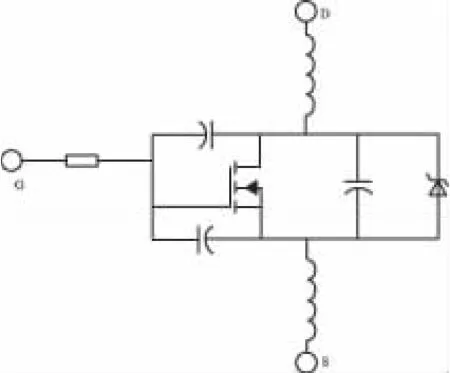

MOSFET的开关特性模型可用图1表示,开关特性取决于下述三个极间电容的电压变化速度有多快 :

CGD=CRSSCRSS:反馈电容

CGS=CISS-CRSSCISS:输入电容

CDS=COSS-CRSSCOSS:输出电容

图1 MOSFET的开关特性模型

快速开关需要栅极驱动电路的负载能力足够大,以在要求时间内完成对等效栅极电容(CEI)的充电。这里需要注意几个容易忽略的问题:(1)内部引线栅极输入电阻RGI,降低了开关速度和dv/dt耐受能力;(2)栅极门槛电压UTH具有负温度系数特性,通常为–7 mV/℃,高温时门槛电压会降低,在逻辑电平设计应用中需要考虑,这一特性降低了高温下UGS的抗干扰能力而易引起误导通,同时也使得在更低的门极电压下才能可靠关断;(3)源极引线电感LS和漏极引线电感LD在开关过程中会引起应力问题,如UGS负压等,设计中尽量从布局方面减小引线电感。

1.2 栅极驱动电流计算

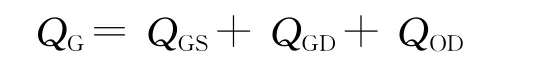

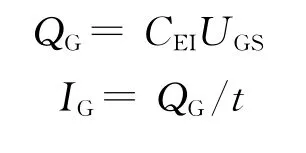

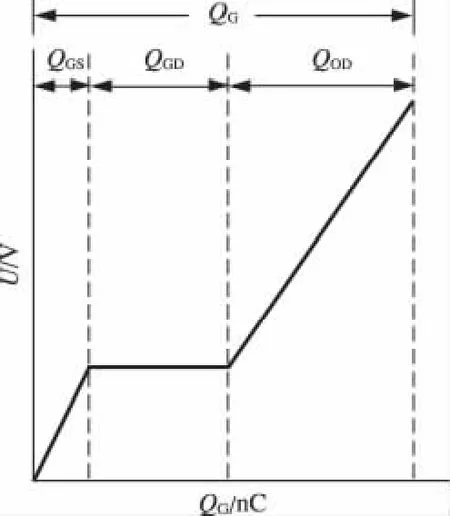

计算栅极驱动电流时,要根据MOSFET生产商提供的栅极电荷QG数据计算,QG可表示为:

式中,QG:总的栅极电荷;QGS:栅极-源极电荷;QGD:栅极-漏极电荷(Miller);QOD:Miller电容充满后的过充电荷。

MOSFET门极电荷-栅源电压特性曲线如图2,驱动电流决定MOSFET导通和截止的速度快慢(栅极电压的上升和下降时间),优化的上升/下降时间取决于诸多因素,如EMI、开关损耗及开关频率等。MOSFET导通和截止的速度与栅极电容的充电和放电速度有关,驱动电流可由下式计算:

图2 MOSFET门极电荷-栅源电压特性曲线

式中,QG:总栅极电荷;CEI:等效栅极电容;UGS:栅-源极间电压;IG:MOSFET在时间t内导通所需驱动电流。上述公式假设电流使用的是恒流源,若用驱动器的峰值驱动电流来计算,将会产生一些误差。MOSFET驱动器驱动能力以输出峰值电流能力来表示,通常,峰值电流也表示在器件最大偏置电压下的电流,这意味着如果MOSFET驱动器工作在较低的偏置电压,峰值电流驱动能力会相应降低。

例:QG=20 nC ,UGS=12 V ,

导通/截止时间:t=40 ns,

IG= QG/t=20 nC/40 ns=0.5 A。

这个公式得出的峰值驱动电流为0.5 A。然而,设计参数中栅极驱动电压为12 V,在选择驱动器时,这个参数应在考虑之中,例如,如果选择的驱动器在18 V 时标称电流为0.5 A,则在12 V时,其峰值输出电流将小于0.5 A。因此对于这个应用,应选择峰值输出电流为1.0A的驱动器。同时还需考虑在MOSFET驱动器和功率MOSFET栅极之间使用外部电阻,这会减小栅极电容的峰值充电电流。

1.3 驱动功耗

对MOSFET的栅极电容进行充电和放电需要同样的能量,MOSFET栅极电容充电和放电产生的功耗:

PC=CEIU2GS2f

式中,f为开关频率,由于QG=CEIUGS,得到:

PC=QGUGSf

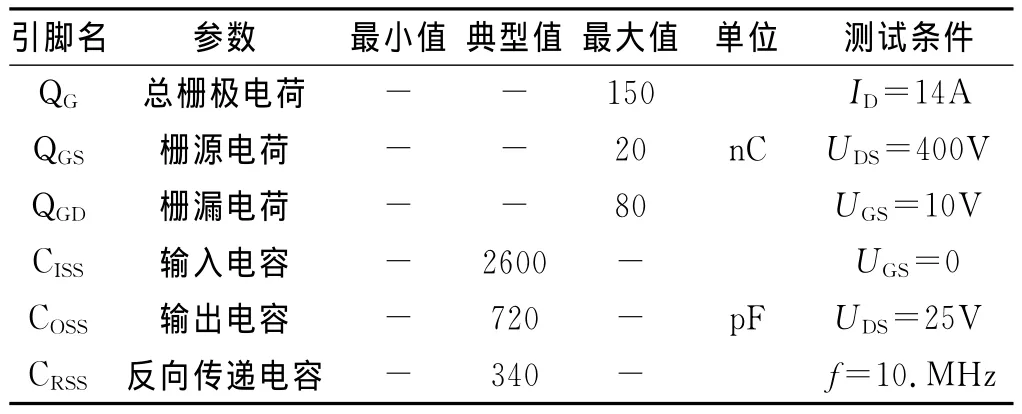

表1为某500 V/14 A的 MOSFET栅极电容在数据手册中的典型示例,要注意表中给出的数值与测试条件有关:栅极电压和漏极电压,这些测试条件影响着栅极电荷的值。图3为同一MOSFET在不同栅极和漏极电压下栅极电荷的特性曲线,应确保用来计算功耗的栅极电荷值也要满足应用条件。

从图3的曲线中选取UGS=10 V的典型值,得到总栅极电荷为98 nC(UDS=400 V)。利用Q =CU关系式,得到栅极电容为9.8 nF,这大大高于表1中列出的2.6 nF的输入电容。这表明当计算栅极电容值时,总栅极电容值应从总栅极电荷值推导而来。

表1 500V/14A的MOSFET栅极电容在数据手册中的典型数据值

图3 不同栅极和漏极电压下栅极电荷的特性曲线

注意:对于一些MOSFET,栅极驱动电压超过8 V至10 V并不会进一步减小MOSFET的通态电阻(RDS-ON),由于栅极驱动电压和驱动损耗成比例关系,减小栅极驱动电压可以减小驱动器的功耗。

2 MOSFET开通及关断过程分析

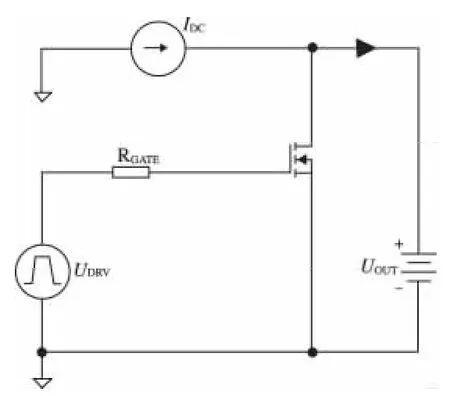

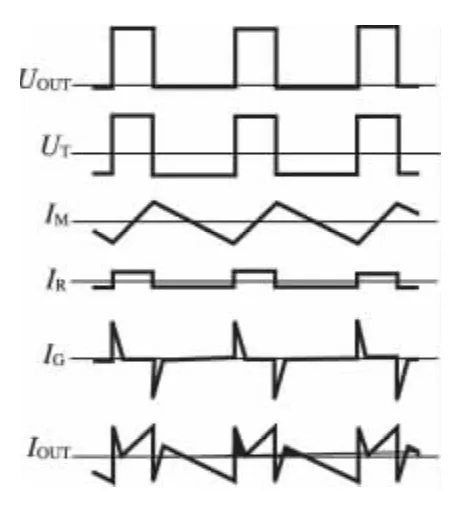

以感性开关模型Boost电路(图4)来分析 MOSFET的开通和关断过程。电感用直流电流源表示,在较短的开关周期内电感电流可以认为保持恒定,二极管在MOS管关断期间为电流提供通路并将MOS管的漏极电压箝位到输出电压。

图4 Boost电路模型

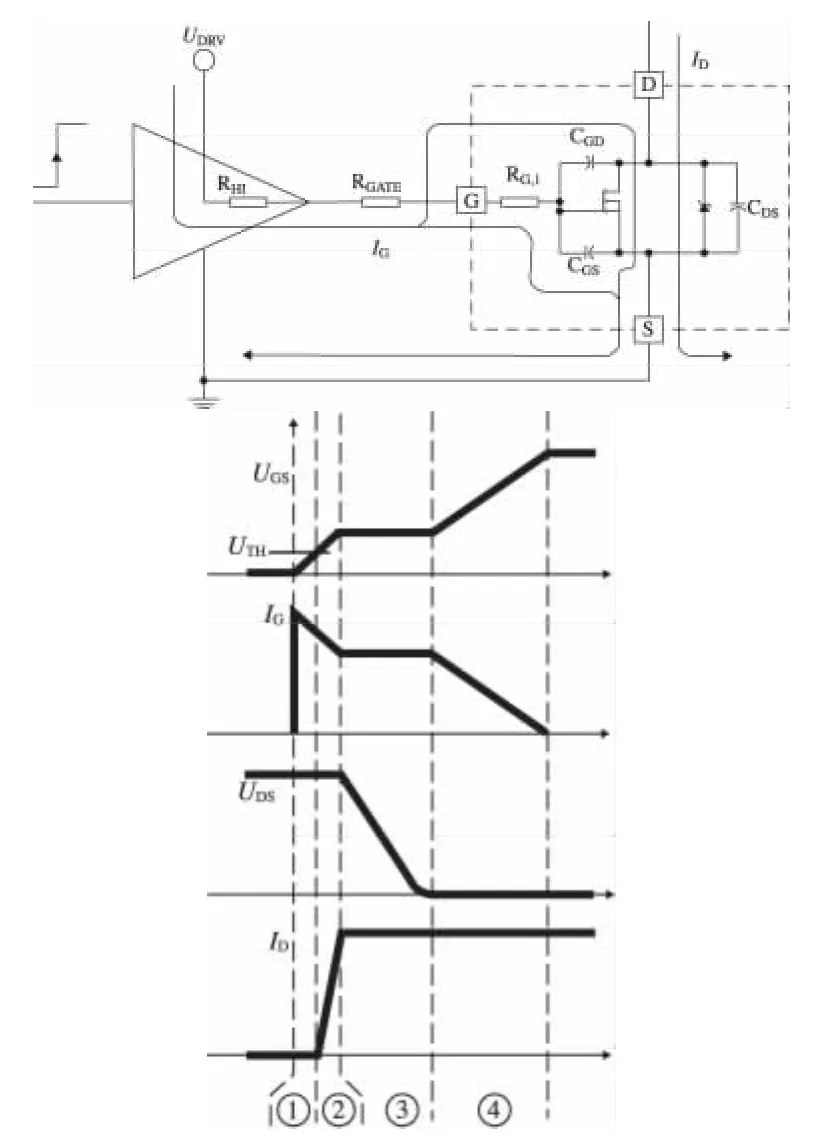

图5所示,MOSFET开通过程分为4个阶段:(1)栅极输入电容的电压从0充到UTH,绝大部分栅极电流用于给CGS充电,MOS管漏级电流和漏级电压保持不变;(2)一旦门极电压达到UTH,MOSFET开始承载电流,该阶段UGS电压从UTH上升到密勒平台电压UGS,Miller,MOSFET工作于线性区,漏极电流和门极电压成比例上升,门极电流流过CGS和CGD,漏极电压保持输出电压不变;(3)栅极电压已经充到足够高(UGS,Miller),使MOS管能够承载全部负载电流而二极管电流下降到零,驱动电路提供的所有栅极电流用于给CGD放电使漏源电压迅速下降而栅极电压维持不变(密勒平台);(4)该阶段UGS从UGS,Miller电压上升到最终的驱动电压,使MOS管进入深度饱和,UGS电压的最终幅值决定了最终的通态电阻;栅极电流用于给CGS和CGD充电,漏极电流不变,随着UGS电压的上升,饱和深度增加而导通电阻减小,所以漏极电压略有降低。

图5 MOSFET开通过程

关断过程也分为4个阶段(见图6),可参照开通过程进行分析,这里不再详述。

3 MOSFET驱动电路

3.1 以地为参考电平的门极驱动电路

(1)PWM控制器直接驱动

用PWM控制芯片直接驱动MOS管,应注意:PWM控制器或许离MOS管比较远,将在布局走线中引入电感,杂散电感减慢了开关速度,欠阻尼时会导致驱动波形出现振荡。布局应尽量使PWM控制器靠近MOS管且加宽驱动电路的PCB走线;PWM控制器的峰值电流驱动能力有限,功耗问题需要关注,尤其在频率较高的情况下;旁路电容需就近跨接在驱动器的电源引脚和地引脚之间,通常取值0.1-1μF;在NPN双级性输出级情况下,外并肖特基二极管为反向谐振电流(寄生电感和MOS管结电容的振荡电流)提供通路以保护输出级。

(2)双极性图腾柱驱动器

该驱动电路特点:增大了峰值电流驱动能力,解决了PWM控制器直接驱动时的功耗问题;紧靠MOS管放置,减小了驱动环路面积和杂散电感;分立的驱动电路需要独立的旁路电容,为提高噪声抑制能力,两个旁路电容之间需串平波电阻R或者电感;两个PN结互相保护可防止反向击穿。

(3)加速(关断)电路

通常驱动加速电路是指关断加速,因为MOS管的开通过程通常伴随续流二极管的关断过程(如Boost电路),MOS管的开通速度受限于二极管的反向恢复特性,与驱动电路本身的驱动能力关系不大。

MOS管的关断速度取决于栅极驱动电路,关断时从MOS管栅极流出的电流越大,栅极输入电容放电越快,开关时间越短,开关损耗越低;更大的放电电流可以通过减小放电回路的阻抗或者关断时在栅极施加负压得到。但同时应注意:越快的关断速度伴随MOS管呈现更高的di/dt和dv/dt,关断加速电路有可能增加波形的振荡,带来电应力超标和EMI等问题,下面介绍两种简单常用的加速关断电路。

(a)反并联二极管关断电路中,RGATE的大小调节开通速度,DOFF在关断栅极放电电流较大(IG>UD.FWD/RGATE)时起作用,减小了关断时间,并改善了dv/dt抗扰性;栅极放电电流仍然必须流过驱动器的输出阻抗。

(b)PNP三极管关断电路,RGATE可以调节开通速度,DON为开通电流提供通路,同时箝位保护QOFF基射结在开通过程中反向击穿;该电路最主要的优点是关断三极管的导通把关断电流限制在最小的环路内,从而旁路了栅极驱动环路杂散电感、可能的电流采样电阻和驱动器的输出阻抗,减小了驱动器的功耗;QOFF不会进入饱和状态,能够快速开关;门极电压被箝在UDRV+0.7 V和 GND-0.7 V,消除了过压应力风险;由于QOFF的基射结压降使得门极电压不能达到0。

3.2 高压侧非隔离门级驱动

这种驱动方式目前常用自举栅极驱动IC实现,通常用于驱动桥式电路桥臂上下管,常见的如IR21814等。应用中需要注意:由于杂散电感的影响,关断过程中高压侧MOS管源极US(桥臂上下管的中点电位)对COM可能出现负压,导致驱动IC进入锁定状态;起动和负载动态时,防止自举电容电压降低到触发欠压锁定保护;注意控制地和功率地分离;布局中尽量减小栅极和自举电路的高峰值电流环路。

3.3 容性耦合门极驱动电路

电容CC在关断时为栅极提供负向驱动电压-UCL,提高了关断速度,改善了MOS管的dv/dt抗扰性,降低了高频开关应用中受干扰误开通的可能性;Cc电容的分压导致正向驱动电压降低为UDRV-UCL,开通速度降低,MOS管饱和深度减小,导致更高的RDS(on);最大的负向电压可通过齐纳二极管箝位限制;UC=UDRVD,在小占空比时会出现负压过小,大占空比下电容电压过高导致驱动电压不足,设计中要折中考虑。

3.4 变压器耦合驱动

在自举驱动IC出现以前,常用驱动变压器驱动桥式电路的上下管,变压器驱动应用最多的场合在于原副边隔离驱动,目前两种方式都有使用,各有特点:IC驱动简单,但存在开关延迟,不能单独进行原副边隔离驱动;驱动变压器可以忽略开关延迟,但电路器件和设计略显复杂,原副边隔离驱动最常用。

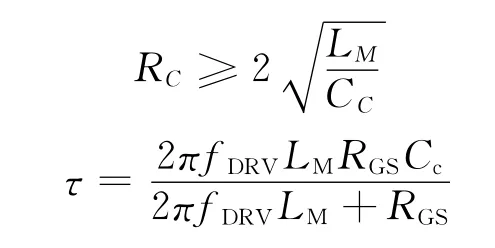

(1)单端变压器

该电路常用于单输出PWM控制器驱动不共地的高端MOSFET,和原边绕组串联的耦合电容在MOS管关断时为励磁电感提供复位电压;占空比的突变对励磁电感LM和耦合电容CC组成的LC谐振槽是一个动态激励,通常情况下,和电容串联的小阻值电阻RC可以衰减这个振荡(注意该电阻包括驱动器的输出阻抗,是个等效电阻);耦合电容电压的临界阻尼响应将需要一个不合理的高阻值电阻,从而影响开关速度,而欠阻尼响应会引起过高的栅源电压应力;根据谐振电路特征阻抗可以得出电阻阻值,耦合电容电压的动态时间常数及驱动器的输出电流波形如下:

从图7可以看出,输出电流的阴影部分对应驱动器输出为低电平,输出电流应该为负,但由于励磁电流分量变化较为缓慢,实际输出电流为正,因此驱动IC的输出需要处理双向电流。如果驱动器为双极性输出级(电流只能单向流动),需要在驱动芯片输出端加肖特基二极管进行保护;在占空比变化范围较宽的应用中,大占空比下耦合电容电压增加,则关断时负向电压增加但开通时正向驱动电压降低,在副边增加CC2和箝位二极管DC2可以在副边恢复初始驱动电压幅值。如果要得到较大的断态负向电压,则可在二极管上再串联一齐纳二极管。

图7 驱动器输出电流波形

变压器的设计需要考虑:驱动变压器虽属于功率小(不需考虑热问题),但流过驱动MOSFET是高峰值电流;考虑在所有运行条件下的伏秒积,避免饱和,通常取稳态运行情况下的最大峰值磁密为饱和磁密的1/3;磁芯常用高磁导率的铁氧体材料以增大励磁电感、减小励磁电流;绕组绕制和排列尽可能减小漏感以减小开关时间延迟。

(2)双端变压器

大功率半桥或全桥电路拓扑中常用的双端变压器驱动电路。电路不需交流耦合电容,占空比及器件差异引起的不对称可通过驱动器输出阻抗(或者和驱动变压器原边绕组串联的小阻值电阻)得到补偿;在移相调制应用的动态过程中PWM输出有可能无法产生50%占空比导致占空比出现不对称,磁密设计需要预留一定的余量;驱动变压器副边通常需要加本地关断电路,尤其在高频应用中,由于驱动变压器的漏感对快速变化的驱动信号呈现高阻抗,本地关断电路可以提高关断速度、减少关断损耗和提高du/dt抗扰性。

4 结 论

本文介绍了门级驱动电路的特点及设计过程中需要考虑的影响因素,为可靠、高性能的MOSFET应用设计提供参考。当然,门极驱动电路不止上述类型,但文中的原理和方法同样有助于其它方案的理解和分析。

[1] Laszlo Balogh.Design and Application Guide for High Speed MOSFET Gate Drive Circuits[Z].Texas Instruments,2002.

[2] Jamie Dunn.MOSFET驱动器与 MOSFET的匹配设计[Z].Microchip Technology Inc.2006.

[3] 林渭勋.现代电力电子电路.杭州:浙江大学出版社.2002.

[4] W.Andreycak.Practical Considerations in High Performance MOSFET,IGBT and MCT Gate Drive Circuits[Z].Unitrode Corporation,Application Note U-137,2008.