L波段捷变频收发前端设计仿真

宋里瑾,贺 欣,宋小勇

(中国空空导弹研究院 河南 洛阳 471009)

信息是信息化战斗中的决定因素,而数据链[1]的根本作用就是解决信息获取、信息处理和信息传输的问题,并从速度上进行优化,极大地增强整体作战效能。某型数据链工作在L波段,是一种高保密、抗干扰、低截获概率的通信链路。微波收发前端作为该数据链终端的重要功能件,其内部既有功率电平的发射通道,又有高增益、低噪声的接收通道,是集高频、低频、大信号、小信号等为一体的复杂功能件。本文着重介绍应用于某型数据链小型化收发前端的设计过程。该组件具有低噪声、低杂散、捷变频等特点。

1 收发前端的主要性能指标要求

本文介绍的收发前端工作在L波段,可以按照伪随机跳频图案产生51个不同的收/发频率,相对带宽约为22%。其主要性能指标是:

接收通道:噪声系数≤5 dB;输入信号范围为:-100~-20 dBm;输出电平:-15~0 dBm;

发射通道:输入功率为-10~0 dBm,输出功率为≥0 dBm;

捷变频时间:≤6 μs。

2 收发前端的组成与工作原理

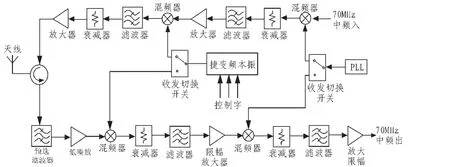

收发前端主要包括发射通道、接收通道和捷变频本振3大部分[2],用于完成发射、接收两大功能,其组成框图如图1所示。在该组件发射通道:中频已调信号经过混频、滤波搬移到L波段指定频段,经过放大后输出射频信号,最后经过环行器至天线辐射单元。在接收通道:从天线单元接收到微弱信号,经过预选滤波、低噪声放大、下变频、限幅放大到中频供后级数字电路进行采样和数据处理。捷变频本振部分负责产生在一定范围内快速变化的宽带低相噪信号,用于给发射通道和接收通道提供快跳本振源,以满足系统抗干扰的要求。由于发射通道和接收通道分时工作,可以通过收发开关按照时序对本振信号进行不同链路之间的切换。

3 主要组成部分的设计

3.1 接收通道

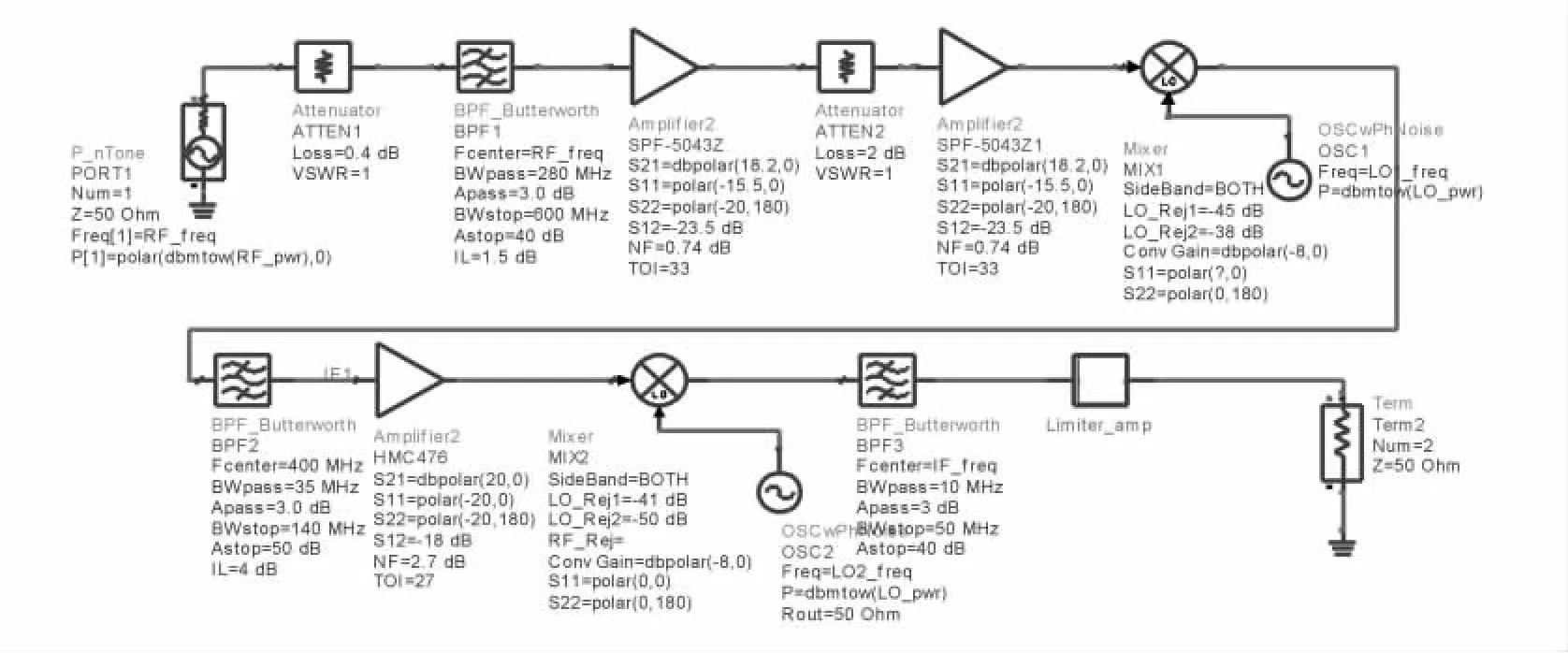

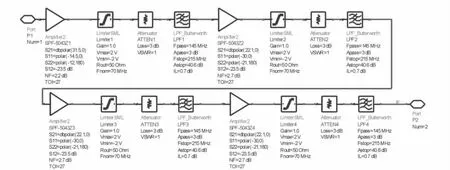

接收通道负责接收L波段范围内的射频信号,相对带宽较宽。如果采用一次变频的方案,宽带的本振信号会泄露至射频输入端,同时较难实现大于55 dBc的镜频抑制。与一次变频的方案相比较,二次变频显著的优点在于一中频可以选的更高,对改善本振泄露和镜频的抑制有很大的帮助。因此确定采用两次变频的超外差式接收机方案,如图2所示。

3.1.1 噪声系数仿真

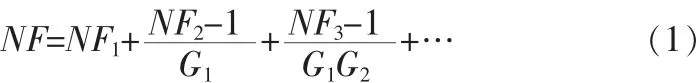

根据级联系统噪声系数(NF)计算公式[4]

式中:NF1为第1级放大器噪声系数;NF2为第2级放大器噪声系数;G1为第1级放大器增益;NF3为第3级放大器噪声系数;G2为第2级放大器增益。公式(1)可以得出接收通道的噪声系数主要取决于前级的低噪声放大器,低噪声放大器之前的无源电路其插入损耗应尽可能小。

图1 收发前端组成框图Fig.1 Block diagram of transmitting and receiving front-end module

图2 接收通道仿真电路Fig.2 Simulation circuit of receiving channel

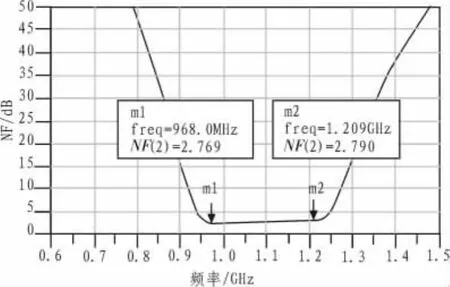

采用ADS软件对接收通道的噪声系数仿真如图3所示,从仿真结果可以看出通带内的噪声系数小于5 dB,满足指标要求。

3.1.2 动态范围仿真

由于该系统为捷变频系统,发射和接收通道的功率随本振频率的跳变存在瞬间建立的过程。为了减少相应的功率起伏瞬态时延,因此采用限幅放大的方式来实现接收通道高动态范围设计,如图4所示。

图3 接收通道的噪声系数仿真Fig.3 Noise figure simulation of the receiving channel

图4 接收通道的限幅放大仿真电路Fig.4 Limiter-amplifier simulation of the receiving channel

接收通道的限幅放大电路主要由放大器、限幅器、衰减器和滤波器组成。当接收端接收到大功率信号时,限幅器将功率限制在10 dBm左右,同时由于器件非线性产生大量的谐波杂散,因此需要在限幅器后面增加衰减器和滤波器,改善级间匹配的同时抑制谐波杂散的功率。根据接收链路的增益分配要求,需要4级放大、限幅电路实现系统80 dB的动态范围要求。

以射频输入信号功率为扫描变量,对接收通道的中频输出功率进行仿真[3],得到图5所示的功率曲线。从图5可以看出,当输入信号在-100~-20 dBm范围内变化时,输出信号被控制在-15~0 dBm之间,满足系统动态范围要求。

3.1.3 组合干扰仿真

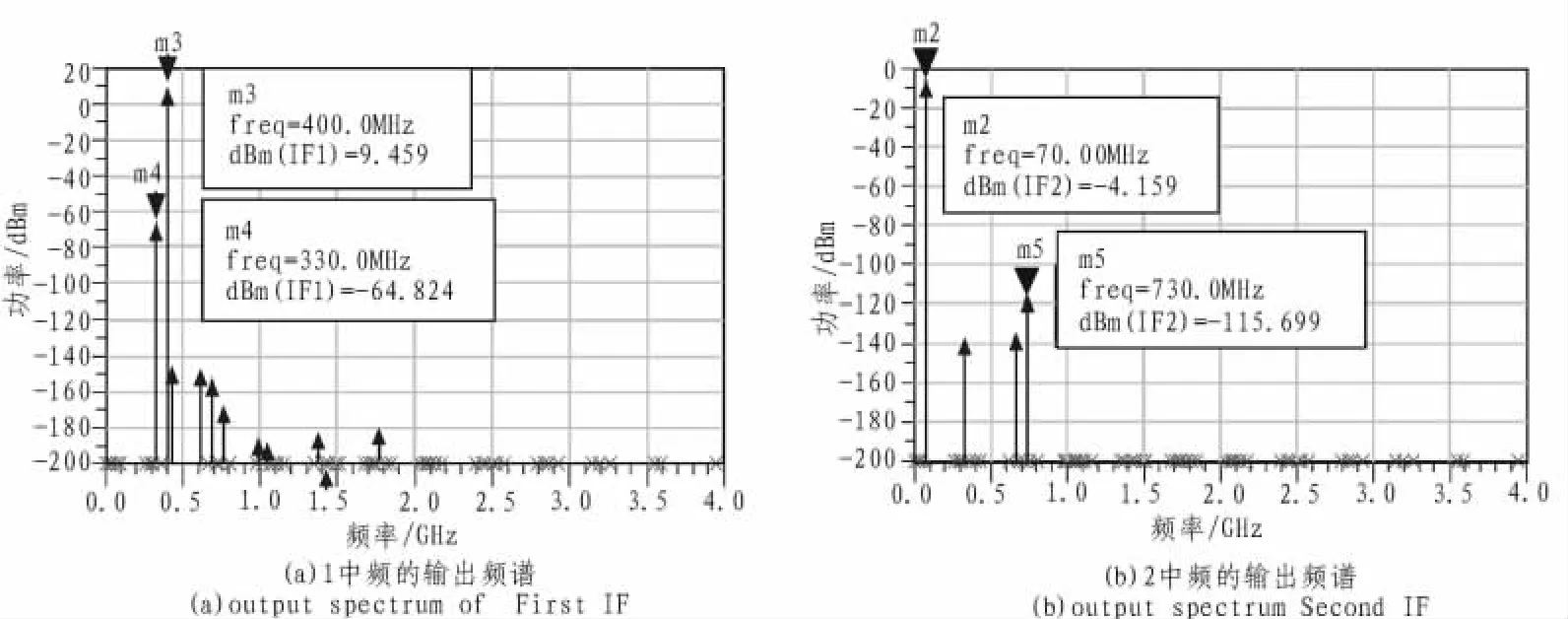

接收通道中混频器和放大器是最容易产生非线性失真的器件,当射频信号fRF和本振信号fLO通过这些器件时会产生|mfRF±nfLO|组合的非线性频率分量。其中只有|fRF-fLO|频率为有用中频信号。同时,由于采用DDS实现的捷变频本振部分需要提供宽带跳频信号,谐杂波分量较多,因此接收通道的中频频率和DDS的输出信号频率两者必须合理规划,才能最大程度减少谐杂波干扰信号的影响。

在本方案设计中,由于捷变频本振以3 MHz的步进在237 MHz范围内跳变,而二中频信号固定不变,因此设计的重点在于第一级变频中频频率的选择。在设计过程中,要充分考虑DDS频率合成产生的杂散,混频产生的非线性频率分量、滤波器的实现难易程度等,尽量避免谐杂波、交调分量等进入到接收通道的滤波器的通带。

通过ADS软件对接收通道进行谐波平衡分析,仿真得到一、二级混频输出的杂散特性,如图6所示。从仿真结果可以看出,一、二级混频输出的信号杂散抑制达到70 dB以上,满足设计指标要求。

图6 中频输出频谱Fig.6 Output spectrum of IF port

3.2 发射通道

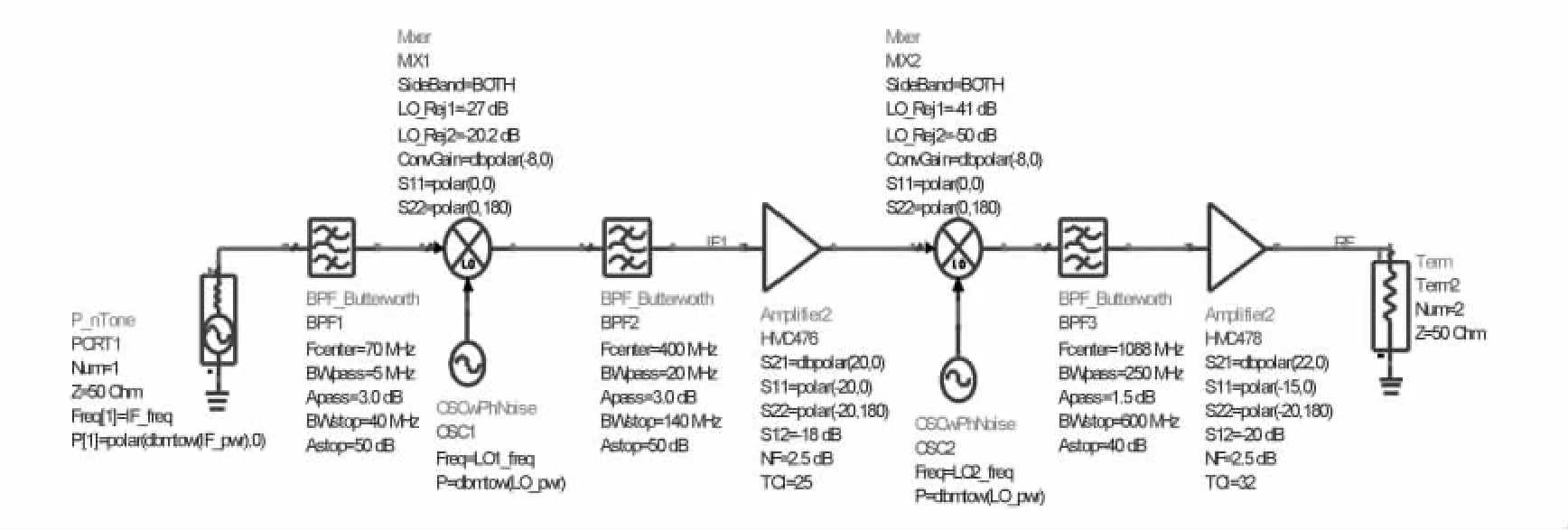

发射通道负责将70 MHz±2 MHz的窄带中频信号上变频至L波段,同时将带宽扩展至约240 MHz,并放大经过环行器送至收发共用天线,完成自中频至射频的发射功能。

3.2.1 发射通道的增益

发射通道与接收通道共用捷变频本振,因此发射通道的与接收通道电路形式互易,如图7所示。中频输入信号电平为-10~0 dBm,输出功率为大于0 dBm,因此要求发射通道增益大于10 dB。由图7电路仿真可以得到发射通道增益为12.4 dB,中频输入信号0 dBm时输出信号为12.4 dBm。末级放大器的1 dB压缩点P-1为17.8 dBm,输出功率与1 dB压缩点之间有5 dB左右的余量,可以保证发射通道的线性度要求。

3.2.2 发射通道的杂散特性分析

值得注意的是,作为宽带跳频系统,尤其在发射通道的射频输出端信号带宽迅速变宽,本振的谐杂波、变频的交调分量等杂波极易落入有用信号带内形成干扰。因此,需要在系统内对发射通道的杂散特性进行优化设计,尽量抑制干扰信号幅度。

ADS软件对发射通道进行谐波平衡分析[5],仿真得到射频输出的频谱特性,如图8所示。从仿真结果可以看出,射频输出信号杂散抑制达到80 dB以上,满足设计指标要求。

3.3 捷变频本振

图7 发射通道仿真电路Fig.7 Simulation circuit of transmitting channel

图8 发射通道的射频输出频谱Fig.8 RF output spectrum of transmitting channel

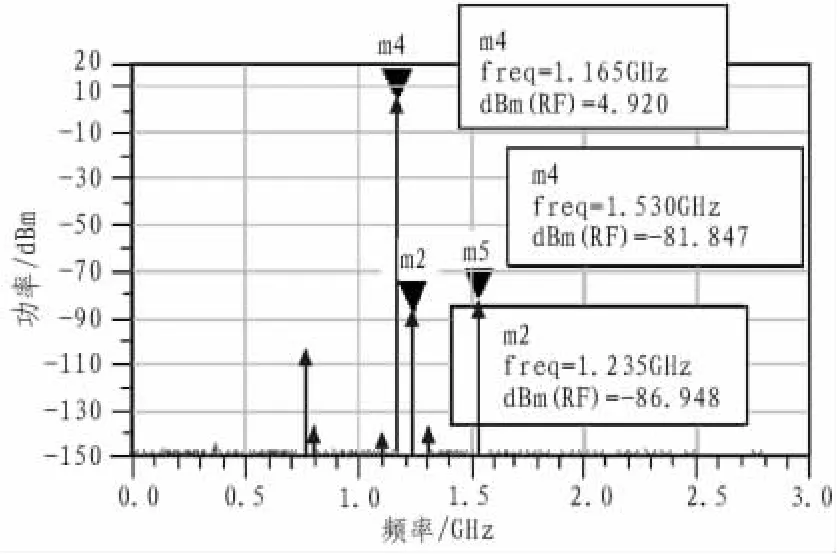

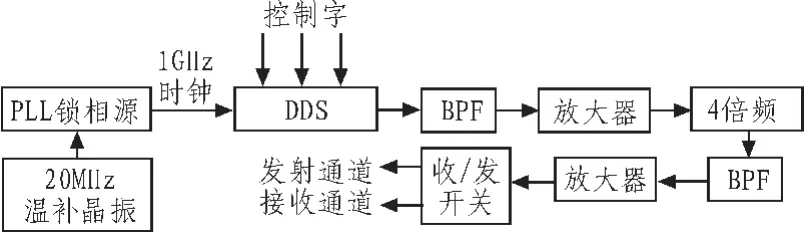

频率捷变时间作为捷变本振的关键指标,指标要求时间小于6 μs。锁相环(PLL)在频率转换时需要一定的捕获时间,捕获时间与环路的类型、参数和跳频步长等有关。通常跳频步长为10 MHz左右时,捕获大概需要10~20 μs。当步长很大时,捕获时间会达到毫秒级。直接数字式(DDS)频率合成[6]的变频时间主要受限于编程配置的时间,一般可以做到1 μs量级。综合频率捷变时间、相位噪声、谐杂波抑制等性能,采用DDS+DAS(倍频)方案实现捷变本振设计,原理框图如图9所示。

图9 捷变频本振原理框图Fig.9 Principle diagram of frequency agility local oscillator

捷变频本振主要由参考晶振、锁相源、DDS、滤波器、放大器、倍频器以及控制电路组成。PLL锁相源为DDS提供1 GHz的参考信号,用于提高DDS的输出频率和带宽;同时由于DDS采用外部PLL提供的高频时钟,避免使用内部的时钟倍频电路,能够有效减少时钟谐波杂散。合理选择DDS的输出频率,能够使其本身输出信号杂散最小。DDS的输出信号经过由放大器、倍频器和带通滤波器组成的倍频链路之后,最终由单刀双掷开关完成收发本振的切换功能。在设计中合理选择倍频次数可以有效降低对滤波器的设计要求,从而更大程度减小输出信号杂散,以达到满足要求的频率纯度。

4 结束语

文中介绍了基于DDS的收发前端的设计方法,该方案既能充分发挥DDS跳频速度快、输出频率分辨率高的优点,还具有电路简单,易于实现的特点,其仿真结果能够满足要求的技术指标,目前该组件正处于调试阶段,并且不断考虑增加新的特性(发射功率、功耗最小化等),能够为更高频段收发前端设计提供参考。

[1]梅文华,蔡善法.JTIDS/Link16数据链[M].北京:国防工业出版社,2007.

[2]胡明春,周志鹏,严伟.相控阵雷达收发组件技术[M].北京.国防工业出版社,2010.

[3]陈艳华,李朝晖,夏玮.ADS应用详解-----射频电路设计与仿真[M].北京:人民邮电出版社,2008.

[4]弋稳.雷达接收机技术[M].北京:电子工业出版社,2005.

[5]徐兴福.ADS 2008射频电路设计与仿真实例[M].北京:电子工业出版社,2009.

[6]曾建军.基于DDS和PLL的频率合成器[D].成都:电子科技大学,2011.