适用于DBF的多通道中频宽带数字接收机设计

郑 锦,王玉辉,张 晋

(1.91404 部队,河北 秦皇岛 066001;2.中国船舶重工集团公司第七二四研究所,南京 210003)

0 引言

随着雷达体制和集成电路的迅速发展,多通道接收机得到了越来越普遍的应用。同时,由于数字接收机将接收到的中频甚至射频回波信号进行A/D 采样,然后进行数字下变频和数字滤波,使基带信号具备了优良的正交特性,没有或大大减少了模拟接收机带来的温度漂移、增益变化或直流电平漂移,所以在多通道接收机设计中采用数字接收机设计的方案越来越多[1]。采用DBF 体制可以实现对波束自适应置零和低副瓣所需幅相更优控制、当同时多波束时可以获得更快的帧搜索时间;采用宽带信号可以获得高的距离分别率,有助于目标识别。显然,DBF 体制和宽带化是相控阵雷达发展的重要方向[2]。宽带信号接收处理的工程化方法有两种:一种使用拉伸处理(去斜)的模拟方法来接收宽带信号[3-4],将宽带信号转换为窄带降低了对ADC 采样率需求,但是其脉压性能受目标回波时延影响较大[5],且当系统对目标高分辨探测的带宽内存在幅相误差时,很难对接收数据进行幅相均衡补偿或对发射信号进行预失真处理进行系统校正;另一种是数字去调频直接采样,而该种方法显然避免了上述缺陷[1],但对ADC 要求较高。为充分提高系统探测性能,本文选择了后者进行设计,通过对ADC 选型、相关电路设计和指标试验等各个环节的综合考虑,最终完成了设计。DBF 体制的多通道接收机,其幅相一致性和稳定性是影响合成波束副瓣电平和指向精度的重要因素[6]。理论上,多通道接收机的幅相不一致性可以通过注入测试信号来校准,但实际工程中受校准范围和校准频次的限制,校准在时间上和能力上是有限的。因此,其幅相稳定性和一致性成为目前多通道数字接收机研究的重点。

1 方案及组成

本文设计的8 通道中频宽带数字接收机主要包含电源电路、模数转换电路、FPGA 电路、数据存储及配置电路、光纤通讯电路、时钟分配电路、逻辑控制与状态监测电路等。系统组成框图如图1所示,可根据系统提供的光纤指令及时钟、触发信号完成同时采集8通道、250 MHz中频、最大100 MHz 带宽或最小5 MHz带宽的模拟信号(并可根据需要进行通道扩展)。将这些通道的数字化信号进行数字下变频(DDC)、通道幅相修正、数字波束合成(DBF)、低通滤波等数字信号预处理后通过光纤将数字基带I/Q信号输出,其中宽带1个和波束,窄带同时6波束;并且具备收发通道的逻辑控制及在线电压、电流和温度监测功能。

图1 8 通道中频宽带数字接收机原理框图

1.1 时钟分配电路的设计

DBF 体制的多通道接收机需要严格一致的时钟,这样才能统一多个通道时序。在本项目中有8 路ADC 需要同步,再加上一路提供给FPGA的全局时钟一共需要9 路。时钟信号分配一般有两种方法:一种是模拟功分法:有两种方案,方案1:微带线设计,由于信号频率较低、波长较长所以分配网络比较庞大;方案2:模拟功分芯片搭建,完成一个9 功分的设计,2 功分的芯片一共需要8个;另外一种是数字分配法:采用时钟分配芯片设计。这两种设计方法相比较而言模拟方法是无源设计,但是占用的PCB 面积都比较大;数字方法采用多路时钟分配芯片,设计占用PCB 面积小。由于本设计用于多通道DBF 接收机,体积重量是设计中一个重要的考虑因素,所以这里选用数字方法进行时钟分配。时钟分配电路的原理图如图2所示。

图2 时钟分配电路原理图

对于时钟分配电路的逻辑选择,目前常用的数字时钟逻辑标准主要有LVCMOS、LVTTL、LVDS、LVPECL等。LVCMOS 及LVTTL 本身是单端信号传输标准,用作时钟信号不适于长距离传输,并且易被干扰,附加抖动较大;LVDS 及LVPECL 均为差分信号传输标准,适于距离较长的传输,由于LVDS 较LVPECL偏置电平及压差较小,所以LVPECL 更适于对抖动要求更严格的场合。在本文中时钟分配芯片选用LVPECL 逻辑的MC100LVE111,其附加随机抖动为0.2 ps,片内的延迟不确定性不超过50ps,保证各个通道间的一致性,引入1 路200 MHz时钟信号,将其分配成9 路LVPECL 差分信号后分别送给8 路ADC和FPGA,在时钟输入端做好终端匹配。时钟芯片供电使用线性电源并通过穿心电容滤波,以减少供电电源引入的抖动。提供给各路ADC的差分时钟布线尽量保持等长,这样可以减少布线引入的各个通道间采样时钟的不一致性。PCB 上时钟缓冲输出到所有时钟输入之间应该是点对点连接,走线长度应该匹配使偏差最小。每个时钟线上的过孔数应相同。时钟信号要远离同层上的其他信号,至少保持四倍最小间距。时钟电路是主要的干扰和辐射源,所以单独安排,使其尽量远离敏感电路。

1.2 信号采集电路设计

ADC的设计是数字接收机的关键,它直接影响整个接收系统的动态范围和灵敏度等指标。对ADC 芯片选择主要的指标有采样率、位宽、3 dB 带宽、信噪比(SNR)等,其中SNR 反映了对系统改善因子的限制。

在本文中,由于需满足100 MHz中频带宽的采样要求,所以对采样频率和模拟中频计算如下:

x(t)假设是具有带宽B=fmax-fmin的带通信号,则根据奈奎斯特带通采样定理:ADC的采样率fs必须满足2×fmax/m≤fs≤2×(fmax-B)/(m-1),fs>2B,其中m为任意正整数;所以在本设计中选用m=3、fs=200 MHz 进行设计,则模拟中频频率为250 MHz。

接收机的SNR 主要受限于模拟输入信号频率、时钟信号及ADC 本身所引起的综合孔径抖动[7]:

在本文中,ADC 选用ADI 公司的AD9230,位宽12 bit,最高转换速率达250 MSPS,最大模拟输入带宽为780 MHz,满足200~300 MHz的带宽使用要求,自身孔径抖动为0.2 ps,功耗为400 mW左右,数字输出为13 对差分LVDS 接口,12 对数据线,一对数据有效信号。由于系统的输入信号为250 MHz中频宽带信号,所以选择ADC的前端输入电路设计为变压器交流耦合,将模拟单端中频信号转为差分中频信号。

1.3 信号预处理FPGA 设计

在进行芯片选择前,必须明确FPGA 需要完成的任务。根据逻辑外部接口类型、速度、数量和信号预处理所需的逻辑资源、DSP 及RAM 数量以及耗费功率及成本进行综合权衡。在本文中,信号预处理FPGA 选用Xilinx 公司的Virtex5-XC5VSX95T。该芯片具有640个高速DSP处理单元和8784 kbit的高速双口RAM,最高运行频率为550MHz,在其内部可灵活实现DDS、DDC、FIR、FFT、DBF 等多种信号处理功能,具备640个有效IO来满足多种电平标准可根据需要进行灵活配置,若使用为LVDS 接口其速度最高支持到1.25 Gbit/s。内部具备System Monitor,内部集成多路选择器、200 kSPS ADC、温度传感器,能够对多路模拟信号进行分时数字化并实时监测FPGA 内部温度。它还具有16个GTP 高速串行口,支持从100 Mbit/s 到3.2 Gbit/s。

信号预处理的流程如图3所示。首先将从8个通道采集的ADC 数据分别与FPGA 内部的数字中频(NCO)进行混频,得到混频后的I/Q两个通道的数据;按照光纤送来的幅相修正系数进行通道修正,修正后的各个通道数据按照DBF 系数进行乘加运算;再进行FIR 低通滤波(根据不同的状态调用各自的FIR 系数,以减少逻辑及DSP 资源的耗费),得到所需波束的基带I/Q 数据。将FIR 滤波置于DBF后而不在混频后进行处理。这与传统的DDC 有所不同,主要由于上述运算均为线性运算,所以各个部分可以根据需要进行位置的替换而不影响处理结果。这样做在合成波束数量较少时可以明显减少FPGA中DSP 占用的资源,只有当合成波束的数量大于8个时,将FIR 置于DDC后才有优势。

图3 信号预处理流程图

1.4 光纤通讯电路

通讯电路需要满足数字接收机与雷达信号处理主机间的大量高速数据和控制命令传输。根据本系统中数据下行传输的要求,需要将DBF后的16 bit /100MSPS的基带I/Q信号传输到信号处理主机,最大数据流为2*16*100 Mbit/s,高速串行数据的稳定收发通常需要经过编码,在本系统中使用8B/10B 编码,编码后的最大数据流为2*16*100*8/10 Mbit/s=2*2 Gbit/s。LVDS所需路数太多,工程可用性差;同时考虑到主控FPGA 自身的GTP 支持高速串行传输,其最高传输率为3.2 Gbit/s,所以可使用GTP;传输介质选用光纤,光纤可以保证数字接收机与雷达主机之间高速大容量、高可靠的远距数据传输,不受高能电磁场的影响。当GTP 工作在2 Gbit/s时,选用两路光纤即可满足数据下行传输需求。上行数据传输主要是控制指令,速率很低,一路光纤即可满足需求。选用2个Finisar 公司生产的双工光收发模块,其最高转换速率为4.25 Gbit/s,最大传输距离550 m,分别用于两路下行通道和一路上行通道。

2 测试及结果

工作频带内的SNR、幅相一致性和稳定性是多通道宽带数字接收机的重要参数,所以对设计样件的上述性能指标进行了测试。测试是在常温、室内条件下进行的,测试所得结果是进行后续系统设计的重要参考。

2.1 SNR测试

Agilent N5183A 型信号源提供频率200 MHz的单频信号作为8 通道宽带数字接收机的工作时钟,同样类型的信号源提供八路模拟中频输入信号。采用FFT法测试ADC 输出信号的信噪比,选取的点数为16384,设置信号源的频率分别为:从200.2905273 MHz 始,以10MHz为步进至300.2905273 MHz。测试中在各个频点逐渐增加输入信号功率,使ChipScope采集回的各通道数字信号的幅度满足-1dBFS,导出当前ChipScope中的数据并计算该频点各通道的SNR[8]。样件8个接收通道工作频带内的SNR测试结果见图4。

图4 8个接收通道在工作带内的SNR测试结果

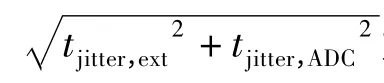

2.2 幅相一致性测试

图5 通道间的同频点幅度一致性测试结果

通道间的一致性是指同频点多通道间幅度和相位的相似性。该处测量的是修正前的数据,直接反映了接收机的设计和加工工艺水平。选第1 通道作为参考通道,在同一输入频点上,使用FFT 法计算各通道的幅相与参考通道的幅相差。工作频带内的幅度一致性见图5,相位一致性见图6。可以看出,通道间同频点的幅度差小于±0.2 dB,相位差小于±4°。

图6 通道间的同频点相位一致性测试结果

2.3 幅相稳定性测试

幅相稳定性是指接收机通道的幅度、相位随时间变化情况。只考察在1 h 内各路接收机之间的幅相稳定性。测试方法与2.2 相同,多次幅相测试的结果如图7、图8所示。可以看出,通道间的幅度和相位稳定性很高,经计算分别为0.01 dB(rms)和0.025°(rms)。

图7 8个通道间的同频点幅度稳定性测试结果

图8 8个通道间的同频点相位稳定性测试结果

3 结束语

本文针对DBF 体制的多通道宽带接收设计提出了数字中频的解决方案。该方案采用FPGA 作为整个数字接收机的主控和信号处理核心,使用多通道高速ADC 对信号进行宽带采样,使用数字时钟分配芯片给各个ADC 提供统一的时钟,使用光纤作为大容量高速数据传输手段,解决了传统设计的通道间幅相一致性和稳定性问题,达到了较好的DBF 接收性能。

[1]弋稳.雷达接收机技术[M].北京:电子工业出版社,2005.4.

[2]Merrill I.Skolnik.Radar Handbook[M].3rd Edition.McGraw -Hill Companies Inc,2008.

[3]李海英,杨汝良.去斜率线性调频合成孔径雷达成像研究[J].现代雷达,2003,25(3):8-10.

[4]宋千,梁甸农.宽带线性调频雷达数字去调频直接采样技术[J].现代雷达,2001,23(6):48-51.

[5]徐成节,黄巍,陈祝明,等.宽带LFM信号数字脉压匹配滤波和去斜率方法的比较[J].雷达科学与技术,2004,2(3):168-712.

[6]郭崇贤.相控阵雷达接收技术[M].北京:国防工业出版社,2009.7.

[7]Brad Brannon,Allen Barlow.Aperture Uncertainty and ADC System Performance[M].Analog Device An501,2006.

[8]Brad Brannon,Rob Reeder.Understanding High Speed ADC Testing and Evaluation[M].Analog Device AN835,2006.