GNSS模拟器中频源D/A设计与实现*

卢 杰,张 波,杨东凯

(北京航空航天大学电子信息工程学院,北京100191)

0 引 言

GNSS卫星信号模拟器用来实时模拟不同条件下接收机天线端接收到的多路卫星信号。可充分模拟动态载体运动过程中接收机遇到的各种复杂情况,为接收机特别是兼容接收机的研制开发、测试阶段提供仿真环境,同时也可用于系统级仿真验证和系统兼容性测试从而可在系统建设论证初期完善设计方案。

GNSS模拟器主要由上位机、中频和射频模块三部分组成,而中频模块作为信号产生的主体部分是整个系统的一个重要部分。中频模块接收上位机数据转换为导航信号,然后进行数模转换生成中频模拟信号给射频模块。设计了一个基于AD9779A的中频模块,通过将FPGA产生的GNSS信源基带数字信号转换成可供正交调制的I、Q两路模拟中频信号。

1 系统架构

GNSS模拟器在中频模块一般先产生基带数字导航信号,所以导航信号在数模转换的同时要求进行上变频。根据系统分析GNSS模拟器数模转换的总体设计如图1所示,主要包括信号生成模块、时钟模块、A/D控制模块和数模转换模块。本设计通过FPGA接收上位机数据产生数字基带导航信号,然后A/D控制模块使AD9779A实现相关寄存器的配置并在时钟模块提供的基准差分时钟下进行采样完成带上变频功能的数模转换。

图1 总体设计框图

上变频功能的数模转换主要有两种实现方式:1)数字信号在上变频的基础上进行数模转换;2)数模转换后对模拟信号进行上变频。AD9779A具有带上变频功能的数模转换,将数字信号转换模拟信号同时进行上变频从而使设计简单、容易实现。本文的重点是对AD9779A电路设计和功能配置。

2 AD9779A相关电路设计[1]

AD9779A是Analog Devices公司生产的16位双通道、高动态范围的数模转换芯片,提供1 Gsps采用率。还包含低噪声高性能的PLL时钟倍频电路,可以减少板级时钟输入的负担。

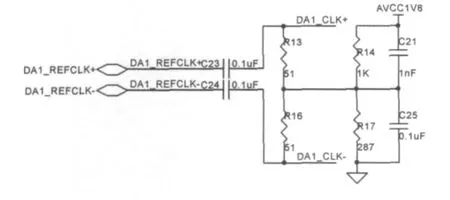

2.1 差分时钟电路设计

AD9779A通过两种模式提供DAC采样时钟:第一种是采用片内时钟倍频器,能接受一个较低输入频率工作的参考时钟;第二种模式是旁路时钟倍频电路,让DACCLK直接通过REFCLK引脚提供。无论何种情况要求REFCLK信号抖动很低,尽可能提高DAC噪声性能。差分时钟的质量关系整个数模转换的性能,是正确采样和内插的根本。

因为高频信号会引起信号之间的互相干扰,而且稳定度也差,本设计采用第二种方式通过FPGA提供较低频率的差分时钟信号(50MHz),当摆幅达到1.6V峰峰值,PLL就能实现最佳幅值。

参照AD9779A手册的REFCLK的电气规范要求DAC时钟输入差分峰峰值电压为800mV,共模电压为400mV.REFCLK的差分时钟由Virtex6提供,为使差分峰峰值电压达到800mV,采取LVPECL_25差分标准。但REFCLK的共模电压达到1.2V,为提供400mV共模电压,所以对FPGA提供的差分时钟进行交流耦合,再加外部400mV的共模电压,电路设计如图2所示。

图2 差分时钟电路设计

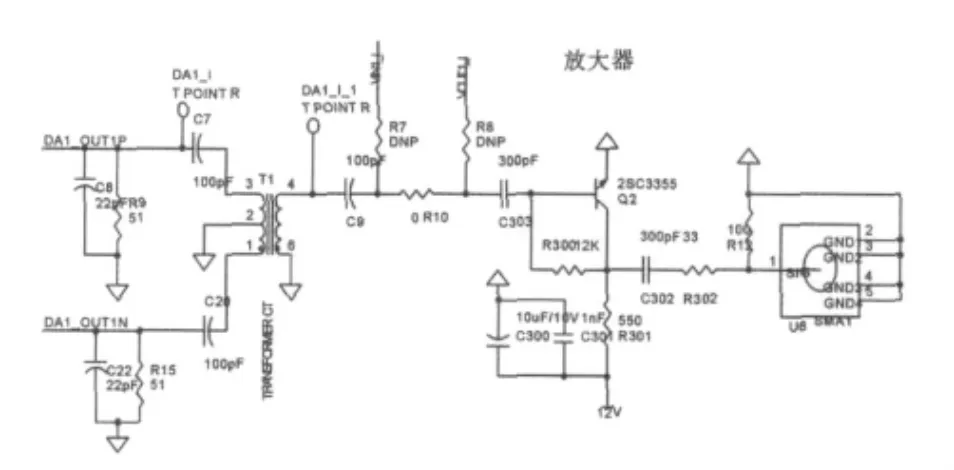

2.2 AD9779A外部模拟滤波器设计

AD9779A输出的差分模拟信号耦合输入一个抗混叠滤波器,再经过放大器提高信号增益,提供给射频模块。GNSS导航信号(载波频率210 MHz,带宽2.046MHz)处理过程和时钟源中参杂很多低频分量,所以滤波器设置为高通滤波器。具体电路如图3所示。

因为载波频率达到210MHz而信号带宽很窄,对信号放大很难找到现成的放大器,本设计采用2SC3355三极管放大电路实现。

图3 模拟高通滤波器设计

2.3 其它相关设计

本设计通过FPGA实现控制模块对整个系统的控制。控制模块接收上位机数据,使信号生成模块产生GNSS模拟器的I/Q两路基带数字信号。为实现模拟中频输出分别将I/Q两路信号送给的端口1和端口2,各ADC均从专用输入端口接收数据,使AD9779A工作在双端口模式。双端模式下发送使能端口(Txenable)用来关断数字数据路径,设计中将此管脚与FPGA相连配合自动掉电使能位控制器件掉电和休眠功能,从而降低功耗。AD9779A的SPI四根接口线与控制模块相连,配合通过FPGA控制模块的设计实现在三线或四线模式下的数据传输,从而实现对各寄存器的配置。

AD9779A采用先进的0.18μm CMOS工艺制造,采用1.8V和3.3V电源总功耗为1.0W.AD9779A支持的最高采样速率为1 100MHz,但对DVDD18和CVDD18有限制。通过12V直流稳压电源转换实现供电,采取TPS73801转换芯片提供3.3V,为更好实现稳定度,1.8V在3.3V的基础上通过LT1963A转换实现。

3 AD9779A寄存器配置[3]

AD9779A是通过SPI接口与外部控制模块通信,设置各种功能达到设计的要求。采用标准的四根接口线进行通信,当然也可以配置为3线SPI接口。通过串行接口实现与外部通信读取控制字,从而可以设置优化各种功能达到最佳性能。通信周期可分为两个阶段:第一阶段是指令周期,与前8个SCLK上升沿重合。指令周期提供数据传输周期的信息,包括数据传输是读操作还是写操作,数据传输有多少字节以及起始寄存器地址。第二阶段是实际进行数据传输的阶段,根据指令字节提供的信息配置内部相关寄存器。通信方式支持单字节或多字节传输,包括高位优先和低位优先格式。

AD9779A内部总共32个寄存器,每个寄存器8位,每位都有自己特定的功能。根据具体设计要求设定寄存器,所有不用寄存器位应保持器件默认值。寄存器控制功能主要分数字控制、同步控制、PLL控制、通道I/Q控制和中断控制,本设计重点通过数字控制和PLL控制实现信号上变频数模转换。

3.1 AD9779A的数字控制配置

数字引擎采用集插值滤波器和数字正交调制器于一体的创新滤波器结构,所以能执行数字正交上变频。数字控制主要通过设置0x01和0x02寄存器,设置插值系数、滤波器调制模式和数据格式等实现。

本设计中为了实现信号从10MHz上变频到带宽为2.046MHz的210MHz中频信号。因信号带宽较窄且为实现上变频后载波频率,可知道将AD9779A设置为对数据进行8倍内插的无偏移的fDAC/4滤波器调制模式。因输入数据为互相正交的两路基带调制正弦波信号,数据格式设为二进制补码形式。双通道模式下复数信号的实部和虚部分别出现在数字输入端口1和端口2经复数载波调制,DAC输出分别代表输入信号的实部和虚部,因此同时设置使能16位数据P1D和P2D,且输出I/Q路都被使能输出。为了配合AD9779A自动调整采用时钟和输入数据之间的采样位置优化数据采用结果,使能DATACLK DELAY和反sinc滤波器,使输出的模拟信号变平坦。

3.2 AD9779APLL的配置

PLL配置[2]是AD9779A配置中的另一个重点,这个模块提供DAC采样时钟直接影响D/A实现,其中相关的主要是0x08和0x09寄存器。AD9779A的PLL VCO(压控振荡器)最佳工作范围1.0~2.0GHz,时钟倍频电路从较低频率的REFCLK输入产生DAC采样时钟,同时使VCO输出频率fvco锁定在相应的频带内。

根据数字控制配置可知为实现中频载波210 MHz可求的fDAC为800MHz,同时为VCO在工作范围内通过公式(1)和(2),可知道通过FPGA产生50MHz的REFCLK时钟,同时设置N1和N2分别为16和2可以实现功能要求。

PLL在环境温度下的频带优化锁定,AD9779A的VCO有效运行范围里有63个频率重叠带。对于期望的VCO输出频率有多个有效的PLL频带供选择,且会随温度的变换而变换,各频带中心频率随温度的升高而降低,随温度的降低而升高。每个器件在特定的温度下都有一个最优的PLL频带值,不同器件之间也有30~40MHz的误差。器件具有片内PLL频段自动选择特性,当使能时将自动确定给定温度下的最佳PLL频段设置,且此值在温度±60℃变化幅度内始终有效。因模拟器通常工作在室温条件下,通过读取可知设置VOC的频率范围为100 111.

4 系统实现与验证

GNSS模拟器数模转换设计中FPGA主要实现信号生成模块、时钟模块和A/D控制模块[4]。FPGA通过接收上位机数据产生数字基带导航信号,A/D控制模块使AD9779A实现相关功能。设计的重点是A/D控制模块,通过本模块根据上文所分析的寄存器配置实现AD9779A的功能,从而实现上变频的数模转换。

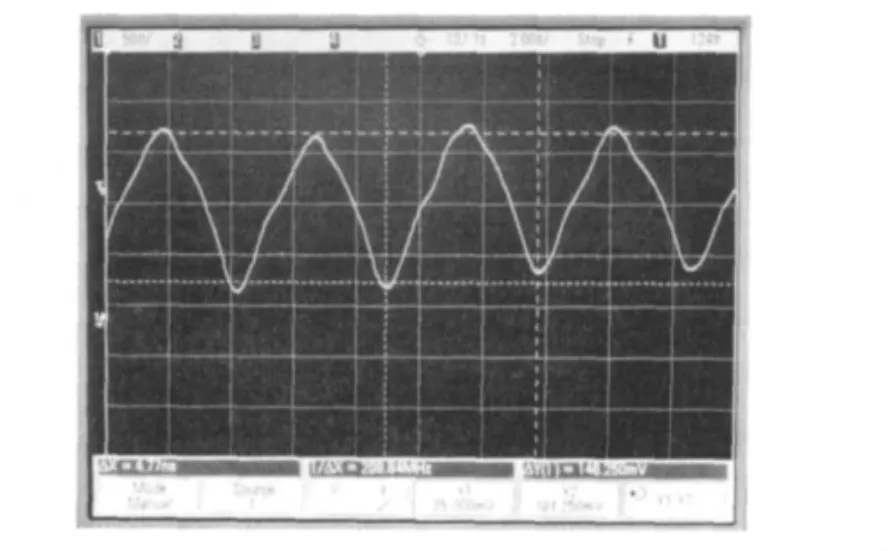

通过产生GPS的L1的C/A码基带数字导航信号,A/D控制模块使得AD9779A在时钟模块提供参考时钟(REFCLK)基础上输出中频模拟信号。通过示波器和频谱仪观察模拟器数模转换设计的GNSS导航信号,通过分析验证设计正确。测试结果如图4和5所示。

图4 模拟源正弦信号

图4示出了基带数字导航信号经AD9779A转换后输出的中频模拟信号,图5则是相应的频谱图。通过观察可知输出的载波中心频率为210 MHz,带宽为2.04MHz.理论输出应该是在210 MHz的载波上调制1.023MHz的导航数据,符合设计要求只是存在小量的低频分量。射频板具有滤波功能,可直接输入本中频信号。

图5 模拟源信号频谱

5 结 论

通过电路设计、寄存器配置和系统实现和验证等三个部分,介绍如何实现GNSS模拟源数模转换设计。AD9779A是中频源设计的关键部件,实现数模转换同时进行信号上变频。通过测试频谱符合设计要求,仍然有杂散信号存在特别是基带载频的泄漏,通过外部滤波器的性能和AD9779A的寄存器配置上着手考虑进一步优化信号质量。

本设计与以往设计[5]中采用将数字信号先进行内插到所需中频再进行数模转换相比具有设计简单、易于集成和模块化。所述的数模转换已经在多星座可重构GNSS仿真验证平台的模拟器设计中成功应用。

[1] 徐启炳,张立新.Cadence高速电路板设计与仿真[M].北京:电子工业出版社,2009.

[2] ANALOG DEVICES.AD9776A/AD9778A/AD9779A Dual,12-/16-Bit,1GSPS Digital-to-Analog Converters Data Sheet(Rev.B)[R].2008.

[3] 蔡 翔,伍彩琴.AD9779A的寄存器配置及PLL频带优化[J].单片机与嵌入式系统应用,2011,11(1):36-39.

[4] 田 耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008.

[5] ZHU Yuhong,KOU Yanhong,CHANG Qing,et al.Hardware design and implementation of a multichannel GPS simulator[C]//International Telemetering Conference,USA.2004.