TMR+Scrubbing SRAM加固型FPGA辐照实验研究

孙 野,陈晖照

(山东航天电子技术研究所 通信事业部,山东 烟台264003)

由于静态存储器(Static Random Access Memory,SRAM)型现场可编程门阵列(Field Programmable Gate Array,FPGA)与反熔丝型FPGA相比具有可反复重新配置的优点,所以SRAM型FPGA在航天领域受到广泛关注。但SRAM[1]为辐射敏感器件,这严重威胁了卫星安全可靠的运行。国内外对航天故障的统计显示:约有40%的故障源自太空辐射[2]。近10年来,国内外一直重视SRAM FPGA辐射效应和加固方法研究。本文研究了三模冗余(TMR)和 动态刷新(Scrubbing)两种加固措施,并对采取措施的FPGA和未采取加固措施的FPGA进行单粒子辐照实验研究,成功验证了TMR+Scrubbing加固措施的有效性,试验结果显示,TMR+Scrubbing加固措施可以提高SRAM型FPGA抗单粒子性能2倍以上。

1 TMR+Scrubbing加固设计

1.1 TMR加固设计

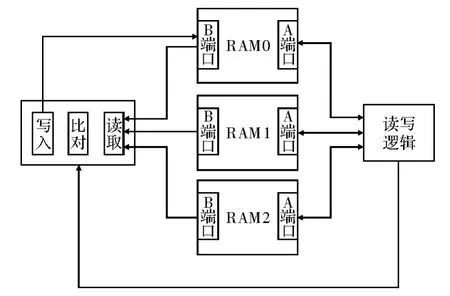

FPGA内部的RAM资源相对寄存器、查找表等资源较为丰富,而且都可以采用双端口方式访问,当正常逻辑只操作一个端口时,可以采用图1所示方式对RAM模块进行三模冗余处理,当正常逻辑使用RAM模块的A端口时,自刷新模块使用B端口同时读取3份RAM中的数据,进行读取→比对→回写的操作。如当RAM模块1中数据有错误时,自刷新模块经比对发现该模块存在错误后,保存错误数据存在的地址,同时检测正常逻辑在端口A的操作信号,当发现正常逻辑没有对数据错误存在的地址进行写操作时,立即通过端口B对RAM模块1的数据错误地址写入正确的数据。为保证自刷新模块自身的可靠性,对自刷新模块进行模块级三模冗余。

图1 RAM三模冗余自刷新处理框图

在一般通信系统中,借助查找表法实现载波NCO或者滤波器,因此正弦表、反正切函数表、滤波器参数等重要的运行参数一般存在于FPGA的内部ROM中,由于ROM只是使用双端口RAM资源的一个端口,因此可以通过另一端口实现三模冗余和自刷新,具备可恢复能力。3个RAM的三路信号(douta_tr0douta_tr1douta_tr2)输出后经过表决器比对,输出一路信号(doutb),在正余弦表单元中,TMR单元信号处理如图2所示[3]。

图2 正余弦表TMR单元信号处理

三模冗余对资源的占用量是原始设计的3.2~3.5倍,因此不能对整个FPGA逻辑设计进行三模冗余,只能选择对关键模块和所有模块中长时间存在的关键变量进行三模冗余。长时间存在的关键变量主要是指:主程序的大循环控制变量、主程序的有限状态机控制变量、重要的全局标志等等,这些变量关系到FPGA运行程序的总体进程,而且存在的时间比较长,发生单粒子翻转的概率比一些临时局部变量大的多,影响也更加严重[4]。

1.2 Scrubbing加固设计

在Scrubbing过程中对配置流数据进行回读、比对,当发现配置数据有错误时,对存在错误的部分配置区进行局部重配置,消除错误数据。进行Scrubbing时,可以不中断FPGA的正常工作,该措施在FPGA工作期间同步运行,以最快的速度检测到配置区数据错误并纠错,可以有效地防止配置区数据累积,将错误影响的时间间隔缩小到一个回读、比对周期所需的处理时间。在这个过程中分3步:配置流回读、比对、局部重配置。

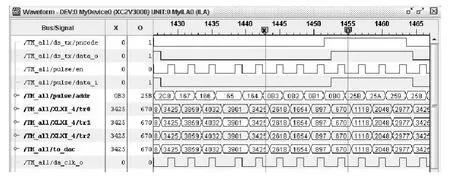

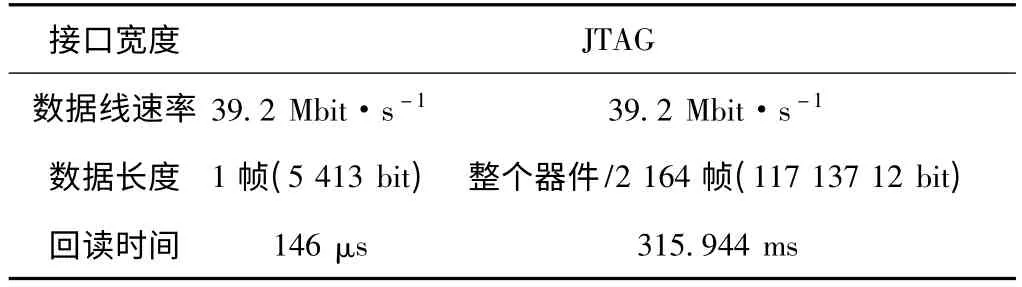

回读是通过JTAG接口从配置区中回读出FPGA内嵌逻辑的运行状态量,据此判断逻辑是否运行正常。回读过程可以读出CLB、IOB的寄存器和FPGA的内部存储器的当前状态,以及布线资源的配置情况等,然后通过回读数据的校验来检验当前配置数据的正确性。

表1 XQRV3000配置存储器动态回读的时间特性

表1所列为XQRV3000动态回读的时间特性。经过实验测试,JTAG接口最快的访问速率约可达55 Mbit·s-1。这里以39.2 MHz作为回读时钟,根据表1中的参数可以计算得到:每帧数据的回读时间约为150μs,整个器件的回读时间约为270 ms。SRAM型FPGA配置区的部分数据反映了硬件结构内部的寄存器内容,而FPGA内嵌逻辑中又使用了硬件结构中的寄存器,实际上配置区的部分数据位充当了内嵌逻辑中变量的影子寄存器,可以从这些影子寄存器中探测FPGA内嵌逻辑的工作状态。

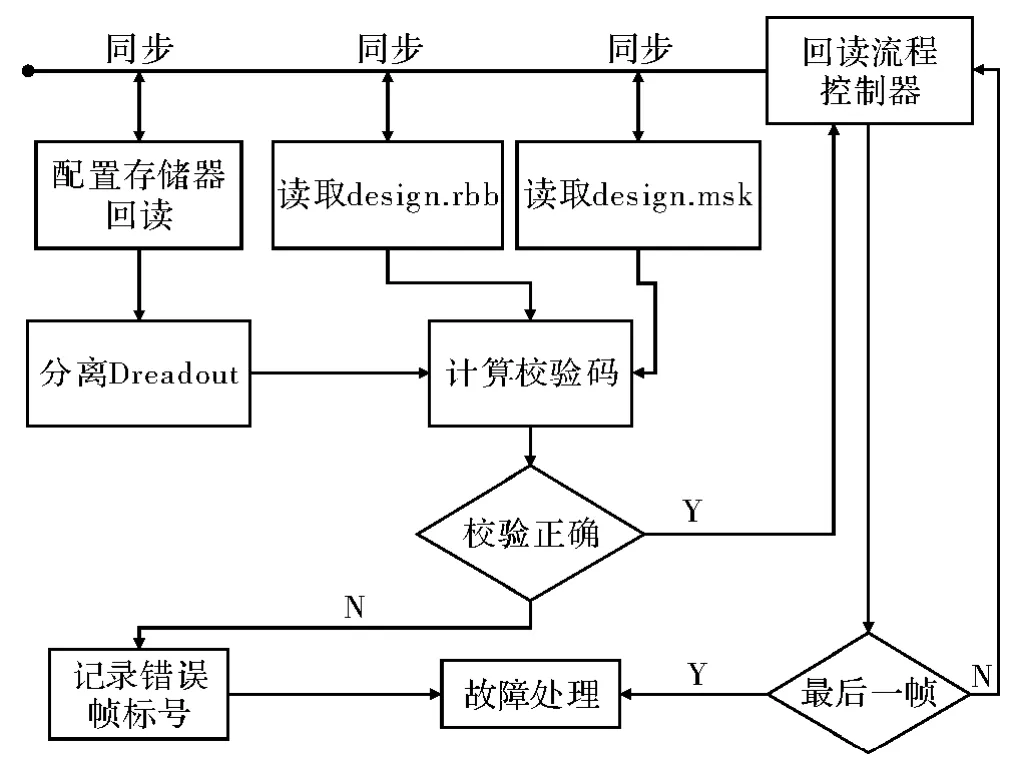

比对就是将标准数据和回读数据逐位进行比较,也就是直接比较校验。这个过程需要两个专用的存储区域分别存储屏蔽数据文件(design.msk)和回读后应该得到的标准数据(design.rbb)。这两个文件可以在生成配置数据(design.bit)时一并生成。由于某些临时性数据,比如Distributed RAM,在FPGA工作的过程中会发生变化,因此比对时需要将此部分内容屏蔽掉[5]。即在直接比较校验过程中,需要比较的是校验码是否相等,如果不相等则说明回读的数据出现翻转错误。回读数据的直接比较校验流程如图3所示。

图3 配置存储器回读数据的直接比较校验

局部动态重构是指在不中断FPGA其他功能模块正常时序条件下,实现的故障区域的局部重配置。在FPGA发生单粒子辐射效应故障时,HRU通过对FPGA状态的监控、配置存储器的回读校验等措施,可以将故障定位于功能模块对应的布线配置区域。

在样品FPGA和配置数据存储PROM器件间加入一块Actel反熔丝型FPGA,由该Actel FPGA充当样品FPGA的配置控制器,负责对样品FPGA进行动态刷新。

2 试验验证

试验采用辐照中测试,辐照失效判据为功能失效。首先为了验证TMR+Scrubbing加固方法的有效性,采用相同注量率的B粒子分别照射无加固措施的样品和采用TMR+Scrubbing加固的样品,在试验过程中观测样品功能是否失效[6]。

表2 平均中断粒子数与加固模式关系

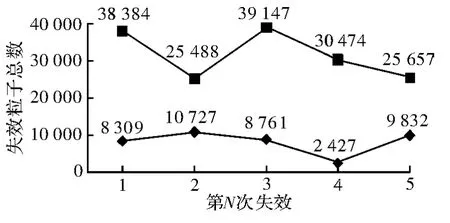

根据实验数据,获得中断粒子总数与第I次翻转关系曲线如图4所示。

图4 失效粒子总数与第N次翻转关系曲线

注量率对比实验过程中,样品功能失效时立即停止辐照,待测试系统重新开机,实验样本进入正常工作状态之后继续辐照,失效粒子数累积计量。

3 结束语

通过B粒子相同注量率(60 Ions/cm2·s)下不同检测模式的对比实验可以得出结论,TMR+scrubing加固方式可以将SRAM型FPGA抗辐射性能提高2倍以上。实验成功验证了TMR+scrubing加固方式可以提高SRAM型FPGA抗辐射性能。为TMR+scrubing加固研究提供了数据依据。需要注意在实际工程实现中,并非所有功能都可以刷新,也有一些功能由于FPGA资源有限的原因,不能三模冗余,这些资源有可能会成为TMR+scrubing FPGA抗辐射性能的短板,使用时需谨慎。

[1] 韩郑生.抗辐射集成电路概论[M].北京:清华大学出版社,2011.

[2]PHILIPPE A,GREG A.Assessing and mitigating radiation effects in xilinx FPGA[M].Pasedena,California:Propulsion Laboratory California Institute of Technology,2008.

[3]REED R.Implementation of a BPSK transceiver for use with the university of kansas agile radio:bachelor of science[D].Kansas:University of Kansas,2004.

[4] 辛明瑞,时晨,高德远,等.面向空间应用的片上系统集成技术研究[J].微电子学与计算机,2006,23(6):194-197.

[5] 段青亚,黄士坦,辛明瑞.空间单粒子故障容错设计的验证技术研究[J].微电子学与计算机,2007,24(11):38-41.

[6] 刑克飞,张传胜,王京,等.数字信号处理器抗辐射设计技术研究[J].应用基础与工程科学学报,2006,14(4):572,578.