基于FPGA的变压器绕组变形测试仪研制

陈 超

(韶关曲江供电局,广东 韶关 512100)

变压器绕组变形是导致变压器发生损坏事故的主要原因之一。因此,对受短路冲击后的变压器应进行绕组变形测试,以确保变压器的安全稳定运行[1]。变压器绕组变形测试的方法有低压脉冲法、频率响应分析法和短路电抗分析法。其中低压脉冲法和短路电抗法的灵敏度低,判断方法复杂,而频率响应分析法具有灵敏度高、试验设备轻便、判断直观的优点[2]。目前国内对频率响应分析法仪器的研究主要是分立设备法和模拟分析法[3-4],分立设备法操作麻烦,抗干扰能力不强,模拟分析法不能解决实际问题。为此笔者结合所学知识,运用FPGA作为主控芯片,利用FPGA并行处理和可以嵌核的特点,结合DDS技术,研制了变压器绕组变形测试仪,该仪器可测变压器绕组的幅频特性曲线和相频特性曲线。

1 频率响应法原理

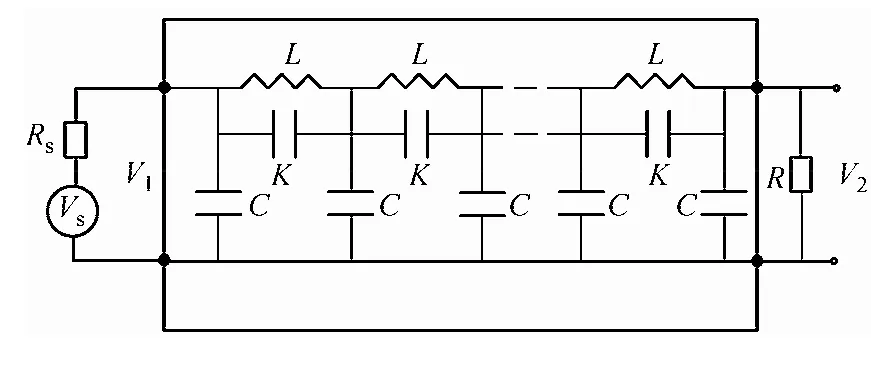

变压器绕组是由线圈绕在铁心上,由于线圈有一定的电感和电阻,同时线圈之间也存在电容。因此变压器绕组可以等效成电阻电容和电感组成的网络[5],在高频信号的作用下,变压器绕组的频率特性可以用传递函数H( j)ω描述。根据变压器绕组的特性,变压器绕组在频率响应下的等效电路如图1所示。图中L为变压器绕组单位长度的分布电感,K为变压器绕组的纵向分布电容,C为变压器绕组的对地分布电容;V1为变压器饶组测试端所加电压,包括幅值和相位,V2是变压器绕组响应电压,同样也是矢量。VS为正弦波激励信号源电压,RS为信号源输出阻抗;R为匹配电阻。

图1 变压器绕组等效电路和频率响应分析测试电路

由前面的分析可知,变压器绕组的等效电路在出厂后是固定的,同时其在不同频率下的响应特性也固定。但是如果变压器在运行过程中出现绕组变形,其电阻电感和电容都会发生不同程度的变化,导致变压器绕组等效电路发生变化,同时其等效电路的频率特性也会发生不同程度的变化。变压器绕组的幅频响应特性采用扫频检测法获得,即连续改变激励端的频率f(角频率ω=2π f),测量不同频率下的响应端电压V2和激励端电压V1的信号幅值之比,并进行如下处理:

从上面的分析可知,可以先对出厂变压器的频率特性进行测量存档,再次检修时再次测量其频率特性并和出厂时频率特性进行比较,可以判断变压器在运行过程中是否发生绕组变形。

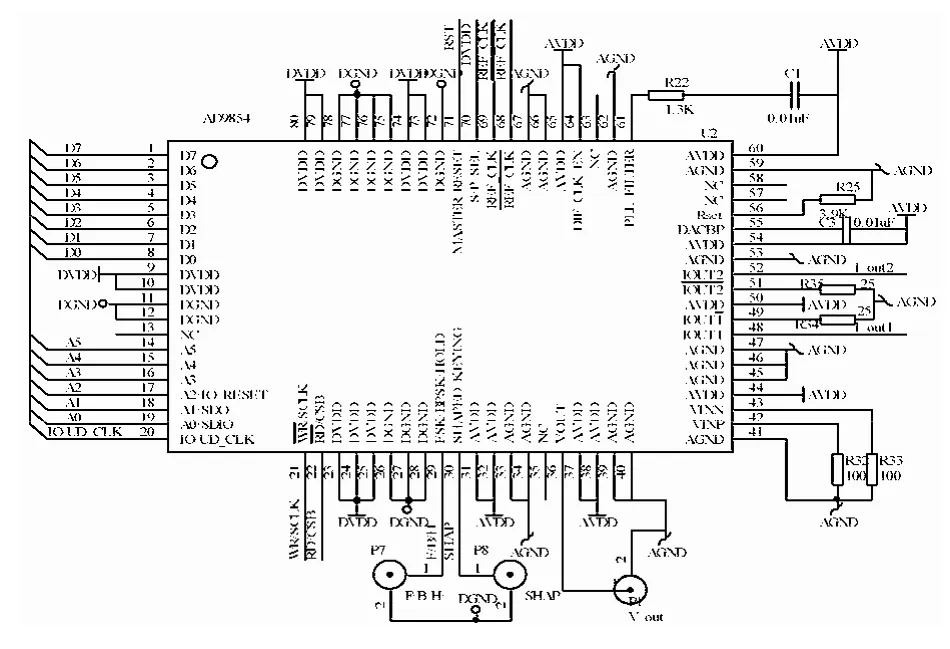

2 系统总体设计

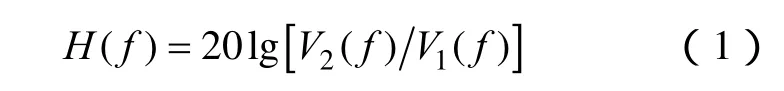

变压器绕组测试仪总体框图如图2所示。其工作原理是从键盘输入起始频率、截止频率、步进频率、步进间隔和测试要求,FPGA根据输入内容控制AD9854产生扫频信号,经滤波,放大后加到变压器绕组,由信号调理电路对放大后和变压器输出信号进行调理,以满足AD采样的要求,然后双通道AD对变压器的输入信号和输出信号进行数据采集,送入FPGA处理后在LCD上输出幅频曲线或相频曲线,也可将数据通过RS232串口传输给上位机,由上位机对信号进行处理。其中信号调理电路包括信号衰减电路和有效值转换电路,多路开关用来选择进入AD的是正弦波信号还是经有效值转换的信号,两种信号分别用来测试幅频和相频曲线。

图2 系统总体框图

3 系统硬件设计

FPGA(Field Progrunmable Gate Array)有很多自由的门,通过将这些门连接起来形成乘法器、寄存器、地址发生器等,其中先进的FPGA可以进行嵌核[6]。本设计选用FPGA的主要原因是其可嵌核和数据的并行处理。由于系统设计要能达到测试变压器绕组的幅频特性和相频特性,所以要求AD的采样速度比较高,同时又要控制DDS产生扫频信号,可嵌核的FPGA能够满足本设计的要求,用核来控制DDS产生信号,用并行处理来控制采样,同时也免除了多处理器的问题。测幅频特性如果能够直接测量输入和输出的有效值,就减少了核的处理数据量,所以在本设计中设计了既可以直接测输入和输出信号,也可以测经有效值转换后的信号,两种信号的切换通过多路开关来选择。下面介绍主要单元模块电路的设计。

3.1 正弦波产生电路

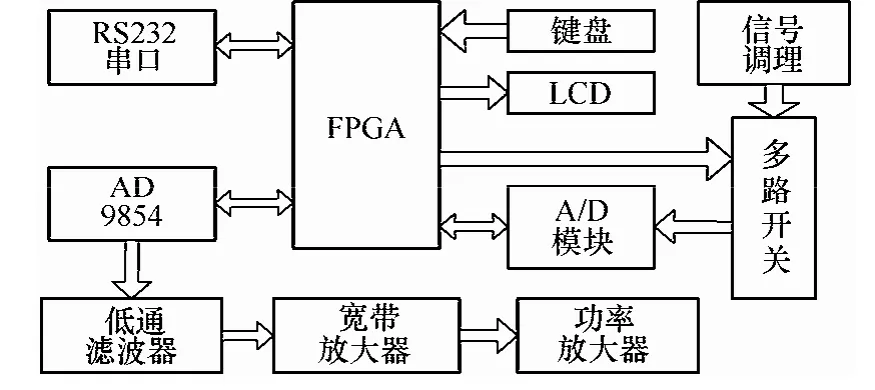

本系统设计的信号发生器采用DDS技术的芯片AD9854[7],AD9854原理图如图3所示,时钟采用40MHz有源晶振,控制方式采用并行方式,最高输出频率控制为8MHz,可以满足变压器绕组变形检测信号源的频率要求。

图3 AD9854原理图

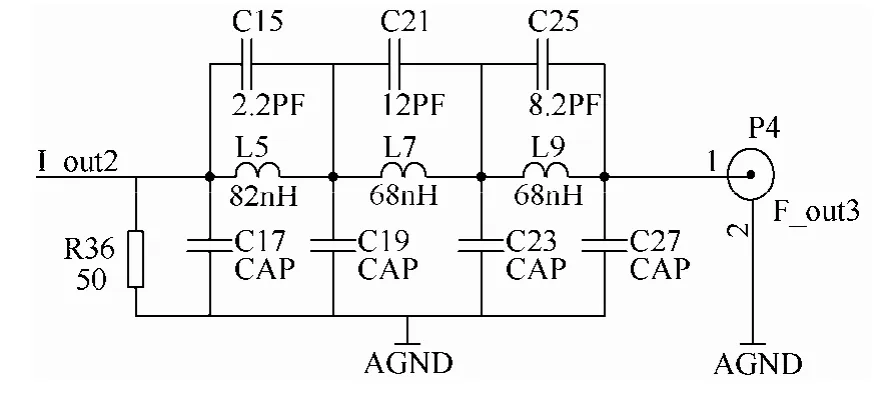

3.2 滤波电路

由于AD9854输出的是采样信号,虽然其内部对信号进行了一定处理,但还是不可避免的含有谐波信号。在滤波电路上采用25MHz的7阶切比雪夫低通滤波器,使信号波形纯洁,失真度大大减少,其电路图如图4所示。

图4 7阶切比雪夫滤波器

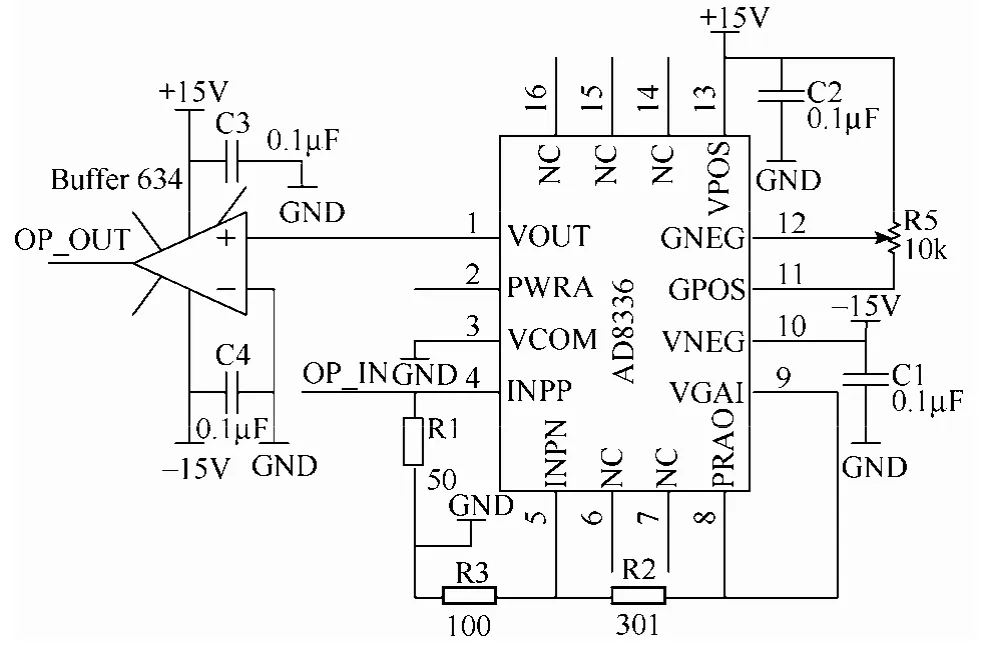

3.3 放大电路

仅靠AD9854的输出信号达不到变压器绕组变形测试仪扫频信号的要求,为此要设计信号放大和功率放大来满足变压器绕组测试的信号的要求。对于信号放大电路,为了满足对设备对不同电压的要求,选用宽带且放大倍数可调的AD8336。AD8336是一款低噪声、双端、线性dB、通用型可变增益放大器,可以在较大的电源电压范围内工作。它内置一个非专用前置放大器,可用增益范围为6~26dB,采用传统方式通过外部电阻确定,VGA增益范围为0~60dB,该放大器在80MHz内完全可用[9];对于功率放大电路,选用Buffer634。Buffer634是一款高速缓冲器,带宽30~180MHz,输出电流最大可达250mA,最大输出电压峰峰值36V,可满足系统对电压和电流的要求。AD603和Buffer634原理图如图5所示,其中调节变阻器R5可调节AD8336的放大倍数。

图5 放大电路原理图

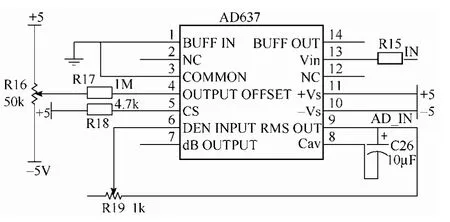

3.4 有效值转换电路

为了使幅频特性测试变得更加容易实现,在本设计中用到了两路有正弦波有效值转换。由于扫频的高低频相差较大,在有效值转换中选用AD637。AD637是一款完整的高精度、单芯片均方根直流转换器,误差小于1%。宽带宽允许测量200m V均方根、频率最高达600kHz的输入信号以及1V均方根以上、频率最高达8MHz的输入信号[10]。AD637应用电路如图6所示从13脚输入经信号调理后的信号,9脚输出正弦波电压的有效值。

图6 AD637原理图

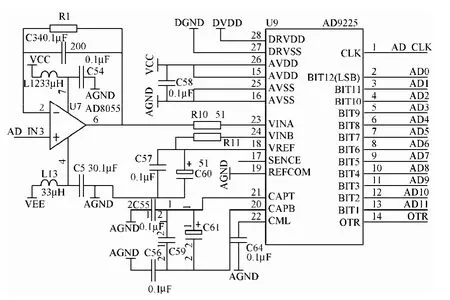

3.5 AD转换电路

由于采用了有效值转换电路,在幅频特性测量时可用低速AD,然而由于要测相频特性,且DDS信号源的输出可达8MHz,这就要求AD速度至少要达到16MHz,同时也为了数据采集方便,在本设计中选用速度可调的且精度较高的AD9225[11]。由于AD9225的输入阻抗较小,为了保证信号不因与AD相连而产生失真,需在AD前加一级跟随,在这里跟随选用AD8055,可满足对输入阻抗和带宽要求。AD8055和AD9225连接原理如图7所示。AD基准采用内部基准源,同时为了保证数据采集不因采集不同时而给数据处理带来麻烦,在这里选用两片AD9225来采样,两片的时钟接在一起,这样可以保证输入和输出采样是在同一时间进行,方便数据处理。

图7 AD9225原理图

4 系统软件设计

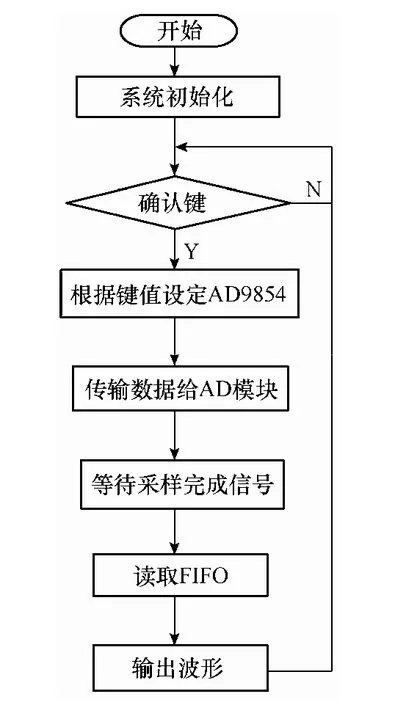

FPGA软件设计主要包括基于FPGA的C语言的主程序设计和Verilog HDL语言的AD数据采集程序设计。为了以下叙述方便,定义扫频起始频率为f1,截止频率为f2,频率更新间隔为tjg,频率更新间隔为Δf,AD时钟为tclk。主程序先从键盘读取测试功能、f1、f2和tjg,计算出AD9854要写入的数据和tclk,然后设定AD9854,传输数据给AD采样模块,等待AD采样模块给出频率达到上限的信号,读取采样数据,输出波形图。主程序流程图如图8所示。

图8 主程序流程图

在这里介绍一下AD9854实现扫频的实现。AD9854 有5种工作模式,分别为Single-Tone(Mode 000)、FSK(Mode 001)、Ramped FSK (M ode010)、Chirp(Mode 011)和BPSK(Mode 100),模式选择可在控制寄存器里进行修改。本设计主要用到AD9854的扫频功能,故可选用Ramped FSK模式,该模式其相位则由相位控制字P1决定,频率跳变时相位保持连续。频率控制字F1和F2低频率和高频率,输出时从F1到F2扫描扫描间隔和速度都可以控制。采用Ramped FSK的好处是可以对变压器绕组任意频段进行测量。

对于波形图的绘制,在要求测量幅频特性时,NIOS Ⅱ核控制采样速度和频率更新速度相同,且AD时钟滞后频率更新tjg/2,由于采用了正弦波有效值转换,滞后tjg/2可以保证采出来的是同一频率的有效值,根据式1可以直接得出该频率下的输出和输入的幅值之比,整个频段内所有采样点之间有平滑曲线连接即可得出整个频段的幅频特性。在频标问题上由于已知f1、f2和Δf,且采样点数为(f2-f1)/Δf+1,因此可以根据f1、f2和Δf在LCD上快速标出频标。在相频曲线上原理的幅频曲线上主要是采样点数的差别和相位差的计算,频标问题和幅频特性一样,在这里不再叙述。

为了保证两路AD数据采集的同时性和实时性,AD数据采集用Verilog HDL程序控制。两路AD时钟用同一时钟,且该时钟受核控制,可以从0~25M连续可调,保证两路数据采集同时进行。数据采集后先放入FIFO中,消除NIOS II核的处理速度较慢的问题,等扫频完成后再传输到NIOS Ⅱ核进行处理。Verilog HDL程序功能是先读取从NIOS Ⅱ核中传输的测试功能、f1、f2、tclk和tjg等量,然后计算出要采集的数据数和采样速率,开始对信号进行采样。由于Ramped FSK不会在输出达到最高频率时自动停止,所以在AD采集完所有数据后,要通知NIOS Ⅱ核关闭DDS。

5 系统试验及结果分析

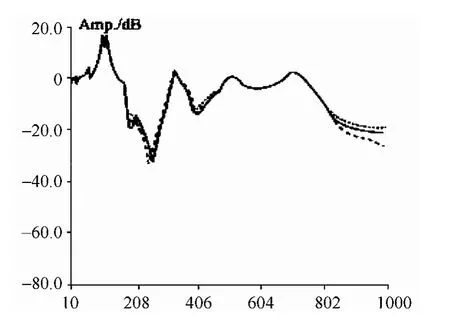

本装置主要功能是用于测量变压器绕组的频率响应特性。在实验室采用本装置对一台三相变压器绕组高压侧的频率响应特性进行测试,测试输入信号幅值10V,扫频范围0~1MHz。将三绕组测试结果输入电脑画得三绕组频率特性测试结果如图9所示。从测试结果可以看出,该台变压器三绕组的频率响应的一至性较好,也说明了测试仪能很好的完成变压器绕组频率特性测试功能。

图9 变压器绕组测试结果

6 结论

本文设计了变压器绕组变形测试仪,主要介绍了该仪器的硬件设计和软件设计,设计该仪器能够完成对变压器绕组的幅频特性和相频特性进行测试,也可根据不同的测试要求,对变压器绕组进行分频段测试和整频断测试。在实验室对变压器绕组的频率特性进行测试后,进一步证明了该仪器在变压器绕组测试中的实用性和可靠性。

[1] 张琛. 变压器绕组变形测试方法及应用[J]. 变压器,2007, 44(2): 35-37.

[2] 诸兵, 曾雪梅, 黄晓艳. 变压器绕组变形监测的研究现状综述[J]. 四川电力技术, 2009, 32(3): 48-53.

[3] 辜超. TWD-Ⅱ型变压器绕组变形测试仪的研制及应用[J]. 山东电力技术, 2002(5): 8-11.

[4] 章叔昌. 基于LabVIEW的变压器绕组变形测试仪[J].江西电力, 2009, 33(5): 38-41.

[5] 于云飞, 胡学龙, 方宇. 基于FRA的变压器绕组变形的分频段研究[J]. 扬州大学学报(自然科学版),2009, 12(3): 34-38.

[6] 黄智伟. FPGA系统设计与实践[M]. 北京: 电子工业出版社, 2005.

[7] COMS 300 MSPS Quadrature Complete DDS-AD9854 Datasheet. Analog Devices Inc, 2004.

[8] 董军刚, 蔡振江, 王福顺, 等. 基于DDS技术的智能信号发生器的设计[J]. 微计算机信息, 2007,23(4-2): 298-299.

[9] 王小利. 宽带直流放大器系统设计[J]. 电子器件,2010, 33(3): 392-394.

[10] 陈仁伟, 朱长青, 岳夕彪. 高准确度有效值转换电路的设计与实现[J]. 电子测量技术, 2010, 33(6):20-23.

[11] 刘延华, 张承学, 代芬. 12位高速ADC存储电路设计与实现[J]. 单片机与嵌入式系统应用, 2003(5):33-35.