总剂量辐射环境中的静态随机存储器功能失效模式研究

郑齐文余学峰崔江维 郭 旗 任迪远 丛忠超3)

1)(中国科学院新疆理化技术研究所,乌鲁木齐 830011)

2)(新疆电子信息材料与器件重点实验室,乌鲁木齐 830011)

3)(中国科学院大学,北京 100049)

(2012年12月30日收到;2013年1月30日收到修改稿)

1 引言

静态随机存储器是数字处理、信息处理、自动控制设备中重要组成部件,被广泛应用到航天器和卫星的控制系统中[1].空间辐射环境中的带电粒子(如电子、质子与带电重粒子)和宇宙射线会对SRAM器件造成辐射损伤,引起诸如数据存取速率、噪声容限、功耗电流等特性参数的剧烈变化,甚至造成数据错误或功能完全失效,严重威胁航天器工作的可靠性和安全性[2].因此,研究SRAM器件的辐射效应具有重要现实意义和必要性.

自上世纪70年代起,国内外针对SRAM的总剂量辐射效应开展了大量研究[3-9].目前关于SRAM总剂量辐射损伤机理的基本认识是:辐射在栅氧化物和隔离氧化物中引入的氧化物陷阱电荷及界面陷阱电荷引起晶体管阈值电压漂移及漏电,积累到一定程度造成SRAM功能失效,在参数测试上表现为随着总剂量辐射静态功耗电流增加,累积到一定剂量器件功能失效[3].

目前关于SRAM总剂量功能失效的研究大部分集中在物理层面,少有在电路级别关于失效模式的探讨,且对不同工艺及电路结构的器件采用不同的实验方法得出了不同的结论[10-12].

实际上,由于SRAM器件内部电路结构复杂,宏观电参数的测试结果很难体现器件内部的损伤信息,使得目前对总剂量辐照引起的SRAM功能失效模式的认识依然不是十分清晰.首先SRAM功能失效模式可为存储单元固定错误(Stuck-at fault),存储单元转变错误(Transition fault),多个存储单元的耦合错误(Coupling fault),以及译码器错误(Address fault)等[13].目前在SRAM的总剂量辐射效应测试中,多数实验通过遍历地址写入读取固定数据的功能测试方法来判断SRAM功能是否正常[4-9],但写入读取固定数据的功能测试只能覆盖存储单元固定错误以及部分的转变和耦合错误且需要假设译码器正常工作,如果SRAM的功能失效模式不在其覆盖范围内,则该器件的抗总剂量辐照水平会被高估.例如总剂量辐照引起SRAM译码器错误,由于写入读取固定数据的功能测试对所有地址写入的数据相同,因此即便是辐照引起了译码器失效,器件仍可通过该功能测试.其次在相同的功能失效模式下,SRAM功能失效可以是存储单元失效和外围电路失效,外围电路失效又可分为译码器失效、写驱动电路失效、灵敏放大器失效、数据IO失效等[13].研究确定SRAM的总剂量辐照功能失效模块,对SRAM器件的抗总剂量辐射加固及评估具有一定的指导意义.如果可以确定SRAM的失效模块,我们可以只针对该模块进行工艺或设计加固来提高SRAM器件的抗总剂量辐照水平,进而减小整体加固所需要的成本;在辐射损伤评估中,则可有针对性地加强相关性能的检测,提高评估精度.

本文对SRAM器件总剂量辐射引起的功能失效进行了六种不同测试图形下的测试.利用不同测试图形覆盖的出错模式不同,通过对比一定累积剂量下同一器件不同测试图形测试结果的差异,以及对失效存储单元单独进行测试,研究了总剂量辐照引起的静态随机存储器(SRAM)功能失效模式.

2 辐照实验及测试方法

本次实验SRAM参数的测试在Verigy 93000上进行,辐照前后对SRAM进行了六种不同测试图形的功能测试.如表1所示,复杂的测试图形覆盖较多的失效模式,简单的测试图形覆盖较少的失效模式[13].其中固定数据(Solid)测试图形即为遍历地址写入读取固定数据的功能测试.在对SRAM进行功能测试的同时也对静态功耗电流,读延迟时间等直流和交流参数进行了测试.

表1 实验应用测试图形以及其覆盖的静态随机存储器出错模式

实验器件采用IDT公司0.5µm互补金属氧化物半导体(CMOS)工艺的16 kbit SRAM,器件型号为IDT6116SA.辐照实验在中国科学院新疆理化技术研究所60Co-γ射线源上进行,剂量率为0.51 Gy(Si)/s.选取3片同一批次的器件,分别编号为A,B,C,器件A辐照到总剂量150 Gy,器件B辐照到总剂量200 Gy,器件C辐照到总剂量300 Gy.器件在辐照期间,除了Vss管脚接地外,其他所有管脚接5 V高电平,使得器件处于静态状态.

3 实验结果及讨论

3.1 实验结果

如表2所示,器件A在辐照到总剂量150 Gy后,进行不同测试图形的功能测试,SRAM可以通过 Solid,Checkerboard,March-6N和Galpat的功能测试,但无法通过Galrow,Galcol的功能测试.器件在进行Galrow和Galcol测试时,地址(96,11,0)的存储单元发生0到1的翻转(我们用(x,y,d)表示存储单元的地址,x为地址线A0—A6的10进制表示,y为地址线A7—A10的10进制表示,d代表一个字(word)的第d个位(bit)).器件B和C分别辐照到总剂量200 Gy和300 Gy后,无法通过所有测试图形的功能测试.

3.2 结果讨论

3.2.1 数据保存错误

在本次试验应用的六种测试图形中,Galpat覆盖最多的失效模式且包含其他五种测试图形覆盖的失效模式.器件A在150 Gy处可以通过Galpat的测试,则说明该器件未出现其覆盖的失效模式,但器件A无法通过Galrow以及Galcol的测试,表明该器件表现出了新的失效模式,且该失效模式不在表1所列范围内.器件A地址为(96,11,0)的存储单元在Galrow和Galcol的测试中发生0到1的翻转,而在其他测试图形中并未翻转,说明该存储单元的翻转需要一定的条件.我们对该存储单元单独进行了写读操作,该存储单元在写操作之后直接读取数据始终正确,但写操作之后使器件置于静态一段时间,当这段时间大于0.15 ms时,读取数据该存储单元发生0到1的翻转,上述实验现象表明器件的功能失效模式为数据保存错误(Data retention fault),数据保存错误是指存储单元只能正确存储数据一定时间,一定时间后存储数据向相反方向翻转[10].对失效存储单元写操作之后直接读取数据功能正确表明器件的写读功能模块并未失效,且器件A在150 Gy只有一个存储单元发生翻转,外围电路失效一般会使得大量存储单元发生翻转,根据以上分析我们认为器件功能失效初期的失效模块为存储单元.

表2 器件A,B,C不同测试图形功能测试结果

IDT6116SA的存储单元结构为四晶体管多晶硅电阻负载(4T-2R)结构,如图1所示.4T-2R结构的存储单元可以最大限度上节省硅片上的面积,商用器件大多会选择这种存储单元结构.同六晶体管结构(6T)存储单元一样,4T-2R结构存储单元通过左右两侧的正反馈来稳定存储数据,只是多晶硅电阻取代p型金属氧化物半导体晶体管(PMOSFET)成为上拉负载.为了限制存储单元上的漏电流,多晶硅电阻的阻值一般较大,这就造成其上拉驱动能力远小于PMOSFET.当存储数据0时,晶体管Q3和Q4处于关闭状态,Q1处于开启状态,存储节点A存储低电平,Q2处于关闭状态,存储节点B存储高电平.

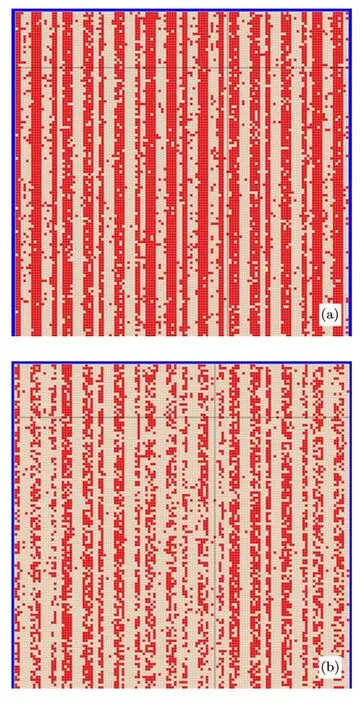

IDT6116SA是0.5µmCMOS工艺的器件,栅氧化物较厚,总剂量辐照在栅氧产生的氧化物陷阱电荷会引起晶体管阈值电压负向漂移[2].处于关闭状态n型金属氧化物半导体晶体管(NMOSFET)的驱动能力与阈值电压直接相关,阈值电压越小关态漏电流越大,进而驱动能力越强.总剂量辐照会使得晶体管Q1和Q2的驱动能力增强,对于辐照期间存储数据为1的情况,处于开启状态的Q2阈值电压负向漂移大于处于关闭状态的Q1[2],即辐照后Q2的驱动能力要大于Q1.当总剂量辐照使得Q2的驱动能力大于RL时,对该存储单元写入数据0后,Q2使存储节点B的分压小于1/2Vdd,晶体管Q1关闭,Q1关闭促使节点A电压上升,进一步提高Q2的驱动能力,形成正反馈,最终导致存储单元翻转.如果节点B的分压大于1/2 Vdd,则不足以关闭晶体管Q1引起正反馈,存储单元也不会发生数据的翻转,也就说晶体管Q2的阈值电压负向漂移到一定的值,才会发生存储单元数据翻转[14,15].图2(a)为器件C辐照前上电直接读取00h的位图(bitmap),浅色的点代表存储数据0的存储单元,深色的点代表存储数据1的存储单元,由于辐照期间未对器件写入数据,上电直接读取的数据即为辐照本底数据.图2(b)为辐照300 Gy后,对器件进行写读数据00h的功能测试bitmap,结果显示辐照期间处于1状态的存储单元多数发生0到1的翻转.

图1 四晶体管多晶硅电阻负载的静态随机存储器存储单元结构图

对器件A存储单元(96,11,0)进行写读操作的实验结果表明,存储单元向相反的方向翻转前可以保持正确存储数据一段时间.图3为存储节点B一侧的等效电路图,如图3所示,把晶体管Q2等效为电阻RQ2,该阻值代表晶体管Q2的驱动能力,与其阈值电压直接相关,电容C为存储节点B的寄生电容,该电容存储的电荷代表存储节点B存储的数据.对存储单元节点B一侧建立基尔霍夫方程为

图2 (a)器件C辐照前上电直接读取00h;(b)器件C辐照300 Gy后,写读00h功能的位图测试的位图

其中UC(t)为寄生电容C两端的电压,把各元件的电阻电容特性应用到上式,化简得微分方程

对存储单元进行写0操作时,字线WL处于高电平使得存取晶体管处于导通状态,位线BLB处于低状态,BL处于高状态.通过存取晶体管Q4,位线BL对节点寄生电容充电,使其维持在高电平状态Vdd,写操作结束后字线WL处于低电平使得存取晶体管断开,此时寄生电容的电压为Vdd,即微分方程(2)的初始条件为

根据初始条件解微分方程(2)得

图3 存储节点B一侧的等效电路图

在我们进行的所有测试图形的功能测试中,都没有覆盖数据保存错误,所以器件A在150 Gy处可以通过覆盖失效模式最多的Galpat测试图形.由于器件A无法通过写读操作间隔时间较长的Galrow和Galcol测试图形,我们测试到了该器件的数据保存错误.在更小的剂量下,存储单元的数据保存时间可能大于Galrow和Galcol的写读操作间隔,这时器件便可以通过所有测试图形的功能测试,判定器件功能正常,进而会高估器件的抗总剂量辐照水平.由于工业标准的测试图形没有覆盖数据保存错误,为了准确评估SRAM器件抗总剂量辐照水平,我们需要设计测试图形去覆盖该失效模式,例如可以通过在测试图形March-6N写操作结束后置器件于静态一定时间再进行读操作来检测.

3.2.2 数据保存时间的离散性

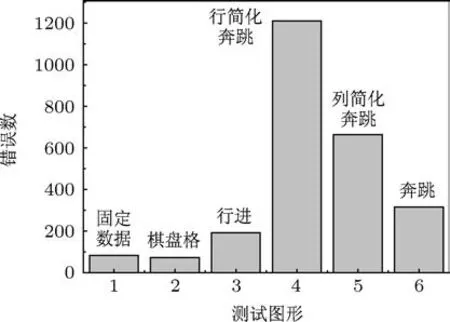

图4为器件B在200 Gy处不同测试图形的出错存储单元个数,如图4所示器件B的出错存储单元数目在不同测试图形测试中有较大的区别.通过对不同测试图形读写操作的分析,我们发现存储单元的出错数与对存储单元写操作和读操作之间的时间间隔直接相关,测试图形写读操作时间间隔越长,出错存储单元越多.对于出错存储单元数最大的Galrow测试图形,大部分存储单元有最大的写读操作的间隔时间.虽然Galpat是测试时间最长且最为复杂的测试图形,但写读操作间隔相对于Galrow和Galcol相对较小,所以出错数远小于以上两个测试图形.写读操作间隔时间最少且相等的测试图形Solid和Checkerboard出错数相当且在所有测试图形中最少.以上实验结果表明存储单元的数据保存时间具有离散性即不同存储单元的数据保存时间不同,测试图形写读操作时间间隔越长其覆盖的存储单元数据保存时间范围越大,进而出错存储单元越多.

图4 器件B在200 Gy处不同测试图形的出错存储单元个数

图5为晶体管Q2不同阈值电压下存储节点电压与时间的关系图,如图5所示,根据方程(4)得到晶体管Q2在不同阈值电压下寄生电容电压随时间的变化关系,其中Vt1>Vt2>Vt3,Vt2为寄生电容稳定电压为Vdd/2的晶体管阈值电压.晶体管阈值电压为Vt1时,寄生电容稳定电压大于Vdd/2,存储单元不会发生数据保存错误.当晶体管阈值电压为Vt3时,存储单元数据保存时间(t1-t0)<(t2-t0).以上结果表明存储单元中晶体管阈值电压漂移到一定值才会发生数据保存错误,且阈值电压越小,数据保存时间越短.

根据以上分析,我们认为由于半导体工艺造成的不同晶体管阈值电压的离散性可能是存储单元数据保存时间的离散性的直接原因.

图5 晶体管Q2不同阈值电压下存储节点电压与时间的示意图

4 结论

本文利用六种不同测试图形的功能测试,研究了SRAM器件的总剂量辐射功能失效.对比SRAM功能失效时不同测试图形的测试结果,以及对失效存储单元单独进行测试,分析认为器件的功能失效模式为数据保存错误且数据保存时间具有离散性,引起数据保存错误的SRAM功能模块为存储单元.4T-2R结构的存储单元,多晶硅负载电阻驱动能力较小,当总剂量辐照使得存储单元中NMOSFET驱动能力大于多晶硅负载电阻时,存储单元发生数据保存错误.由于半导体工艺的偏差,使得同一器件上的不同晶体管阈值电压具有离散性,直接导致存储单元的数据保存时间具有离散性.4T-2R结构的存储单元对总剂量辐照非常敏感,在抗辐照SRAM的设计中不适合应用.数据保存错误要求我们进行覆盖更多失效模式的功能测试,才能准确判断辐照后SRAM器件功能是否正常.

[1]Lu H,Yin F,GaoJ 2005 Microprocessors 5 6(in Chinese)[陆虹,尹放,高杰2005微机处理5 6]

[2]Oldham T R,McLean F B 2003 IEEE Trans.Nucl.Sci.50 483

[3]Francis P,Flandre D,Colinge J P 1995 IEEE Trans.Nucl.Sci.42 83

[4]Aivars J L,Steven R M,Oldham T R,Robertson D N 1996 IEEE Trans.Nucl.Sci.43 3103

[5]Robin H P,JoelJ C,Robert L R,Keith W G 1986 IEEE Trans.Nucl.Sci.NS-33 1535

[6]LiM,Yu X F,Xue Y G,Lu J,CuiJ W,GaoB 2012 Acta Phys.Sin.61 106103(in Chinese)[李明,余学峰,薛耀国,卢健,崔江维,高博2012物理学报61 106103]

[7]LiM,Yu X F,Xu F Y,LiM S,GaoB,CuiJ W,Zhou D,XiS B,Wang F 2012 Atomic Energy Science and Technology 46 507(in Chinese)[李明,余学峰,许发月,李茂顺,高博,崔江维,周东,席善斌,王飞2012原子能科学技术46 507]

[8]He C H,Geng B,He B P,YaoY J,LiY H,Peng H L,Lin D S,Zhou H,Chen Y S 2004 Acta Phys.Sin.53 194(in Chinese)[贺朝会,耿斌,何宝平,姚育娟,李永宏,彭宏论,林东生,周辉,陈雨生2004物理学报53 194]

[9]LiM,Yu X F,Lu J,GaoB,CuiJ W,Zhou D,Xu F Y,XiS B,Wang F 2011 Nuclear Techniques 34 452(in Chinese)[李明,余学峰,卢健,高博,崔江维,周东,许发月,席善斌,王飞2011核技术34 452]

[10]Chumakov A I,YanenkoA V 1996 IEEE Trans.Nucl.Sci.43(6)3109

[11]Schwank J R,Dodd P E,Shaneyfelt M R 2004 IEEE Trans.Nucl.Sci.51 3692

[12]Schwank J R,Shaneyfelt M R,Felix J A 2006 IEEE Trans.Nucl.Sci.53 1772

[13]Jha N K,Gupta S Testing of DigitalSystems(New York:Cambridge University Press)

[14]DililloL,Patrick G,Serge P 2005 VLSI Test Symposium,Proceedings.23rd IEEE Palm Springs California May 1—5 183

[15]Oldham T R,McGamty J M,Lelis A J,TerrellJ M 1992 Reliability Physics of VLSI Microelectronic Devices Harry Diamond Laboratories Report HDL-TR-2203

[16]Huff H,Shimura F 1985 Silicon MaterialCriteria for VLSI Electronics Sol.St.Technology 103

[17]Oldham T R,Bennett K W 1993 IEEE Trans.Nucl.Sci.40 1820

[18]ToshihikoH,Hirotada K,ShujiM 1990 IFEE Journalof Solid-Stat Circuits 25 1068