低SSN的机顶盒芯片DDR控制器的设计

梁 骏,张 明

(浙江大学 信息与通信工程研究所,浙江 杭州310027)

责任编辑:许 盈

DDR SDRAM(Double Date Rate Static Random Access Memory,双速率静态随机访问存储器,以下简称DDR)的最高工作频率随着芯片技术进步从第一代的200 Mbit/s传输速率飞速发展到第三代的1 600 Mbit/s[1]。封装寄生电感会给DDR接口带来很大的SSN(同步开关噪声),并限制芯片DDR接口的传输速率。QPF封装的管脚金线电感大约有5~10 nH,BGA封装的寄生电感大约1 nH。当使用QFP封装时,金线电感会引起极大的SSN效应,并导致DDR的波形异常与数据错误[2-3]。这一不利因素限制了机顶盒芯片采用QFP封装降低芯片成本的可行性。

本文分析了DDR接口的SSN效应,并提出了基于数据重发的DDR控制器的设计以减少DDR接口的SSN效应。本文提出的设计以损失较少的DDR接口数据带宽为代价,通过数据比特翻转控制来减少SSN效应。较少的SSN使得低成本的QFP封装能够应用于高速的DDR接口中,有助于提高机顶盒芯片的竞争力,并减少对环境的消耗与污染。

1 SSN效应

DDR接口的SSN效应可以由图1说明。图1表示了一对电源地为2个接口驱动器提供电源地回路。QFP封装主要的寄生效应是电感,如图1中的L。当DDR接口开始向DDR颗粒写数据1时,电流通过L和PMOS管,并输出到PCB传输线,引起外部传输线电平升高。当输出信号翻转为0时电流从外部传输线流入芯片,通过驱动器的NMOS管,然后通过L回到电源的地。在信号翻转过程中,DDR接口的驱动器感受到的电源与地将是一个叠加SSN噪声的非理想电源与地。这个SSN电压噪声引起输出波形的边沿发生恶化,信号延时发生抖动,最终导致系统的工作时序减少,数据异常,系统稳定性降低。

图1 SSN效应

当一对电源地为更多驱动器提供电源地回路时,如果多个驱动器同时输出,每一份电流都要在电源地的寄生电感上产生感应电压dV即SSN。这个SSN又反作用于每个驱动器上。由电感的感应电压计算式可得SSN反比于电流变化时间dt,正比于封装寄生电感值L与变化电流dI。

式中:n是驱动器的个数。

当同时翻转的比特增加时,SSN变得更严重。以16 bit位宽的DDR颗粒的设计为例,当16 bit数据同时从0翻转到1时,此时的SSN将在电源上形成最大的电压变形。如果要减少SSN,可以减小L,减小dI,增加dt,或者减少同时翻转的驱动器个数n等[4-6]。

图2是1个电源、1个地为1~8个数据IO提供电源地回路时的SSN的SPICE仿真结果。由图2可知当1~8 bit共同翻转时,SSN在电源上产生的电压波动的峰峰值分别 是160 mV,290 mV,380 mV,460 mV,530 mV,600 mV,660 mV,730 mV。8 bit翻转时的噪声幅度是1 bit翻转时的4.6倍,是4 bit翻转时的1.6倍。如果减少同时翻转比特的数量就可以显著降低SSN。

图2 SSN仿真波形(截图)

2 DDR接口与重发流程

一个16 bit位宽的2 Gbit存储容量的DDR3颗粒的功能引脚的定义如表1所示。

DDR颗粒的低8 bit和高8 bit各有1 bit的DM信号作为写入使能。LDM为低8 bit数据的DM信号,HDM为高8 bit数据的DM信号。当DM为高时对应传输的数据不存储进DDR颗粒。当[HDM,LDM]=00,01,10,11时分别表示不写入数据,写入低8 bit数据,写入高8 bit数据,写入16 bit数据。当DM为高时,由于对应的数据不写入DDR颗粒,所以此时对应的数据可以是任意值。

表1 DDR接口

利用DM信号,可以设计基于重传的DDR控制器。当一次写传输操作中如果因为同时翻转比特较多导致SSN严重时,可将1次写传输分成2次写传输。通过数据复制的方法减少同时翻转的比特数目。

上文提出的DDR控制器的重传流程如图3所示。在系统初始化阶段设定最大翻转比特N。当系统开始运行时对DDR的读写操作进行判断。如果是读操作,则正常进行读操作;如果是写操作,则再对写数据中的最大翻转比特M进行计算。

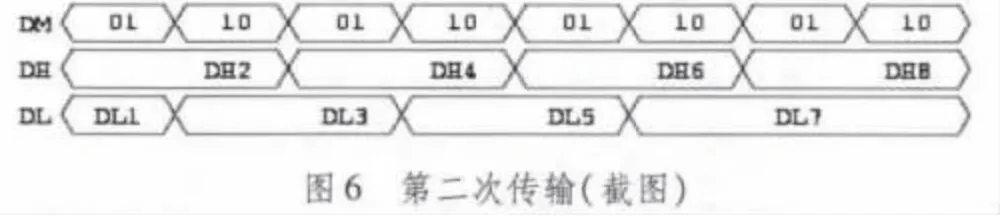

如果最大翻转比特M没有超过设定最大翻转比特N,则按照图4正常写传输。如果最大翻转比特M超过设定最大翻转比特N,则将一次burst 8变换成2次burst 8写操作。同时按照图5、图6方式控制DM信号与数据比特。

经过变换后每一次数据跳变都有8 bit数据不变化,最大同时跳变比特数降低到8,SSN也将相应降低。

3 效率分析

上文提出的方法可以减少SSN效应。但是由于数据重传带来DDR带宽的降低。当DDR读操作和写操作的比例是1∶1时,极端情况下如果每次写传输都重发一次,则DDR带宽降低1/3。由于机顶盒芯片在DDR中存储的数据是电视图像。图像数据通常具有极高相关性,高翻转的数据所占比例不高,需要重发的数据量并不大。

以lena图为例,统计当以burst8的方式存储的亮度信息时DDR接口上数据的同时翻转比特数。1次burst8传输将传送16 byte数据。以每一个像素8 bit计算,一次burst8传输将传送16个相邻比特的亮度数据。以相邻2个像素的亮度数据按照比特组合成一个16 bit的传输数据。每8个传输数据内统计相邻数据的数据跳变的最大比特数。最后统计最大比特数的概率分布,统计结果见表2。

表2 最大翻转比特统计分布

统计结果表明burst8写操作中最大翻转比特11出现的概率最大。最大翻转比特大于12时出现的概率快速减小。当DDR读操作和写操作的比例是1∶1时,当设定最大翻转比特为15时,只有0.60%的数据需要重传,DDR带宽降低0.30%;当设定最大翻转比特为14时,由于数据重传带来DDR带宽降低1.46%;当设定最大翻转比特为12时,由于数据重传带来DDR带宽降低8.00%。结果表明可以用较少的带宽代价减少SSN的负面影响。

4 小结

DDR的工作频率受到多种因素影响。其中DDR接口的SSN效应是重要的因素之一。低成本的QFP封装在消费类电子芯片中得到了广泛应用。但是高寄生电感效应限制了采用QFP封装时的DDR接口速度。

本文利用DDR3标准中的DM管脚功能,提出对高翻转率的数据进行重发,将比特翻转率减少,从而得到较少SSN的DDR控制器的设计方法。分析结果表明这个方法能在不改变封装电感参数的前提下,以较少的DDR接口带宽为代价有效减少SSN,提高DDR接口的工作频率与系统的鲁棒性。这个方法特别适合应用于低成本的QFP封装的机顶盒芯片设计。

[1]DDR3 SDRAM standard JESD79-3F[EB/OL].[2012-10-20].http://www.jedec.org/sites/default/files/docs/JESD79-3F.pdf.

[2]SHYH J J,SHUHUA K,JUI T C,et al.Low switching noise and load adaptive output buffer design techniques[J].IEEE SCCS,2001,36(8):1239-1249.

[3]KOH W.Memory device packaging-from leadframe packages to wafer level packages[C]//Proc.6th IEEE CPMT Conf.[S.l.]:IEEE Press,2004:21-24.

[4]TAKAHASHI N,SUMINAGA S,KAGAWA K,et al.Design practices and issues in controlling simultaneous switching noise[C]//Proc.Electron.Packag.Technol.Conf.[S.l.]:IEEE Press,2005:6-10.

[5]STAN M R,BURLESON W P.Bus-invert coding for low-power I/O[J].IEEE Trans.Very Large Scale Integr.Syst.,1995,3(1):49-58.

[6]HSU J,YANG S,GUO W,et al.High-speed parallel interface implementation with low-cost system solution by using signal integrity factorial design[C]//Proc.Electronic Components and Technology Conference(ECTC).[S.l.]:IEEE Press,2010:1900-1905.