嵌入式数字存储示波器设计

程志强, 汪思静,杨 杰,魏 磊

(1.武汉科技大学 信息科学与工程学院,湖北 武汉 430081;2.武汉科技大学 汽车与交通工程学院,湖北 武汉 430081)

嵌入式数字存储示波器是近年发展起来的一种数据及波形实时显示的智能终端设备,目前通用的数字示波器多采用单片机、DSP、FPGA或DSP+FPGA结构。嵌入式数字示波器可看成是一种低成本、低功耗、可作为一个模块使用的嵌入式智能终端。普通单片机在数据处理方面能力有限,不能满足数字示波器要求的高速数据传输的要求,虽然DSP数据处理能力强大,运行速度较高,FPGA灵活性强,可以充分地进行设计开发和验证,便于系统升级[1-3]。但是,DSP和FPGA一般价格较高,不适合在低成本的嵌入式数字示波器开发中使用。

ARM是面向低价位市场设计的一种RISC微处理器,其优点是性价比高,适合嵌入式数字示波器的需求。选用的是基于Cortex-M3内核的ARM32位微处理器STM32F103VCT6作为主控芯片。该芯片内部集成了16通道的12位高精度A/D转换器,转换时间仅为1μs,还有很多通信接口以及CAN总线,而且它具有一系列的睡眠、停机、待机等省电模式,功耗低,与传统的单片机相比,其在性能上和处理能力上市遥遥领先的,满足本款示波器的设计要求。

与传统模拟示波器相比,数字存储示波器不仅具有可存储波形和使用方便等优点,而且还具有强大的信号实时处理分析功能,同时,将嵌入式技术融入到示波器的设计中,使其具有功耗低,体积小等优点。在电子测量领域,数字存储示波器正在逐渐取代模拟示波器。但目前高性能的数字储存示波器普遍价格昂贵,因此研究数字存储示波器具有重要价值。鉴于此,提出了一种嵌入式数字存储示波器的设计方案,经测试,性能优良。

1 系统硬件的设计

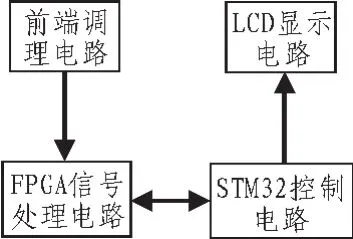

根据系统的功能需求,系统总体框架图如图1所示,主要包括:A/D转换模块,FPGA模块和STM32模块等,FPGA进行数据A/D转换的控制,STM32对整个系统的流程进行控制。工作流程如下:系统初始化完成后,A/D转换器在FPGA的控制下进行数据采样在完成规定长度的采集工作之后,FPGA将数据存入其内部模块FIFO,从而实现对数据的缓存。同时,由STM32在一定的条件下使能DMA通道,将A/D所采集的数据传输至LCD缓冲区中,由LCD对这些数据进行显示。

图1 系统总体框图Fig.1 System block diagram

1.1 前端调理电路

本系统的前端调理电路采用抗混叠滤波电路,我们知道,A/D转换器的采样频率的范围都是一定的。由奈奎斯特定理可知,只有当采样频率高于两倍的输入信号频率时才能对信号可靠地数字化,而如果有一部分输入信号的频率高于采样频率的一半.则这部分信号会变换到较低的带宽内。同时其幅度仍保持不变,这将使人很难区别输入信号是低于采样频率的一半还是高于采样频率的一半。抗混叠滤波器[9-10]的作用就是将高于采样频率的一半的信号滤除。以保证A/D数字化的正确性和可靠性。

采用CMOS双路运算放大器OPA2345对信号进行放大或衰减,使信号满足AD9288的模拟输入要求,也就是将输入信号的电压调理在-0.5~0.5V范围内,然后再进入模数转换器AD9288将模拟信号转换成数字信号。

1.2 A/D转换电路

系统A/D转换部分采用的是ADI公司的AD9288,这是一款双通道8位的高速低功耗模数转换器,最高采样速率达100MSPS,模拟信号的输入范围为-0.5~+0.5 V。用户只需提供3.3 V电源和一个编码时钟,许多应用不需要外部基准和驱动元件,编码器输出的是TTS/CMOS兼容的8位数字量,它为改进系统,降低成本、提高可靠性和缩短上市时间提供了完整的解决方案。

本设计中,采用双路设计,A、B通道分时刻进行数据采集,将采集到的数据送入FPGA进行缓存。

1.3 FPGA部分电路设计

FPGA部分主要功能包括数据缓存和主控制器(STM32)通信,由于AD9288为8位数据采样精度,因此,FPGA使用8位的数据线和AD9288进行数据交互,在和STM32通信方面,采用FSMC(灵活的静态存储器控制器)方式,此时,FPGA相当于STM32的一块外部存储器,FSMC通信方式的优势有:

1)支持多种静态存储器类型。STM32通过FSMC町以与SRAM、ROM、PSRAM、NOR Flash和 NANDFlash存储器的引脚直接相连。

2)支持丰富的存储操作方法。FSMC不仅支持多种数据宽度的异步读/写操作,而且支持对NOR/PSRAM/NAND存储器的同步突发访问方式。

3)支持同时扩展多种存储器。FSMC的映射地址空间中,不同的BANK是独立的,可用于扩展不同类型的存储器。当系统中扩展和使用多个外部存储器时,FSMC会通过总线悬空延迟时间参数的设置,防止各存储器对总线的访问冲突。

4)支持更为广泛的存储器型号。通过对FSMC的时间参数设置,扩大了系统中可用存储器的速度范围,为用户提供了灵活的存储芯片选择空间。

5)支持代码从FSMC扩展的外部存储器中直接运行,而不需要首先调入内部SRAM。

内部框图如图2所示。

2 软件部分设计

2.1 数据采集部分软件设计

图2 FPGA与各模块通信及内部框图Fig.2 FPGA communicate with modules and internal block diagram

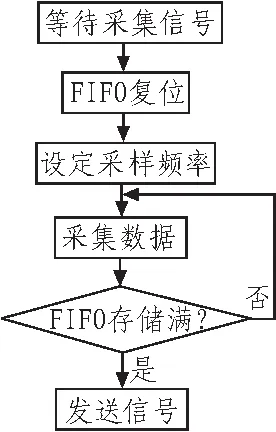

数据采集部分由FPGA进行,因此,数据采集部分软件设计即为FPGA电路设计,在FPGA电路中,主要包含了如下几个模块,FIFO模块、地址控制模块、双端口RAM模块、IO模块和信号同步和控制模块。

程序的流程图如图3所示。

图3 数据采集软件流程图Fig.3 Software flow chart of data acquisition

2.2 控制部分软件设计

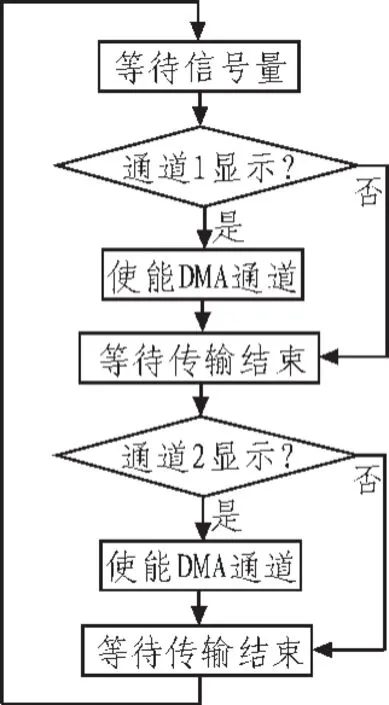

控制部分软件指的是STM32部分的软件设计,主要包括系统初始化、时钟,为了达到数据的高速传输,使能DMA功能,让从FPGA传回的数据通过FSMC方式直接传入LCD中,此外,FPGA和STM32同样采用FSMC通信方式,FPGA相当于STM32的一块外部存储器,与LCD共用FSMC数据总线,这样不仅节约了系统资源,也提高了数据的传输速度。程序流程图如图4所示。

图4 控制软件流程图Fig.4 Flow chart of control software

3 实验结果与分析

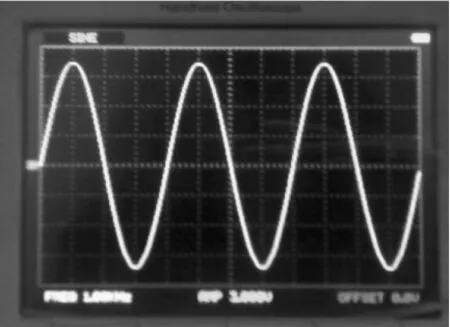

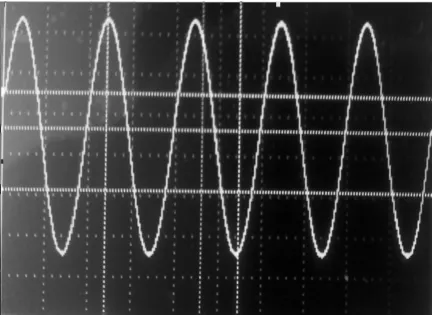

在完成了系统的硬件和软件设计后,需要进行综合调试和测试,通过调试,不断优化程序代码,对程序中的问题进行及时更正和修改,使系统的性能得到提高,工作更加稳定,进行测试时,使用Hantek DSO 8060作为信号源,频率FREQ1.00 kHz,幅值 AMP3.0 V,峰峰值 VPP6.0 V,显示结果如图5所示,使用该嵌入式示波器通道A对信号进行显示,如图 6所示,频率 FREQ1.021 kHz,峰峰值 VPP5.84 V,通过对比分析,嵌入式示波器和Hantek DSO 8060的显示虽然存在误差,频率误差率2.1%,峰峰值误差率1.3%,基本满足要求,实验成功。

图5 Hantek DSO 8060显示结果Fig.5 Displaying results on Hantek DSO 8060

图6 嵌入式示波器显示结果Fig.6 Displaying results on embedded oscilloscope

4 结束语

近年来,随着国内电子信息产业和电子技术的不断发展,催生了庞大的数字示波器市场需求,数字示波器在信号处理和显示方面有着独特的优势,因此,数字示波器具有广泛的研究前景。本系统采用STM32作为主控制器,充分利用FPGA的可编程逻辑功能,完成相关电路设计,软硬件有机结合实现嵌入式数字存储示波器的设计,系统总体功能完善,稳定性高,使用方便。

[1]Mota H O,Vasoncelos FH.A partial discharge data acquisition system based on programmable digital oscilloscopes[J].IEEE Instrumentation and Measurement Technology Conference,2001(2):994-999.

[2]杨林楠,李红刚,张丽莲,等.基于FPGA的高速多路数据采集系统的设计[J].计算机工程,2007(4):246-248.YANG Lin-nan,LI Hong-gang,ZHANG Li-lian,et al.A high-speed multi-channel data acquisition system design based on FPGA[J].Computer Engineering,2007(4):246-248.

[3]刘尧猛,马永军,丁忠林.基于ARM9和FPGA的嵌入式数字示波器[J].计算机应用与软件,2010(3):84-86.LIU Yao-meng,MA Yong-jun,DING Zhong-lin.The embedded digital oscilloscope design based on ARM9 and FPGA[J].Computer Applications and Software,2010(3):84-86.

[4]王栋,张俊涛.基于SOPC的数字示波器的设计与实现[J].电子器件,2009,32(3):632-636.WANG Dong,ZHANG Jun-tao.Design and implementation of digital oscilloscope based on SOPC[J].Electronic Devices,2009,32(3):632-636.

[5]张雅珍.基于FPGA和ADS830的数字示波器设计 [J].电子测量技术,2009,179(6):69-71.ZHANG Ya-zhen.A design of digital oscilloscope based on FPGA and ADS830[J].Electronic Measurement Technology,2009,179(6):69-71.

[6]张锡纯.电子示波器及其应用[M].北京:机械工业出版社,1997.

[7]刘维清,吴隆穗,卢敏.基于ARM的数字存储示波器设计[J].江西理工大学学报,2010,31(5):11-13.LIU Wei-qing,WU Long-sui,LU Min.A design of digital storage oscilloscope based on ARM[J].Jiangxi University of Technology,2010,31(5):11-13.

[8]丁昊,宋杰,关键.基于TFT彩屏液晶的便携数字存储示波器[J].现代电子技术,2010,33(18):13-15.DINGHao,SONGJie,GUAN Jian.A design of portable digital storage oscilloscope based onTFTcolor LCD[J].Modern Electronic Technology,2010,33(18):13-15.

[9]陶征,熊来红.谐波分析与滤波器优化配置软件在电力系统中的应用[J].陕西电力,2011(11):10-13.TAO Zheng,XIONG Lai-hong.Application of harmonic analysis and optimal configuring of filters software in power system[J].Shaanxi Electric Power,2011(11):10-13.

[10]杨建安,李健,徐志强,等.基于互补滤波器的大型定转速风力发电机组有效风速信号测量方法[J].陕西电力,2011(11):22-25.YANG Jian-an,LI Jian,XU Zhi-qiang,et al.Probe into the measurement method of effective Wind speed signal for fixed-speed wind turbines based on complementary filters[J].Shaanxi Electric Power,2011(11):22-25.