基于AES算法的加密模块设计

弟宇鸣,陈荣桦,左广霞

(第二炮兵工程大学 102室,陕西 西安 710025)

随着信息技术的日新月异,信息的安全性问题日益突出,如何确保存储信息的安全有效越来越成为人们关心的问题。采用加密技术是解决数据存储安全性的首选[1]。当前,密码学理论和技术已取得了长足的发展,新一代加密算法AES算法可以抵挡目前已知的所有攻击手段,它的产生与应用,给数据加密带来了福音。AES算法是一种迭代型分组密码,该算法设计简单,与公钥密码算法不同,没有复杂的乘法运算,易于实现,灵活性强,轮函数良好的并行特性有利于硬件设计与实现[2]。

1 AES算法简介

2001年 11月,NIST宣布将比利时人 Joan Daemen和Vicent Rijinen提交的Rijndael算法作为高级加密标准(AES)。2006年,AES算法已成为对称密钥加密中最流行的算法之一。AES算法是一种迭代型分组密码,其分组长度和密钥长度均可变,各自可以独立指定为128位、192位、256位。轮数Nr依赖于密钥长度。如果密钥长度为128比特,则Nr=10;如果密钥长度为192比特,则Nr=12;如果密钥长度为256比特,则Nr=14。文中主要讨论分组长度和密钥长度为128位的情况[3]。

AES算法可以用软件也可以用硬件实现,实际使用中根据具体的应用环境两种情况都有。软件实现是靠CPU的运算来实现算法,易受使用条件限制,加密速度慢,易受到破坏,影响数据传输质量。硬件实现是用专用芯片实现密码算法,通过芯片对数据进行加密。专用加密芯片是实现信息安全与保密的核心模块,具有保密性高,加密效率高,易于嵌入,总体成本低等优点,因此在复杂系统和大数据量加密系统中,一般都使用硬件来实现AES加密[4]。

2 AES算法原理

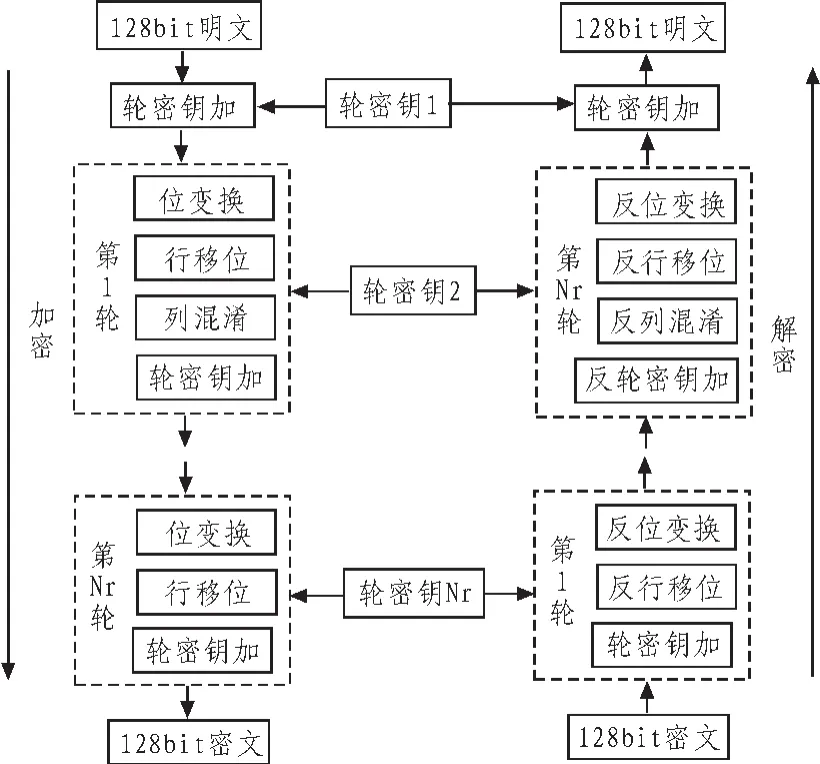

AES的加密流程为,首先将明文映射到状态矩阵(State),进行初始密钥加运算;然后进行Nr次轮运算,各轮都 由 字 节 替 换 (ByteSub)、 行 移 位 (RowShift)、 列 混 淆(MixColumn)、轮密钥加(Addroundkey)4 个置换来实现,但第Nr轮不做列混淆;最后将状态矩阵映射为密文[5]。解密过程与加密过程类似。加密解密流程图如图1所示。

图1 AES加密解密流程图Fig.1 Flow chart of encryption and decryption

2.1 位替换(ByteSub)

位替换是对状态阵列的字节到字节的变换,它使用字节替换表(S盒)作用于状态矩阵的每个字节。字节替换有正向字节替换和逆向字节替换,正向字节替换是一个简单的查表操作。AES定义的S盒是由16×16个字节组成的矩阵,包含了8位值所能表达的256种可能的变换。State中每个字节按照如下的方式映射为一个新的字节:把该字节的高4位作为行值,低4位作为列值,取出S盒中对应行列的元素作为输出。图2描述ByteSub变换结果。

AES的S盒被设计成能防止已有的各种密码分析攻击,Rijndael开发者特别寻求输入位和输出位之间几乎没有相关性的设计,并且输出值不能通过利用一个简单的数学函数变换输入值所得到。当然,S盒必须是可逆的,但S盒不是自逆的。

图2 位替换示意图Fig.2 Schematic diagram of ByteSub

2.2 行移位(ShiftRow)

行移位是对状态阵列的行到行的变换,也就是将某个字节从一列移到另一列中,它的线性距离是4字节的倍数。在这里要注意到,行移位变换确保了某列的4字节被扩展到了4个不同的列。正向行移位变换,即State的第一行保持不变,把State的第2行循环左移一个字节,State的第3行循环左移2个字节,State的第4行循环左移3个字节。而逆向行移位变换则是将State中的第一行保持不变,后3行执行与正向行移位相反方向的移位操作。

2.3 列混淆(MixColumn)

列混淆是对状态阵列的列到列的变换,它作用于状态阵列的每一列。正向列混淆变换对每列独立地进行操作,每列中的每个字节被映射为一个新值,此值由该列中的4个字节通过函数变换得到。

2.4 轮密钥加(AddroundKey)

轮密钥加是轮密钥与状态阵列中的对应字节按位异或的变换,轮密钥由密钥扩展得到。在正向轮密钥加变换中,128位的State按位与128位的密钥XOR把这个操作看成是基于State列的操作,即把State的一列中的4个字节与轮密钥的一个字进行异或。逆向轮密钥加变换与正向轮密钥加变换相同,因为异或操作是其本身的逆。也可以说由于AddroundKey只包括一个异或操作,所以InvAddRoundKey与AddroundKey变换一致。

2.5 密钥扩展模块

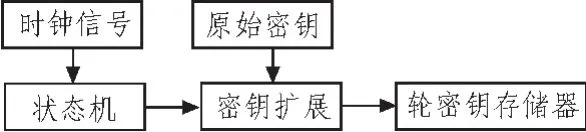

密钥扩展模块负责把输入的初始密钥扩展为每一轮轮变换所需要的轮密钥。文中所设计的模块,预先对输入的密钥进行扩展,一次性完成加密和解密每一轮轮变换所需要的轮密钥。扩展所得的轮密钥存储于轮密钥存储器中,加密和解密过程直接调用轮密钥以节省时间。密钥扩展模块如图3所示。

图3 密钥扩展模块Fig.3 Key extended module

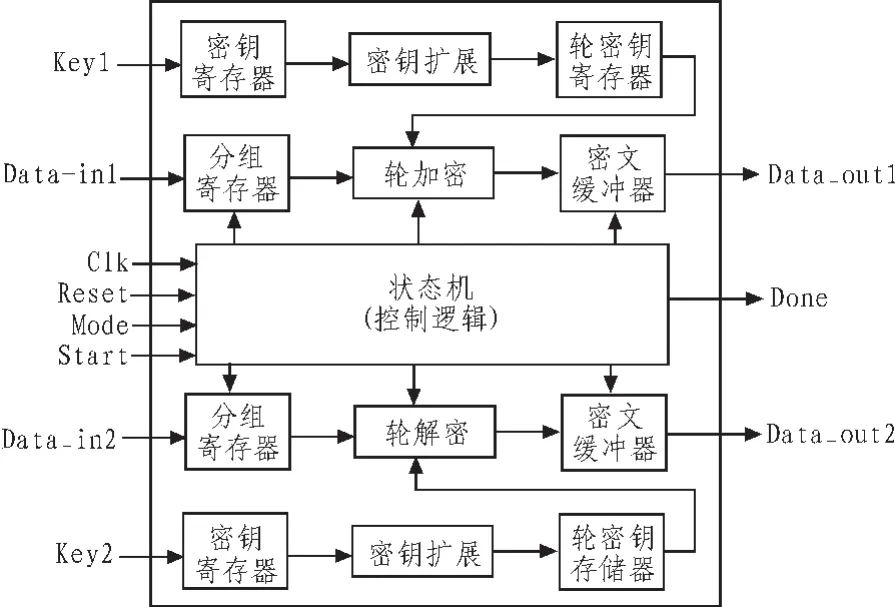

3 硬件模块设计

文中所设计的AES加密模块是在一片FPGA中实现的,系统是以在满足时序要求的条件下,最大程度地减小芯片面积为目标。如果直接在逻辑电路上实现AES算法的各种运算,必然会造成芯片面积过大和资源浪费,影响加解密效果和使用环境。AES加解密模块整体结构如图4所示。

图4 AES加解密模块整体结构Fig.4 Structure diagram of the AESencryption and decryption module

AES加解密模块主要由分组寄存器、轮加密/解密运算单元、明文/密文缓冲器、状态机(控制逻辑)、密钥寄存器、密钥扩展单元、轮密钥存储器及其他单元组成。Clk表示时钟信号,Reset表示复位信号,Start表示算法开始信号,Mode表示加密/解密模式选择,Key1和 Key2分别表示加密/解密密钥输入端口,Start_key表示密钥扩展开始信号,Data_in1和Data_in2分别表示明文/密文数据输入端口,Done表示加/解密完成信号,Data_out1和Data_out2分别表示密文/明文数据输出端口。

在系统进行加密/解密运算前,Start_key信号开始控制密钥扩展模块对初始密钥进行扩展,扩展完成的各轮变换所需要的轮密钥存储于轮密钥存储器中。加密/解密过程需要轮密钥可直接从存储器调用。这样,在大量数据进行运算时,可以节省时间,提高加密解密效率。

4 仿真与结果分析

本设计的代码输入、仿真、综合和实现过程都是在Xilinx公司开发的集成开发件ISE8.2i,Model Tech公司的Modelsim6.le中完成的,选用的是Spartan3系列的Sp3-500E型FPGA芯片。综合工具使用ISE自带的XST,以速度作为约束条件,对本设计进行了综合优化,综合后的得到优化结果如下:

逻辑单元:15 856 LE

存储单元:247 416 bit

最高频率:101.891 MHz

最短时延:9.814 ns

最大吞吐量:2.58 Gbit/s

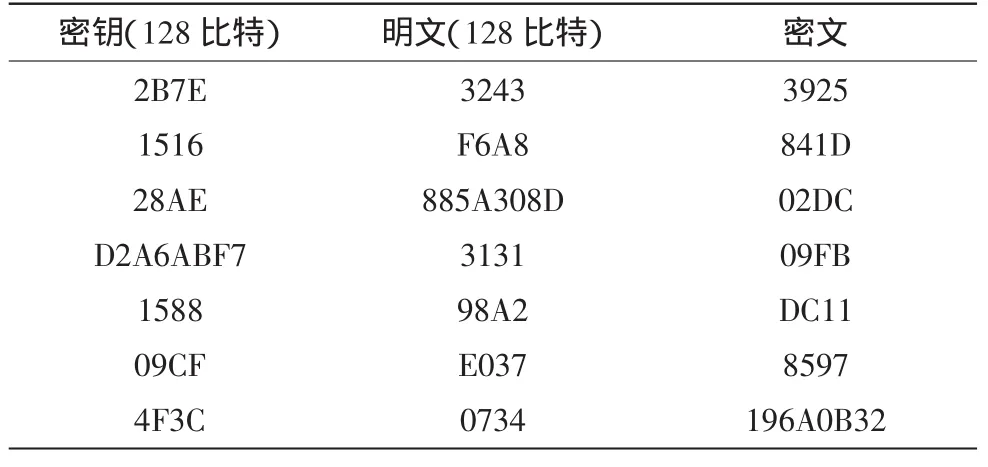

以128比特分组数据为例,在明文分组为128比特,初始密钥长度为128比特,利用高级加密标准提供的测试数据进行仿真。测试数据表1所示。

表1 测试数据Tab.1 Test data

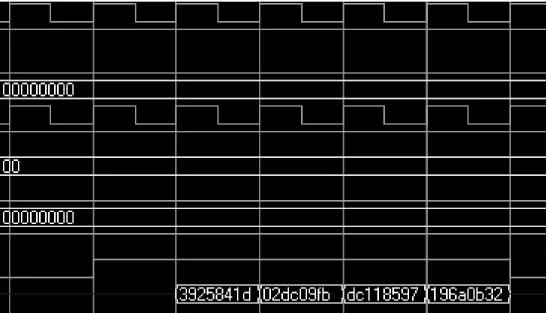

在仿真系统中输入128比特的密钥和明文,仿真结果的密文为:3925 841D 02DC 09FB DC11 8597 196A0B32。仿真结果如图5所示。

图5 初始密钥长度为128比特下的加密结果Fig.5 Encryption result of the key length of 128-bit

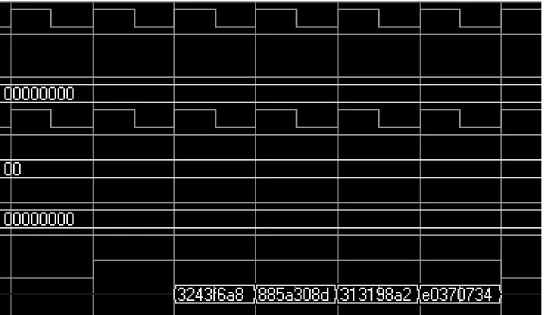

在仿真系统[6-7]中输入128比特的密文和密钥,仿真得到的明文为:3243 F6A8 885A308D 3131 98A2 E037 0734。仿真结果如图6所示。

通过仿真结果可以知道,加密和解密得到的数据与高级加密标准资料中提供的测试数据一致。加密模块能够实现AES算法,AES加密模块在设计上是成功的。

5 结束语

文中首先介绍了AES算法的结构和基本原理,然后提出AES加密模块设计方案。通过用Verilog语言编写实现程序,在Modelsim6.le软件平台上进行编译、仿真,使得以Rijndael数据加密算法的AES高级加密标准得到很好的体现。实验结果表明,文中所设计的AES加密模块能够对初始密钥长度为128比特的明文和密文进行加密和解密,基本达到了预期的设计目标。

图6 初始密钥长度为128比特下的解密结果Fig.6 Decryption result of key length of 128-bit

[1]沈昌祥,张焕国,冯登国.信息安全综述[J].中国科学E辑:信息科学,2007,37(2):129-150.SHEN Chang-xiang,ZHANG Huan-guo,FENG Deng-guo.Summary of information safety[J].Science in China:Series E:Information Sciences,2007,37(2):129-150.

[2]唐金艺.AES算法FPGA实现分析[J].计算机安全,2007(6):14-20.TANGJin-yi.Analysis of AESs Implementation with FPGA[J].Computer Security,2007(6):14-20.

[3]吴鹏,李开成.基于FPGA的Rijndael算法实现的研究[J].铁路计算机应用,2007(120):46-48.WU Peng,LI Kai-cheng.Research on implementation of rijndael algorithm based on FPGA[J].Railway Computer Application,2007(120):46-48.

[4]储奕锋.AES算法的FPGA实现[J].电脑知识与技术,2007(19):191-193.CHU Yi-feng.Implementation of AESalgorithm on FPGA[J].Computer Knowledge and Technology,2007(19):191-193.

[5]高旸,胡向东.AES算法的DSP实现[J].兵工自动化,2006,25(1):38-44.GAO Yang,HU Xiang-dong.Realization of AES based on DSP[J].Ordnance Industry Automation,2006,25(1):38-44.

[6]苏国民,孙旭.基于Matlab的燃油炉温度仿真系统的设计[J].工业仪表与自动化装置,2011(3):89-90.SU Guo-min,SUN Xu.The design of fuel furnace temperature system with the Matlab[J].Industrial Instrumentation &Automation,2011(3):89-90.

[7]周艳平,胡乃平.基于Web的计算机控制技术远程仿真系统开发[J].工业仪表与自动化装置,2010(3):112-115.ZHOU Yan-ping.Development of remote simulation system for computer control technology based on Web[J].Industrial Instrumentation&Automation,2010(3):112-115.