一种基于0.18um工艺低压高精度带隙基准电压源设计

邓森洋, 张 力, 陈 祝

(成都信息工程学院通信工程学院,四川成都610225)

0 引言

传统的带隙基准电路存在很多问题,在温度系数(TC)、功耗、电源抑制比(PSRR)等方面无法达到现今集成电路设计的要求。近几年针对这些问题,很多国内外学者从温度系数、PSRR、功耗、精度等方面进行改进,取得了十分不错的进展[1]。带隙基准源电路的进一步改进和完善,将朝着能够同时满足低功耗、低温度系数、高PSRR、低噪声,以及低电源电压等要求发展[2]。

目前通过一些高阶温度补偿技术,带隙基准电压源的温度系数可以小于1ppm/℃[3-5]。通过加入参考电压源[3]、预校准电路[4]、误差放大器[5]、共源共栅电流镜[6]等电路,可以使电源抑制比达到90dB以上,不过电路都较复杂。有人设计了一种无电阻、工作在亚阈值区的低功耗、小面积的CMOS电压基准源,功耗仅为217nW,但温度系数较大[7]。文中主要分析一阶温度补偿电路,考虑实际电路中电阻的温度系数不为零这一因素,在不影响其他参数性能的条件下进一步降低带隙基准电压温度系数。从而实现结构简单的低压高精度带隙基准电压源。

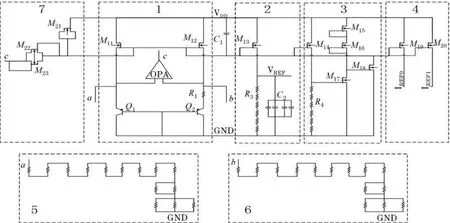

图1 带隙基准整体电路

1 电路设计

设计的带隙基准电路如图1所示。将其划分为7个模块。模块1:带隙基准源的核心电路;模块2:带隙基准源的电压输出模块;通过调节输出端电阻R3的大小,可以改变基准输出电压 VREF的大小;模块3:带隙基准源的自启动电路;模块4:带隙基准源的电流输出模块,利用电流镜的原理,通过调节 M19和 M20管的宽长比,可以改变基准输出电流 IREF0和 IREF1的大小;模块5和模块6:电阻阵列;模块7:电容耦合负反馈PSRR增强电路。

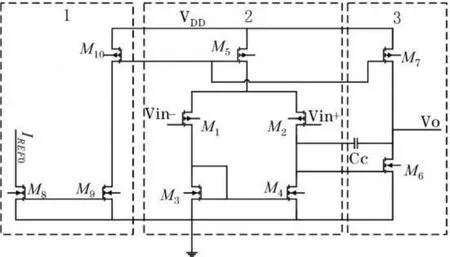

1.1 带隙基准内运放电路

将图2中电路划分为3个模块。模块1:电流镜,作用是引用带隙基准内部的电流基准 IREF0给运放提供偏置,进一步减小运放随温度的影响,降低了电路的工作电流并节省了元件[6];模块2:第一级放大电路,带有源电流镜负载的差分放大器,运放的差分输入对管选择PMOS,可以降低最小工作电源电压,比使用NMOS做输入对管具有更大的输入范围;模块3:第二级放大电路,共源放大电路,提高增益和输出摆幅。Cc为密勒补偿电容,提供频率补偿,保证电路稳定工作[8]。

图2 带隙基准内运放电路

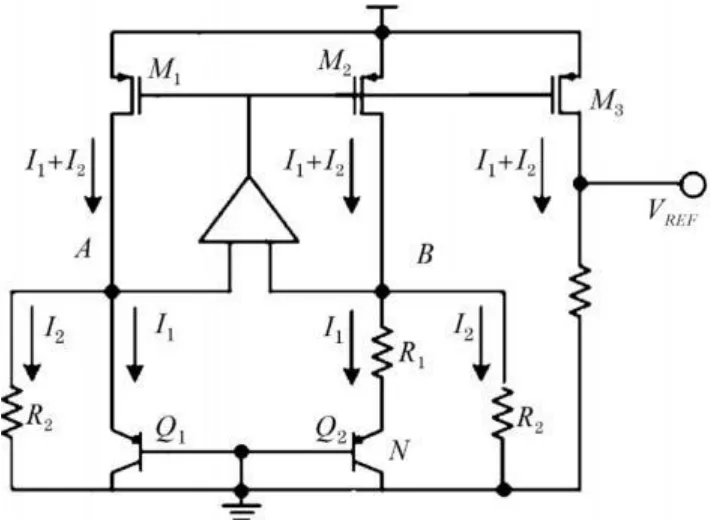

图3 带隙基准核心电路

1.2 带隙基准核心电路

图1模块1中的电路是带隙基准核心电路[1],与图3电路相同,仅电阻R2变换为图1模块5、6。

如图3所示。输出基准大小可以任意调节,从而降低电源电压。当运放处于深度负反馈时,A与B两点电势相等。

流过R1的电流就是与绝对温度成正比(PTAT)电流可知

流过R2的电流与 VBE成正比可知

由基尔霍夫定律得

调节电阻R1、R2大小,使 VREF的温度系数为零,调节电阻R3大小来调整输出基准电压的大小。

1.3 自启动电路

如图1模块3,就是自启动电路。该电路仅在上电瞬间起作用,带隙基准正常工作时停止作用。接通电源瞬间 M15管和 M16管饱和导通,M18管栅压被上拉为高电平而导通,此时 M18管 VDS下降,使 M14管栅压下降,M14管导通,提供了从 VDD经M14和R4到地的电流通路,使带隙基准正常工作。由于R4的存在,有电流流过R4,使M17管栅压上升而导通,M17管 VDS下降,导致 M18管栅压下降而关断,自启动电路停止作用。

1.4 电容耦合负反馈电路

如图1模块7,就是电容耦合负反馈PSRR增强电路[9]。M21管做电容使用,将电源噪声同相耦合到电流镜M11、M12、M13的栅端,使电流镜管的源端和栅端的噪声呈同相变化。这相当于对PMOS电流源管引入了源极负反馈,稳定MOS管的过驱动电压。

1.5 电阻阵列

图1电路中各元件采用TSMC0.18um工艺库中的元件。PMOS选用pmos2V,NMOS选用nmos2V,电阻选用rphpoy,电容选用mimcap。为了电阻的匹配性更好,整个带隙基准电路中的电阻全部用一个阻值的电阻(称为基准电阻)通过串联或并联的方式得到。例如,基准电阻为3K,那么,9K的电阻可以通过3个基准电阻串联得到。若电阻中含有小数,那么也是通过基准电阻的串联和并联的方式实现。文中,电阻 R1作为基准电阻,R2、R3和R4通过R1的不同组合得到。图1模块5和模块6是图3电路中电阻R2的变换结构。同理,电容也如此变换。电容C1和C2可以有效滤出电源中的噪声。

2 数学建模分析

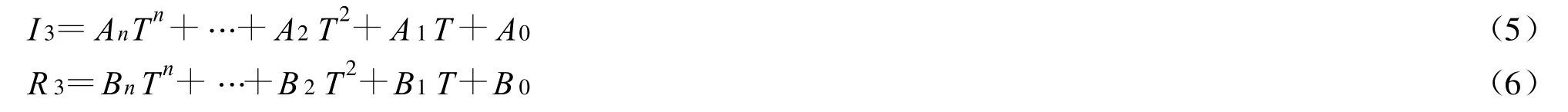

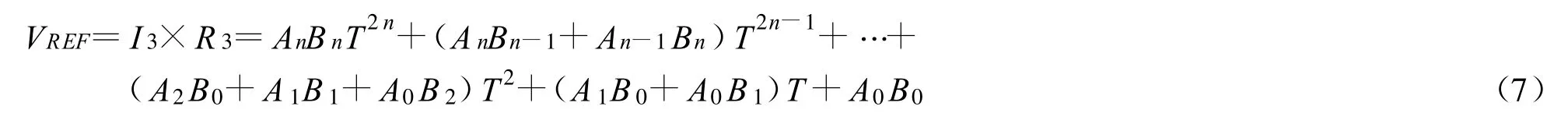

如图3,假设输出端电流(I3=I1+I2)和输出端电阻R3是关于温度 T多项式之和。

由欧姆定律可知,输出基准电压 VREF为

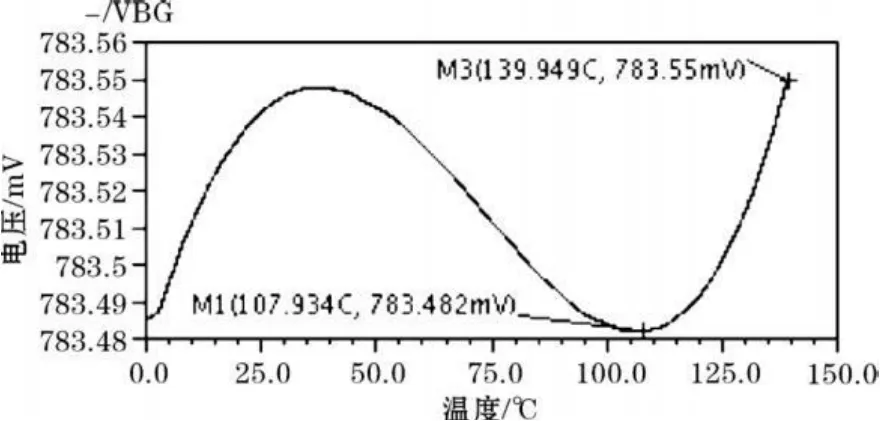

由式(7)可知,VREF是关于温度T的多项式表达式。高阶温度补偿就是要使这些系数为零,即

3 电路调参思路

通过前面分析可知:只要选择合适的输出端电阻和输出端电流随温度的表达式满足式(8),就能够减小在实际电路中电阻温度系数影响带隙基准源输出精度的程度。从而进一步降低带隙基准电压源的温度系数。具体调参思路如下:

(1)改变输出端电阻R3的大小可以改变R=B2T2+B1T+B0中各项系数的大小。

(2)改变R2/R1的大小可以改变电流 I=A2T2+A1T+A0中各项系数的大小。

(3)反复使用上面两个步骤,最终使式(8)成立。

当然,很难实现式(8)的绝对成立。不过满足式(8)的程度越高,基准电压 VREF的温度系数越低。

4 仿真结果及分析

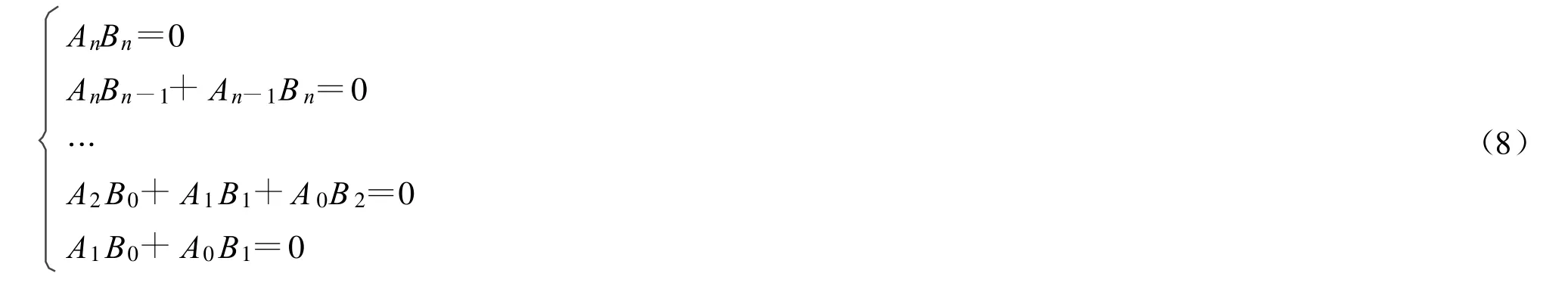

根据以上分析,可以确定电路的器件尺寸,在TSMC 0.18um工艺下,采用典型的Cadence Spectre仿真工具进行仿真,其结果分别如图4~6所示。

图4 VREF随温度变化曲线

图5 电源抑制比曲线

取电源电压为1.8V,在0~140℃对 VREF进行温度扫描,仿真结果如图4。在 0~140℃,VREF从783.482mV到783.55mV,变化了68uV。在0~140℃,温度系数TC=0.62ppm/℃。

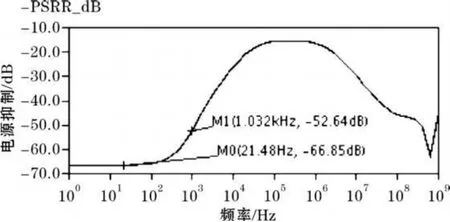

在电源电压中添加AC分量为1V,然后对 VREF进行交流分析,频率为1Hz~1GHz,便可得电源抑制比(PSRR)曲线,如图5所示,在低频时PSRR=-66.9dB,当 f=1KHz时PSRR=-52.6dB。

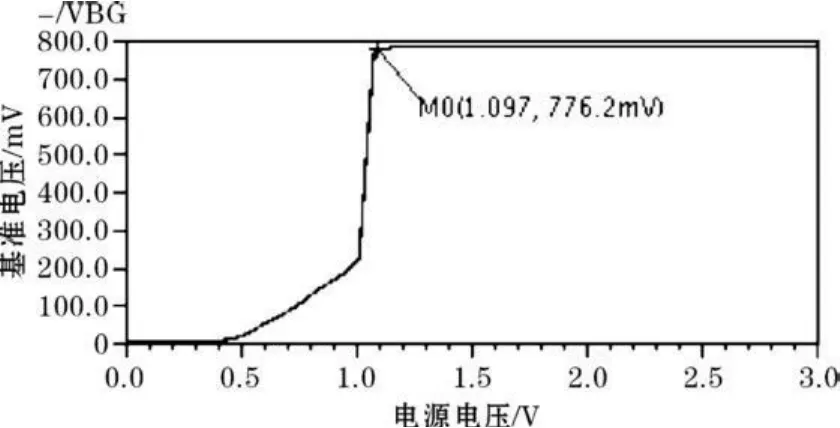

将电源电压 VDD设置为一个变量,然后对 VDD进行直流扫描,得 VREF随 VDD变化的曲线,由图6所示,带隙基准电路在电源电压为1.09V时达到了稳定的输出。因此,该电路的最小工作电源电压约为1.1V。

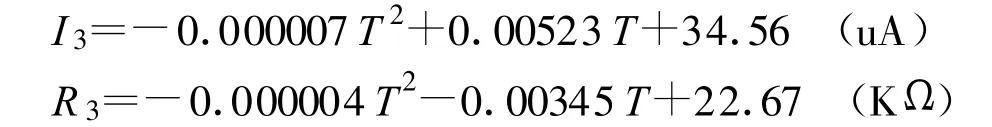

结果分析:当图1电路正常工作时,先通过Cadence软件采集 I3和 R3关于温度T曲线上的点,再通过MATLAB软件拟合出 I3和 R3关于温度 T的表达式,为了求解方便,只考虑温度的二阶(即n=2),再结合式(5)和式(6)验证式(8)。

I3和R3的表达式为:

图6 VREF随 VDD变化曲线

验证式(8)结果如下:

由此可知,I3具有正温度系数,R3具有负温度系数,二者乘积便进一步降低了 VREF的温度系数。

5 结论

通过高阶温度补偿技术,目前国内带隙基准温度系数最低可达0.3ppm/℃[4]。一阶补偿的带隙基准的温度系数一般大于10ppm/℃,高阶补偿后的温度系数也很难小于1ppm/℃且电路都很复杂。设计了一种基于0.18um工艺低压高精度带隙基准电压源,采用电流模结构。在调参过程中考虑了电阻的温度系数,从而进一步降低了带隙基准电压源的温度系数,实现了结构简单的低压高精度带隙基准电压源。

致谢:感谢成都信息工程学院科研基金教改项目(Y20093)对本文的资助

[1] 辛新鹏,李冬,王志华.CMOS带隙基准源研究现状[J].微电子学,2008,38(1):57-63.

[2] 吴文兰,刑立东.带隙基准源的现状及其发展趋势[J].电子设计,2010,26(6-2):186-188.

[3] 胡佳俊,陈后鹏,蔡道林,等.高电源抑制比低温漂带隙基准源设计[J].微电子学,2012,42(1):34-37.

[4] 来新泉,张莎莎,袁冰,等.一种高精度分段曲率补偿带隙基准电压源[J].华中科技大学学报(自然科学版),2010,38(12):40-43.

[5] 张万东,陈宏,王一鹏,等.高电源抑制比和高阶曲率补偿带隙电压基准源[J].微电子学,2011,41(1):57-60.

[6] 曾健平,邹韦华,易峰,等.高电源抑制比带隙基准电压源的设计[J].半导体技术,2007,32(11):984-987.

[7] 徐冠南,贾晨,陈虹,等.一种极低功耗的CMOS带隙基准源[J].中国集成电路,2011,总(141):27-30.

[8] 毕查德·拉扎维.模拟CMOS集成电路设计[M].西安:西安交通大学出版社.

[9] 马卓,段志奎,杨方杰,等.1.8V供电8.2ppm/℃的0.18umCMOS带隙基准源[J].国防科技大学学报,2011,33(3):89-94.