一种高性能全差分运算放大器的设计

唐心亮,刘克智,王林锋

(1.河北科技大学人事处,河北石家庄 050018;2.河北工业大学微电子技术与材料研究所,天津300130;3.渤海石油职业学院,河北任丘 062550)

一种高性能全差分运算放大器的设计

唐心亮1,2,刘克智3,王林锋2

(1.河北科技大学人事处,河北石家庄 050018;2.河北工业大学微电子技术与材料研究所,天津300130;3.渤海石油职业学院,河北任丘 062550)

设计了一种具有高增益、大带宽的全差分折叠式共源共栅增益自举运算放大电路,适用于高速高精度流水线模数转换器余量增益电路(MDAC)的应用,增益自举运算放大器的主放大器和子放大器均采用折叠式共源共栅差分结构,并且主放大器采用开关电容共模反馈来稳定输出电压,该放大器工作在5.0 V电源电压下,单端负载为2 p F,采用华润上华(CSMC)0.5μm 5 V CMOS工艺对电路进行仿真测试,结果显示该运放的直流增益可达到126.3 dB,单位增益带宽为316 MHz。精度为0.01%时的建立时间为4.3 ns。

流水线ADC;增益自举;折叠共源共栅;采样电路

随着无线通信技术的飞速发展,模拟系统对模数转换器的性能提出了越来越高的要求,因而高性能模数转换器的设计与实现已成为混合集成电路设计中的核心问题。在众多类型的模数转换器中Pipelined ADC以其优良的性能得以广泛地研究和应用,而运算放大器是ADC中的关键模块,其有限的直流增益、有限建立时间、输入失调、噪声等都对增益余量放大电路(MDAC)的输出有很大影响,进而影响ADC的整体性能,例如,运算放大器有限的直流增益会限制ADC的分辨率和信噪比,运算放大器有限的建立时间会限制ADC的速度。因此需要高增益、大带宽、大摆率和大输出摆幅的运算放大器。

相对于单端输出运放,全差分运放有以下优点:具有相对于单短输出2倍的输出摆幅、对共模噪声的抑制;消除偶次谐波失真[1]。运算放大器作为模拟电路的主要模块采用全差分结构,要使运放具有高精度和高速度是非常矛盾的,因为高精度要求运放具有高的直流增益,而高速度要求运放具有大的单位增益带宽。在运算放大器的设计中,单端结构的运放具有大的增益带宽,主要有折叠式共源共栅结构和套筒式结构。

套筒式结构可以提供较高的增益和大的闭环带宽,但是其输出摆幅很小。由于有大共模输入范围和输出摆幅,折叠式共源共栅运放可以很容易将输入输出短接实现单位增益,较容易检测输入共模电平[2]。采用增益自举结构的全差分折叠式共源共栅运算放大器可以实现高速高精度的要求。本文采用增益自举技术设计了应用于10位高速Pipelined ADC的高性能全差分折叠式共源共栅运算放大器,并对其进行了仿真和测试。

1 增益自举技术

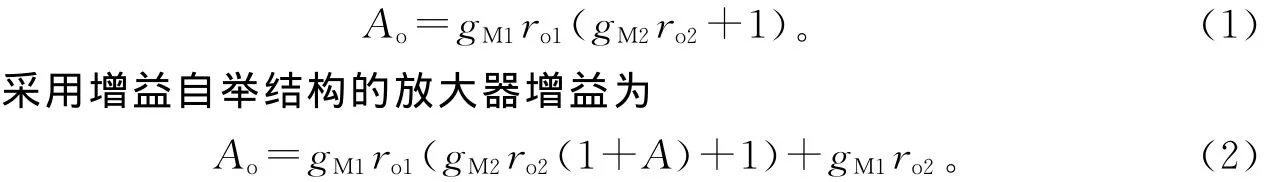

图1为增益自举结构原理图,其中M1和M2构成主运算放大器,A为子运算放大器,其放大倍数为A,放大器A驱动M2的栅极,迫使M1的漏端电压与参考电压Vref相等。当M2的源级变化ΔV时,M2的栅源电压变化(1+A)ΔV,这就相当于M2的跨导增加了(1+A)倍,从而迫使输出电压的变化对M1漏端电压的影响减小[3]。这样输出电阻Rout的大小几乎是常规共源共栅结构输出阻抗的A倍。未采用增益自举结构的放大器直流增益为

比较式(1)和式(2)可知,增益自举运放的直流增益提高了辅助运放的放大倍数,同时不影响运放的带宽和稳定性,消耗的功耗也较少。

图1 增益自举技术Fig.1 Gain-boosted technology

2 运放的设计和优化

2.1 运放的结构实现

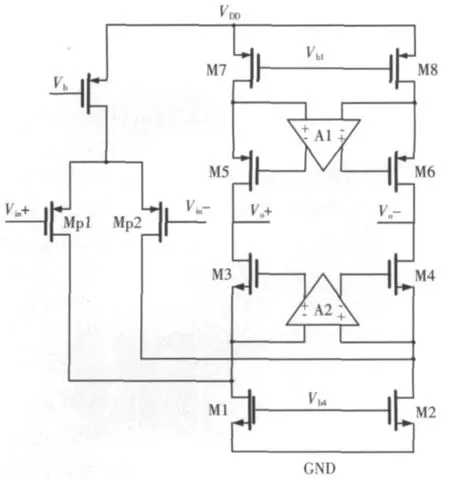

在众多的OTA结构中,套筒式结构作为单极结构具有最好的稳定性和最快的速度,但是其输出摆幅受限,很难使输入和输出短接在一起,而折叠式共源共栅结构具有更大的输出摆幅,更容易检测输入电平,所以应用比较广泛,本电路的主运放采用折叠共源共栅结构[4],其结构如图2所示。

主运放输入管采用PMOS管,主要是由于在n阱CMOS工艺中,PMOS管的衬底可以与其源端相连,不存在衬偏效应,因此线性度较好。由于折叠点采用NMOS管,且NMOS管的迁移率大约是PMOS管的3倍,所以在同一支路流经相同电流时,采用的NMOS管的尺寸小于PMOS管的尺寸,所以在相应的折叠点处的寄生电容比较小,使得次极点较远,有较好的频率特性。衬底噪声对PMOS管的影响较小,并且输入采用PMOS管优化了1/f噪声。

图2中,A1和A2作为辅助运放,其作用通过辅助运放来调节M1(M2)和M7(M8)漏端的电压,进而增加M1(M2)和M7(M8)漏端的输出阻抗来增加运放的直流增益[5]。

假设辅助运放为一个单极点系统,其增益为Aaux=Gaux/(1+Paux),并假设主运放为一个单极点系统,出于系统稳定性的要求,应调节辅助运放的频率响应特性使其3 d B带宽大于主运放,同时,由于辅助运放和主运放除主极点外在M3的源端共有一个次极点,且分别为2个运放自身唯一的一个次极点,所以为了使系统稳定,应当使此次极点的位置小于辅助运放的单位增益带宽(GBW),从而得到

图2 运放整体结构Fig.2 Fully differential gain-boosted amp

出于稳定性考虑,应当满足βωP1<ω1<ωP2,其中ω1为辅助运放的单位增益带宽,ωP1为主运放的单位增益带宽,ωP2为主运放的次极点,β为反馈系数。

2.2 辅助运放结构设计

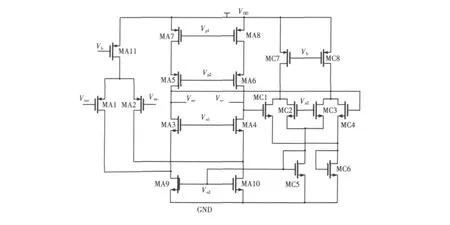

图3 辅助运算放大器A1的电路图Fig.3 Circuit diagram of boosting amp A1

图3为辅助运算放大器A1的电路图。由于A1的共模输入电平较低,选用PMOS管作为输入对管,因为在较低的共模输入时PMOS管是导通的。因为在辅助运放的输出端负载电容较小,因此为了保证其带宽不受影响,若采用共模反馈电路需采用较小的电容,这样由沟道电荷注入和时钟馈通效应引起的非线性误差更加明显,同时连续时间电路共模反馈不影响辅助运放的输出摆幅,采用连续时间共模反馈电路可以使运放的建立时间更短。图3中右半部分为连续时间共模反馈的实现电路[6]。

辅助运放A2的电路图类似于A1,唯一不同的是输入端采用NMOS管作为输入对,这里不再赘述。

2.3 共模反馈电路的设计

差分放大电路能够很好地抑制共模输入噪声和电源噪声,并且能够提供很大的输出摆幅,但是,当差分运放工作在采样保持电路的闭环状态下时,放大器的高差分增益虽然能够抑制差模信号,但是共模信号却极易受到影响,放大器需要额外的共模反馈电路来控制共模输出电压[7]。

在差分高增益的运算放大器中,当差分运放工作在反馈结构中时,高的差模增益可以稳定放大器的差模信号,但是其共模信号是悬浮的[8]。其输出共模电平对器件的特性和适配非常敏感,即使由于适配所造成的电流误差非常小,但是流经运放高的输出电阻后也能产生很大的电压降,导致运放工作于非线性区。因此运放需要共模反馈电路来稳定其共模输出电压。共模反馈电路必须能够补偿环路建立时间以及保持电路结构的稳定性。

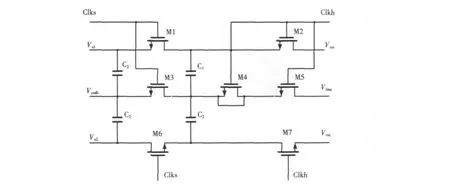

共模反馈电路通常分为2种结构:开关电容共模反馈电路(CMFB)和连续时间共模反馈电路。相对于连续时间共模反馈电路,开关电容电路消耗的功耗小,因为其是在双向不交叠时钟的控制下工作的,并且具有较大的输出摆幅,因此主运放采用开关电容电路作为共模反馈电路[9],其电路结构如图4所示。

图4 开关电容共模反馈电路Fig.4 Switch capacitance common-mode feedback circuits

其中Clks和Clkh为双相不重叠时钟,Vcmfb为共模反馈控制电压,其作用于主运放的尾电流源,使其电流值随Vcmfb的变化而得以调节。在Clks相位,C1和C2并联,C2两端的电压也由C1决定,并在每个Clks相位进行复位。在Clkh相位,C1被充电至Vcm~Vbias,电容C2将产生控制电压Vcmfb,进而稳定运放的输出共模电平。辅助运放采用连续时间共模反馈电路[10],其电路结构如图4右端部分电路。

3 仿真结果

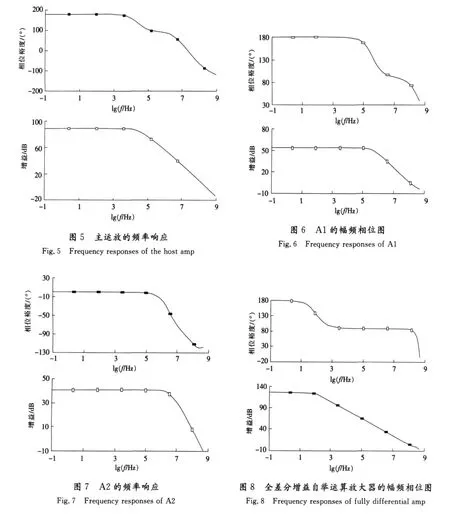

采用CSMC 0.5μm CMOS工艺对运算放大器进行仿真,电源电压为5 V,共模输入电压为2.5 V,单端负载为2 p F。图5为主运放的幅频相位图,由图5可得其直流增益为89.3 d B,相位裕度为89.3°,单位增益带宽为325.25 MHz。图6为辅助运放A1的幅频相位图,由图6可得A1的直流增益为51.3 dB,单位增益带宽为242 MHz。相位裕度为60.34°。图7为A2的幅频相位图,由图7可得A2的直流增益为40.6 dB,单位增益带宽为259.4 MHz,相位裕度为61.4°。图8为整体全差分增益自举运算放大器的幅频相位图,由图8可得,其直流增益为126 d B,单位增益带宽为316 MHz,相位裕度为60.7°。

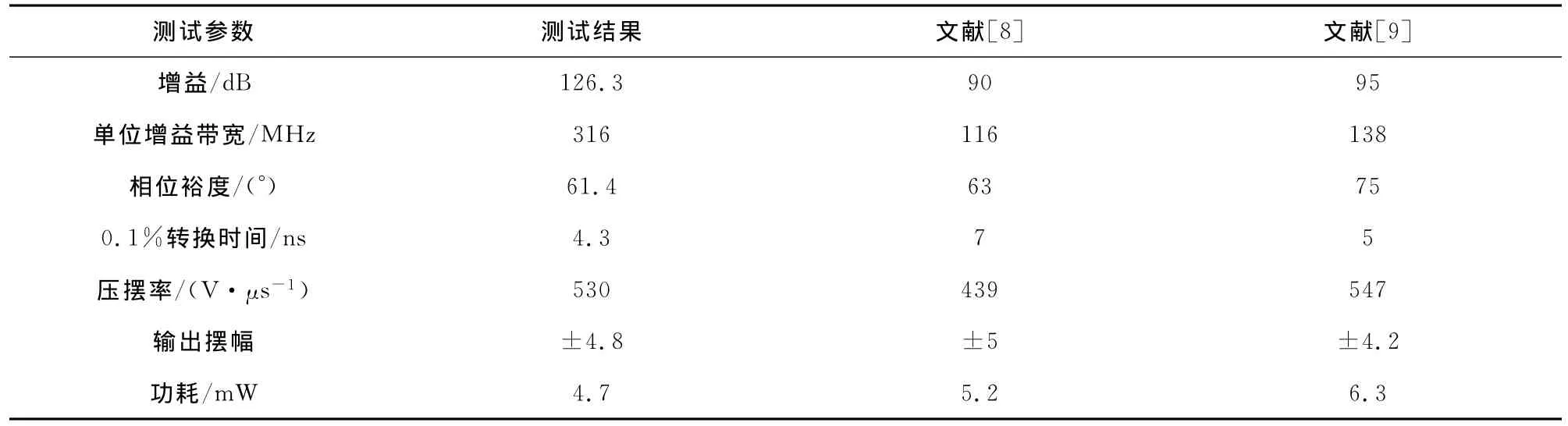

针对上述分析结果,在此基础上进行了版图的验证和寄生参数的提取,并对其进行了后端测试,测试结果如表1所示。

表1 运放的测试结果Tab.1 Summary of measured results

4 结 语

应用增益自举技术,采用华润上华(CSMC)0.5μm 5 V CMOS工艺设计了一款增益自举全差分运算放大器,采用开关电容共模反馈技术,更高的共模抑制比和精度,增加了稳定性,测试结果显示,在5 V电源电压供电的情况下,其开环增益可达到126.3 dB,相位裕度为60.7°,单位增益带宽316 MHz,功耗仅为4.7 m W,该运算放大器可用于高速Pipelined ADC和高性能采样保持电路中。

[1]LIOYD J,ae SEUNG L H.A CMOS op-amp with fully differential gain enhancement[J].Transactions on Circuits And Systems,1994,41(3):241-243.

[2]YAN J,RANDALL L G.Fasti-settling amplifier design using feedforward compensation technique[J].IEEE Circuits and Systems Socie-ty,2002,15(32):494-467.

[3]MARTINEZ J S,CASTRO F C.Improving the high-frequency response of the folded-cascode amplifiers[A].IEEE ISCAS′96[C].Atlanta:[s.n.],1996.500-503.

[4]MOTA D,PHANG K.Fundamentals of fully differential op-amps and CMFB circuits design[J].IEEE Journal of Solid-State Circuits,2005,39(18):37-68.

[5]NAGARAJ K,FETTERMAN H S.A 250 MW,8 b,52 M sample/s Parallel pipelined A/D converter with reduced number of amplifiers[J].IEEE JSSC,1997,32(3):312-320.

[6]HEO S C,JANG Y C,PARK S H,et al.An 8-bit 200 MSps CMOS folding interpolating ADC with a reduced number of preamplifers using an averaging technique[J].IEEE ASIC/SOC,2004,18(5):27-32.

[7]CHIU Y,GRAY P R,NIKOLIC B.A 14-b 12-MSs CMOS pipelined ADC with over 100 dB SFDR[J].IEEE Journal of Solid-States Circuits,2004,21(7):2 139-2 151.

[8]KAMATH B Y,MEYER R G,GRAY P R.Relationship between frequency response and settling time of operational amplifiers[J].IEEE Journal of Solid-State Circuits,1974(SC-9):347-352.

[9]ROBANA M,YUZMAN Y,TAN K Y.Design of single-state folded-coscode gain boost amplifier for 100 mW 10 bit 10 MS/s pipelined ADC[D].San Francisco:University of California,1998.

[10]甄可龙,吕善伟,张 岩.强电磁脉冲对抗对雷达接收机的天线耦合分析[J].河北科技大学学报(Journal of Hebei University of Science and Technology),2011,32(2):147-151.

Design of high-performance fully differential operational amplifier

TANG Xin-liang1,2,LIU Ke-zhi3,WANG Lin-feng1

(1.Department of Human Resources,Hebei University of Science and Technology,Shijiazhuang Hebei 050018,China;2.Institute of Microelectronic Technology and Materials,Hebei University of Technology,Tianjin 300130,China;3.Bohai Petroleum Vocational College,Renqiu Hebei 062550,China)

In this paper,a high gain and high fully differential gain boosted operational fold cascade amplifier is proposed.The amplifier is designed for MDAC of pipelined analog-to-digital converter.Both the main amplifier and the boosted amplifier adopt fully differential fold-cascade structure.The main amplifier uses a switched capacitance common mode feedback circuit to stabilize the output.With 5.0 V power supply,this circuit is designed in CSMC 0.5μm CMOS process.Spectre simulation shows that the whole amplifier has the DC gain of 126.3 dB and the unity gain bandwidth of 316 MHz under 2 p F single ended load,and the settling time is 4.3 ns with an accuracy of 0.01%.

Pipelined ADC;gain-boosted;fold cascade;samplingcircuit

TN432

A

1008-1542(2012)01-0050-06

2011-09-10;责任编辑:李 穆

唐心亮(1977-),男,河北成安人,博士研究生,主要从事微电子技术与材料方面的研究。