内置RTC作为电能表计时钟的应用

梁世清 包海泉 季海涛 何峥嵘

(江苏林洋电子股份有限公司,江苏 启东 226200)

0 引言

内置实时时钟 (real-time clock,RTC)在电能表成本方面具有优势,业界一般都是采用一片时钟芯片,如RX8025T。电能表是一种对时钟有精确要求的产品,但由于晶振受温度影响会产生频偏,导致时钟不精确。为了提高时钟的精确度,设计了一种温度补偿晶体频偏的RTC控制器。RTC时钟控制器能够实时补偿温度影响带来的频偏误差,从而得到精准的时钟。

1 软件校准RTC的原理

外接低速时钟信号(low speed external clock signal,LSE)的频率一般为32768Hz。当RTC预分频寄存器RTC_PRLH/RTC_PRLL(一个20位的寄存器)的频率设置为32768Hz时,RTC每隔32768个时钟周期输出一个秒脉冲。ANTI_TAMP管脚用来测试LSE晶振经64分频后的频率[1-10]。

软件校准RTC的原理如下。

①设置RTC时钟校准寄存器BKP_RTCCR;

② 每个单位能实现0.954×10-6(1000000/220)的精度校准;

③RTCCR寄存器取值范围为0~127;

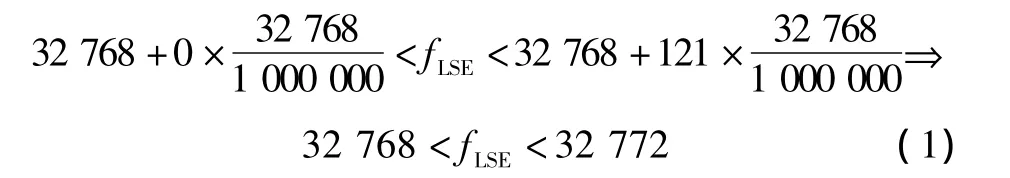

④对于32768Hz晶振,其可补偿频偏范围(调慢)为:

⑤设置RTC预分频寄存器RTC_PRLH/RTC_PRLL,如由预设值32768调整为32766;

⑥ 设置BKP_RTCCR寄存器,此时,对于32768Hz晶振补偿的频偏范围(调快)为:

RTC校准工作原理图如图1所示。

图1 RTC校准工作原理图Fig.1 Operational principle of RTC calibration

基于上述原理,内置RTC时钟控制器可以在固定的时间窗口32 s(220/32768)补偿晶振偏差带来的时钟偏差。在长期运行的条件下,电能表时钟精度可满足要求;但在短期内,通过测试秒脉冲平均精度来测试RTC精度,这种方案不可取。

此外,温度的变化会给晶体的晶振带来偏差,所以必须根据实时环境温度来调整频偏,即调整RTC预分频寄存器RTC_PRLH/RTC_PRLL和RTC时钟校准寄存器BKP_RTCCR的值。

2 内置RTC的应用

目前,内置RTC已经应用于国网内置(带载波)二代三相智能多功能电能表。RTC相关的硬件包括处理器(stm32f100vct6)自带的RTC,3.6 V电池供电(保证在外部电源停电的情况下,RTC正常工作);在软件方面,主要从校准RTC寄存器值和校准寄存器的调整这两个方面对RTC进行校准。下面主要从软件方面实现RTC的校准机制。

2.1 校准RTC寄存器值

爱普生32.768 kHz晶体频偏随温度变化的曲线如图2 所示[11]。

图2 晶体频偏随温度变化曲线Fig.2 Curve of the crystal frequency offset vs.temperature

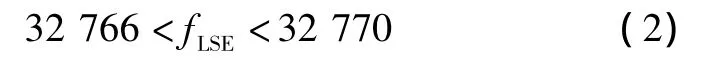

频偏和温度的数学模型为:

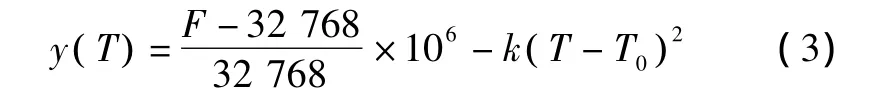

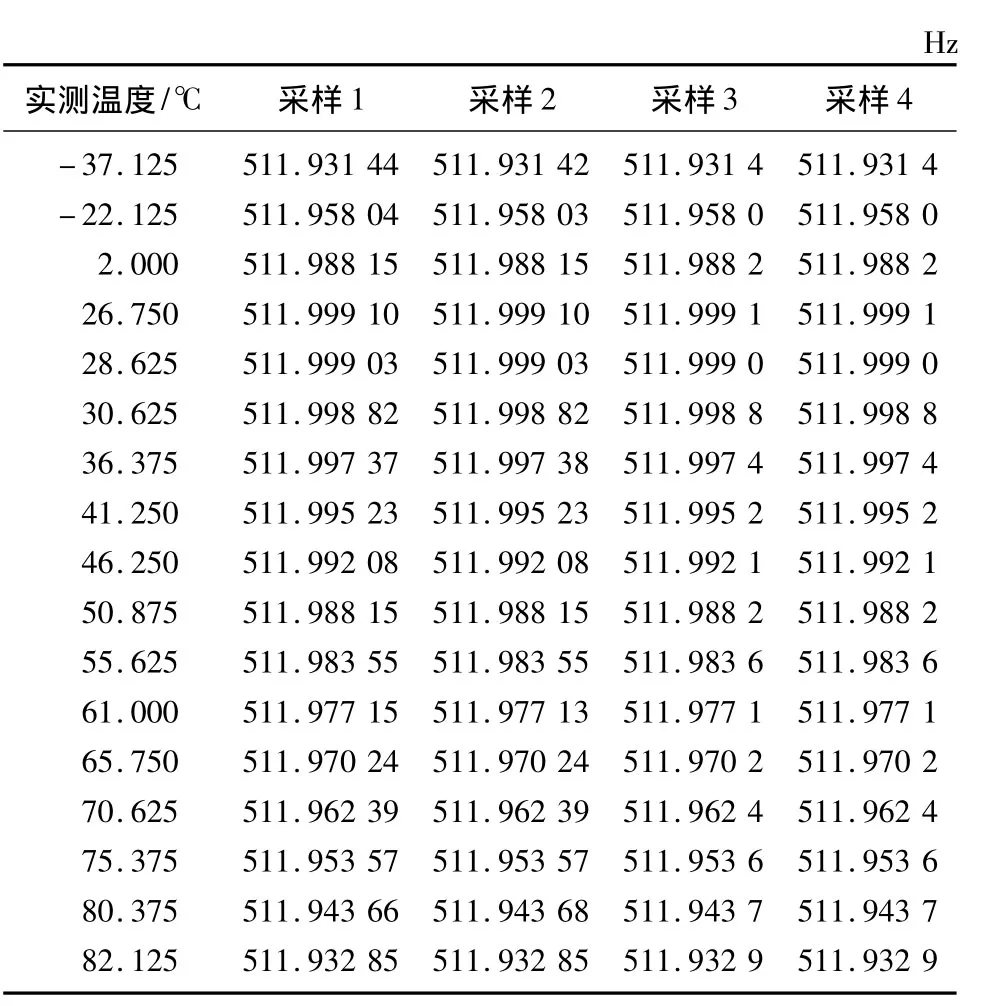

为了拟合接近实际晶振的二次系数k,并对同一批次的晶振进行数据采集和数据处理,在不同的温度下(用TCN75采集环境温度),采用频谱仪实验测试ANTI_TAMP(MCU的PC.13)管脚来获取精准的数据。温度-脉冲数-RTC晶振64分频频表如表1所示。

表1 晶振64分频频率表Tab.1 64 frequency division of crystal oscillation

根据表1的相关数据,经数据处理拟合得到k=-0.035。结合相关数学模型,可以生成一张温度-频偏的表。在国网项目中,生成了一张温度范围为-40~80℃共120个点的频偏表。

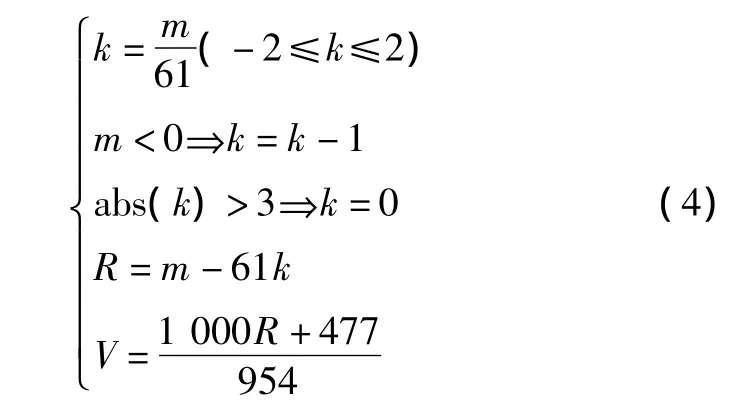

根据软件校准RTC原理,在实际的应用中,设实际调节步数为k,理论上可以分2步进行计算,即2×106/32768≈61×10-6;设实际调节的值为 R,实际校准寄存器的值为V,则有:

式中:m为通过查温度-频偏数据表得到的值。

设实际要调整的预分频寄存器的值为n,则有:

2.2 校准秒脉冲

三相表多功能表处理器的系统时钟T=18.432 MHz,而处理器的定时器均为16位。因此,无法得到一个1 s的计数器。

为了解决这个问题,采用处理器CortexTM-M3内核的24 位定时器(向下计数)进行500 ms定时[4],在500 ms定时器中断过程中对处理器的秒脉冲输出口线翻转,使秒脉冲输出口线输出秒脉冲。对于RTC的32768Hz晶振,一个周期(220/32768)=32 s。在32 s的周期内,每0.5 s进行误差计算,然后对32 s内的累积误差取平均,再将这个平均误差写入到24位定时器预分频寄存器,这样就能起到调整秒脉冲的目的,使时钟更加精确。

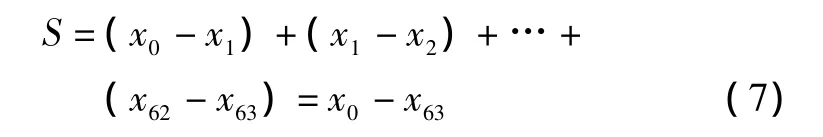

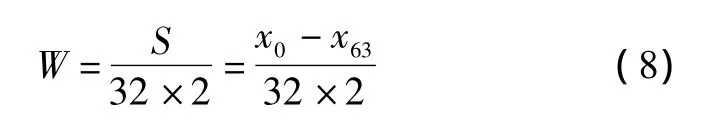

在软件设计方面,通过配置24位定时器500 ms产生定时器中断,在500 ms定时器中断过程中可以读出24位定时器预分频寄存器的值。理论上,每个500 ms读出的值应该是相同的,但实际上晶体的晶振会受温度影响产生频偏,所以就存在前一个500 ms读出的值与后一个500 ms读出的值不一致,这样相邻的500 ms就有一个误差。如在第一个1 s,前一个500 ms读出的值x0与后一个500 ms读出的值x1之间存在一个误差。同理,在第32 s,前一个500 ms读出的值x62与后500 ms读出的值x63之间也存在一个误差,于是在32 s的周期内就有64个这样的误差,称为累积误差和,那么要计算出0.5 s写入24位定时器预分频寄存器的值,只需将累积误差和除以64。以下是具体的推导过程。

设500 ms定时器中断写入预分频器的值为P:

设秒脉冲预分频器的值为Q,32 s累积误差和为S,则有:

在32 s的周期内,每个500 ms的平均误差W为:

所以实际写入脉冲预分频器的值Q为:

3 结束语

对于同一批次的晶振,在设定好晶振旁路的电容后,通过不必进行数据处理而直接用二次曲线的k值。内置RTC目前已经作为时钟成功应用于国网二代表,每天的平均误差小于0.5 s,满足国网技术条件要求,大大降低了产品的成本。内置RTC控制器也可以应用于其他对时钟有高要求的产品。

[1]王永虹,徐炜,郝立平.STM32系列ARM Cortex-M3微控制器原理与实践[M].北京:北京航空航天大学出版社,2008.

[2]张君.晶振实时测量系统设计[D].南京:南京航空航天大学,2004.

[3]邓乾中.自校准实时时钟RTC的研究和设计[D].武汉:华中科技大学,2008.

[4]李浩,兰铁岩.实时时钟芯片RTC4553原理及应用[J].电测与仪表,2003,40(8):35 -37.

[5]贾维.实时时钟 RTC的研究[D].西安:西安电子科技大学,2009.

[6]朱永峰,陆生礼,茆邦琴.SOC设计中的多时钟域处理[J].电子工程师,2003(11):60-61.

[7]谢修祥,王广生.异步多时钟系统的同步设计技术[J].电子工程师,2005(5):18 -20.

[8]李根岱.可校准实时时钟芯片的研究设计[D].武汉:华中科技大学,2009.

[9]白天力.基于RTC技术的即时通信软件的研究与设计[D].北京:北京邮电大学,2006.

[10]曾劲.内嵌电源管理的实时时钟芯片的研究与设计[D].武汉:华中科技大学,2009.

[11]许齐庆.晶体振荡器温频特性的改善[D].西安:西安电子科技大学,2010.