助听器多通道宽动态范围压缩的低功耗硬件实现

于增辉,黑勇,薛金勇,于伽,陈黎明,周玉梅

(中国科学院微电子研究所 专用集成电路与系统研究室,北京 100029)

数字助听器因具有高精度、低噪声、抗干扰、可控性好、算法灵活等优点,成为听障患者康复的新希望.但是我国数字助听器的研究远落后于国际先进水平[1],目前国内还没有数字助听器专用DSP流片成功的报道.

作为便携式医疗电子设备,数字助听器对功耗开销有着极为严格的要求:整机功耗1 mW左右,其中数字部分一般小于500μW[2].听力补偿是数字助听器中最重要的功能,通常采用多通道宽动态范围压缩(WDRC)算法实现[3-7].但是该算法的增益计算需要在线性刻度和分贝刻度间来回转换,涉及较多的非线性运算(对数、指数),硬件实现时功耗开销较大.关于简化增益计算中的非线性运算,文献[8]给出了一种基于泰勒级数展开的近似计算方法.但是该方法在输入信号范围较宽时,会引起较大的误差.文献[9]给出一种通过查表法简化对数和指数运算的方法,但是该方法仍然没有避免分贝刻度和线性刻度的转换,仍存在较多的运算开销.

由于WDRC增益计算所依据的信号声压级(SPL)检测本身存在较大的波动性和不准确性,从而允许采用一定的近似方法来简化运算.据此提出一种多通道WDRC的低功耗硬件实现方法.该方法基于查表实现了输入信号的平均能量和线性刻度的WDRC增益之间的直接映射,完全避免了指数和对数运算.并且,所采用的表格区间划分方法,使得查表误差远小于SPL检测本身的波动和误差;对查表结果进行递归平滑,在较好的抑制增益波动的同时,可通过灵活调整平滑常数来满足启动时间和释放时间的要求.仿真结果表明,在启动时间、释放时间相同的情况下,该方法得到的WDRC增益与直接计算的结果比较吻合,同时波动较小.此外,因无需对WDRC的输入输出(I/O)曲线作分段线性的约束,该方法可用于多种形状I/O曲线的配置,且不会增加控制复杂度以及存储和计算开销,相比文献[8-9]给出的方法而言有较大的优势.

在SMIC的0.13μm工艺条件下,基于该方法,完成了数字助听器DSP芯片中32通道WDRC模块的低功耗VLSI设计,并进行了流片.

1 多通道WDRC算法

听障患者的听力损失一般表现为听阈(人耳可感知的声压最小值)高于正常人,而痛阈(引起人耳痛觉的声压阈值)却不比正常人高.并且,在不同的频段上听力损失也不同,往往是高频部分的损失比较严重.听觉区域(听觉动态范围)是介于听阈和痛阈之间的声压范围[10].多通道WDRC算法,可在不同频段上,有针对性地对输入声音进行压缩或者放大,将正常人听觉动态范围内的声音,“映射”到听障患者的听觉动态范围内[11],从而能有效的提高患者对语音的辨识度.

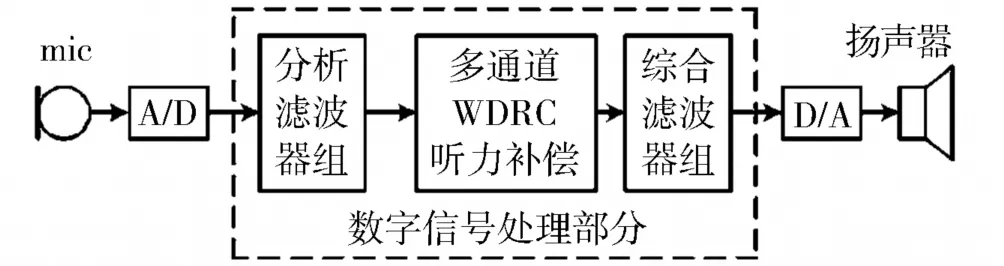

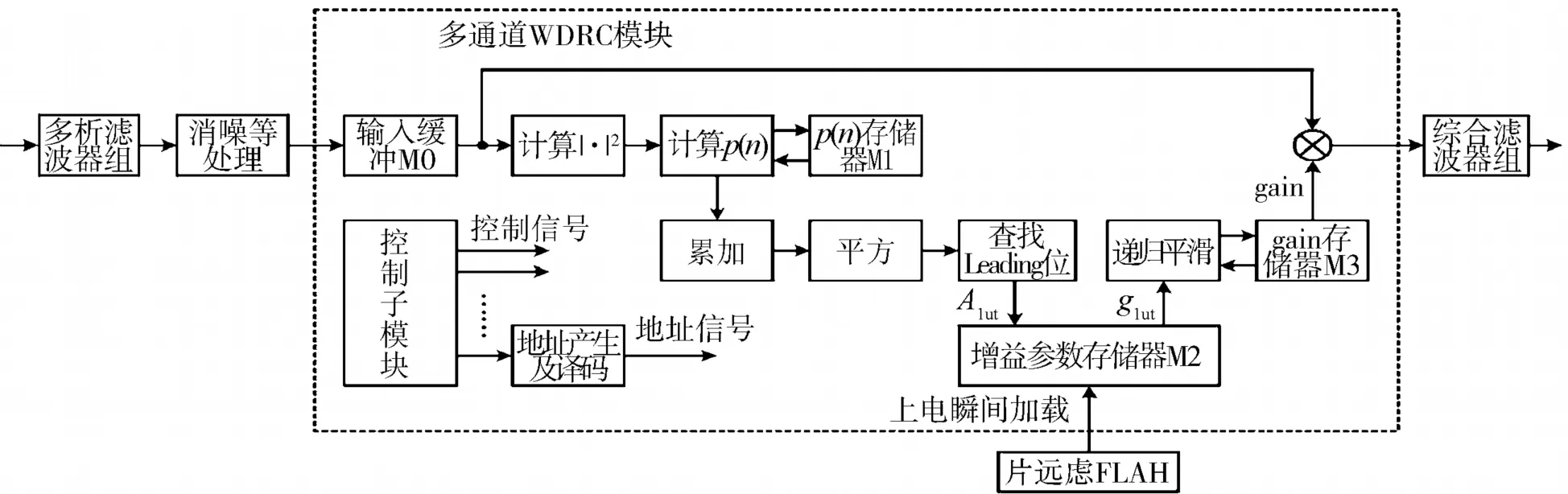

图1和图2分别给出了基于多通道WDRC听力补偿的数字助听器系统结构框图和WDRC模块的结构图[5].图1中的分析、综合滤波器组,分别实现对信号的多频率通道分离与合成.

图1 基于多通道WDRC的数字助听器Fig.1 Digital hearing aid based on multi-channel WDRC

图2 WDRC模块结构图Fig.2 Structure of the WDRC module

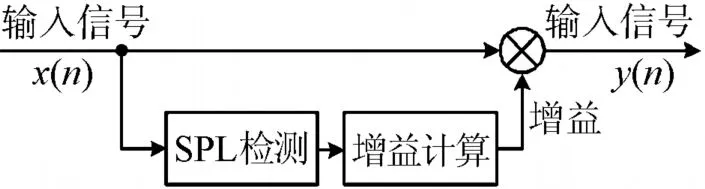

多通道WDRC的特性通常用通道数、I/O曲线以及启动时间、释放时间来描述.通道数反映了助听器对声音信号按频段处理的细致程度.I/O曲线描述的是输出与输入信号SPL的关系.2种常见的分段线性的I/O曲线如图3所示[2].启动时间和释放时间描述的是WDRC对输入信号能量发生变化时的反应速度.对于常用的音节压缩方式,启动时间和释放时间一般分别取5~10ms和50~100ms[2,5,12].通常要求助听器的I/O曲线和启动时间、释放时间是可配置的,以满足不同病人的需要.

图3 常见WDRC听力补偿I/O曲线Fig.3 Common type of I/O curves for WDRC

下面具体说明多通道WDRC算法的实现流程.

1)输入信号的 SPL 检测[5].

首先计算输入信号的平均能量p(n):

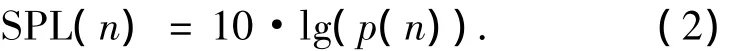

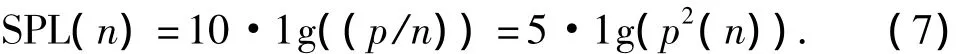

则声压级SPL为:

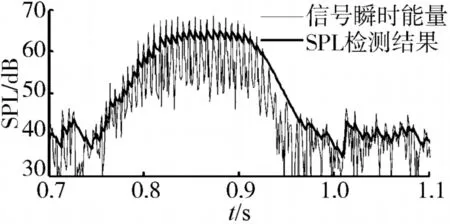

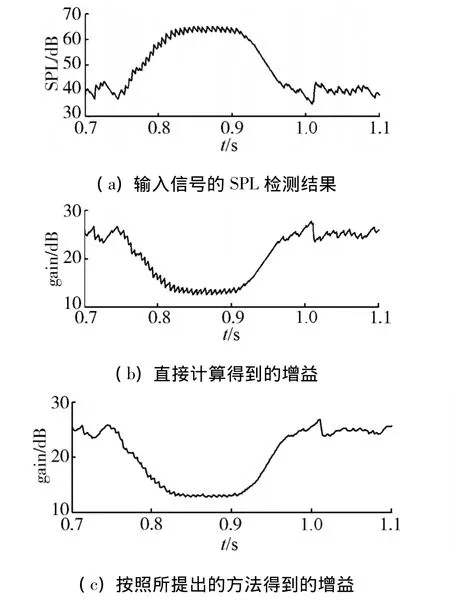

式中:n为时间帧标号,x(n)为输入信号(省略了通道标号),常数α和β用来调节启动时间和释放时间.图4给出了启动时间和释放时间分别取为5 ms和75 ms时,在输入信号的2.5 kHz处SPL检测的仿真结果.图中纵坐标为分贝刻度的信号瞬时能量和SPL检测结果.

图4 SPL检测结果Fig.4 The SPL detection result

2)增益值gain计算.

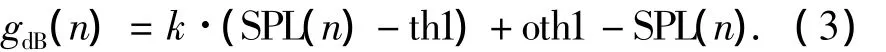

WDRC的增益是根据输入信号的SPL和对应通道的I/O曲线计算得到.以图3(a)为例,当输入信号的SPL小于th1时,处于线性放大区,增益为预先设定的固定值.当th1≤SPL(n)<th2时,处于压缩区,设该区的压缩比为 CR,I/O曲线斜率k=1/CR,则分贝刻度的增益计算方法为[6]

若SPL(n)≥th2,则处于限幅区,增益为:

由gdB(n)计算线性刻度的增益:

3)对输入信号进行压缩/放大.

经过WDRC后输出的信号y(n)为

4)对每一个通道按照上述过程进行处理,然后经过综合滤波器组合并为一路信号,即得到听力补偿后的输出.

根据上述实现过程,WDRC的增益计算需在分贝刻度和线性刻度间来回转换,涉及较多对数和指数运算,开销很大.如何简化或消除这些非线性运算,是多通道WDRC低功耗硬件实现的关键.

2 多通道WDRC的低功耗硬件实现

2.1 低功耗硬件实现方法

根据文献[2]以及上一节的仿真结果显示,SPL检测具有如下特点:

1)通过选择较长的启动/释放时间可以减小SPL检测结果的波动,但该波动不可完全消除(如图4的信号波峰处,SPL的波动幅度达3 dB以上);

2)较长的释放时间,使得在信号能量下降阶段的SPL检测结果明显大于信号实际的SPL;

3)SPL的检测结果随启动时间和释放时间设定的不同,也存在较大的变化.

上述特点造成SPL检测结果必然存在较大的波动性和不准确性,依据该检测结果对WDRC增益进行完全精确的直接计算,是没有必要的.在满足启动时间、释放时间要求,并且保证较小的计算误差和增益波动的前提下,可采用适当的简化计算的方法.基于此,提出一种基于查表法计算WDRC增益的方法,完全避免了线性刻度和分贝刻度的转换,从而彻底消除非线性运算.具体如下:

1)按照SPL划分表格区间.

首先,将助听器每个通道输入信号的SPL范围(一般不大于120 dB)均分为64个区间,每个区间包含的SPL范围小于2 dB.以区间中心的SPL值代表整个区间的SPL,则最大误差小于1 dB,且该误差远小于上文提到的SPL检测结果大约3 dB的波动.

以每个区间中心的SPL值对应的增益作为该区间的增益.预先根据患者的听力补偿I/O曲线将每一个通道的64个增益值计算出来,并作为表格参数存放在存储器中,从而不占用硬件计算资源.

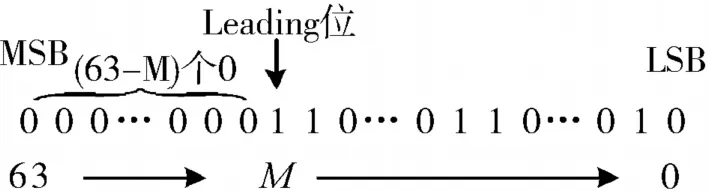

2)查找Leading位确定信号SPL所处区间.

在设计中采用的输入输出数据为16 bit(含1 bit符号位),平均能量p(n)以32 bit表示.这里p(n)的计算方法同式(1).为了查表方便,先将p(n)平方得p2(n),p2(n)为64 bit.则声压级SPL计算如下:

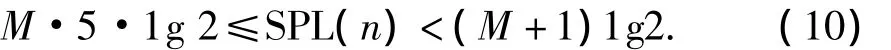

设p2(n)的Leading位(这里是最高非零位)是第 M 位,M=0,1,2,……63.则满足

即:

则p2(n)对应的SPL处于第M区间内.因此,可以用查找Leading位的方法(见图5),由p2(n)直接确定信号的SPL所处区间,避免了对数运算.同时,查找Leading位操作本身的硬件和功耗开销均很小.

图5 查找Leading位Fig.5 The leading bit searching

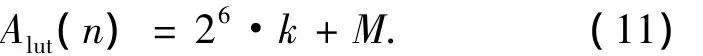

3)查表求WDRC增益.

设通道标号为k,则增益查表地址Alut为

式中:k=0,1,2……K -1,K 为通道总数.实际上直接将M作为地址Alut的低6位,通道标号k直接作为高位即可,从而无需加法运算.

以此地址读取增益参数存储器,即可得到对应的增益值glut(n).并且该增益值直接以线性刻度表示,避免了指数运算.

4)增益平滑与启动/释放时间调整.

增益值较大的波动会造成失真,影响听力补偿后的音质[2].因为信号的SPL检测本身存在较大的误差和波动,加上查表带来的误差,由上述过程所得到的增益值不可避免的存在波动.为了减少波动,采用下式对glut(n)进行递归平滑,得到最终的增益:

式中:αg和βg是平滑常数.该式除了可平滑增益,还可与式(1)一起调整启动时间和释放时间.此时,启动时间和释放时间可通过灵活选择αg、βg、α、β这4个平滑常数的值来调整.

5)通道组合减小存储及计算开销.

考虑到滤波器组的硬件实现复杂度和线性相位等方面的要求,目前的多通道处理一般采用等带宽通道划分方式.但由于人耳对声音频率的感知与频率高低近似为对数关系[10],高频部分无需在每个通道计算增益.因此,助听器设计中常常在将高频通道进行组合后计算增益,降低参数存储和增益计算的开销[2].

高端数字助听器的输入采样率一般为16 kHz,为了在低频部分达到较细致的频段划分,设计中采用32通道划分方案(K=32).同时,采用将高频通道按照倍频程进行组合的方式,将32个通道合并为10个频带,以每个频带内各通道的总平均能量来查表计算该频带的WDRC增益.这样存储和计算开销仅为通道组合前的10/32.

2.2 仿真与性能分析

图6(a)是在输入信号2.5 kHz频率处的SPL检测结果,图6(b)和(c)分别是对应的按照直接计算法和所提出的方法仿真得到的WDRC增益.其中启动时间和释放时间分别设置为5 ms和75 ms.由图可见,采用所提出方法得到的增益和直接计算得到增益比较吻合,同时波动也比较小.

图6 增益计算仿真结果分析Fig.6 Simulation results analysis of gain computing

表1是采用所提出的低功耗硬件实现方法和文献[9]给出的方法进行一次WDRC增益计算(按照图3的分段线性I/O曲线),在运算和存储器读写方面的开销比较(包含了增益平滑的开销).所提出的方法无需对输入信号的SPL所处的区段(线性区、压缩区、限幅区等)进行判断,从而在所有SPL值情况下的开销完全相同.从表1可以看到,在每个区段,该方法均比文献[9]给出的方法开销要小.

表1 所提出的方法与文献[9]方法的开销比较Table 1 Comparison of operating costs between the proposed method and the method in reference[9]

另外,直接计算法以及文献[8]和[9]给出的实现方法,在计算增益时,均需对I/O曲线作分段线性的约束,且分段越多,控制就越复杂,存储和计算的开销也越大.而所提出的方法,实现过程无需对I/O曲线作任何约束,从而除了图3给出的I/O曲线外,该方法还可以用于非分段线性等多种形状的I/O曲线配置,并且不会增加控制复杂度以及存储和计算开销.因此,在I/O曲线配置的灵活性方面,所提出的方法远比文献[8]和[9]给出的方法有优势.

综上,所提出的WDRC实现方法在确保较小的查表误差和增益波动的前提下,实现了输入信号的平均能量和线性刻度的WDRC增益之间的直接映射,完全避免了非线性运算,降低了总体计算开销.而启动时间和释放时间的要求,可以通过灵活调整α、β,αg、βg这4 个平滑常数来满足.最后,相比文献[8]和[9]给出的方法而言,该方法还具有I/O曲线配置比较灵活的优势.

3 VLSI设计与流片测试

所提出的多通道WDRC低功耗硬件实现的具体电路结构以及与数字助听器中其他主要模块的连接如图7所示,其中白线框内的为多通道WDRC模块.基于第2部分给出的低功耗实现方法进行设计,该模块仅涉及乘法、加法、查找Leading位、存储器读写等简单的操作.

图7 所提出的多通道WDRC硬件实现结构图Fig.7 The proposed hardware realization framework for multi-channel WDRC

图7中计算p(n)以及递归平滑子模块分别按照式(1)和(12)进行,累加运算实现对需要组合的通道的能量进行累加.M0~M3为位宽和深度各不相同的存储器,其中M2中的增益参数,采用在系统上电瞬间由片外FLASH加载的方式实现配置.控制子模块提供其余各个子模块的操作时序控制信号;地址产生及译码子模块产生各存储器的读写地址,因为采用通道组合后M3只有10个地址单元,设计中采用了开销极小的译码电路实现地址范围从0~31到0~9的转换.

此外,数据从M0读出直到增益gain写入M3的处理过程,采用流水线的方式,减少了总体运算时间的开销,从而有助于降低系统时钟频率和时钟树的翻转功耗.在此基础上,利用Design Compiler综合工具自动插入时钟门控,关断不工作的子模块,减少无用翻转,进一步降低动态功耗.

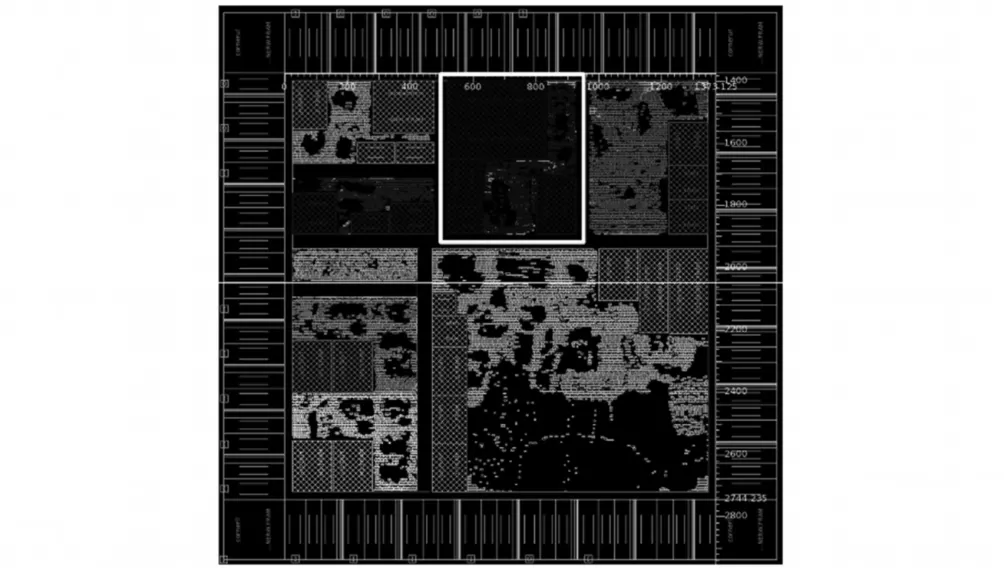

最后,基于上述方法,在SMIC的0.13μm工艺条件下完成了32通道WDRC模块的低功耗VLSI设计,并作为整个数字助听器专用DSP芯片Aid101的一部分进行了流片.图8为Aid101芯片的版图,其中白线框内的是所设计的32通道WDRC模块,该模块的版图面积为 0.45 ×0.55 mm2.

图8 数字助听器DSP芯片Aid101的版图Fig.8 Layout of the digital hearing aid DSP Aid101

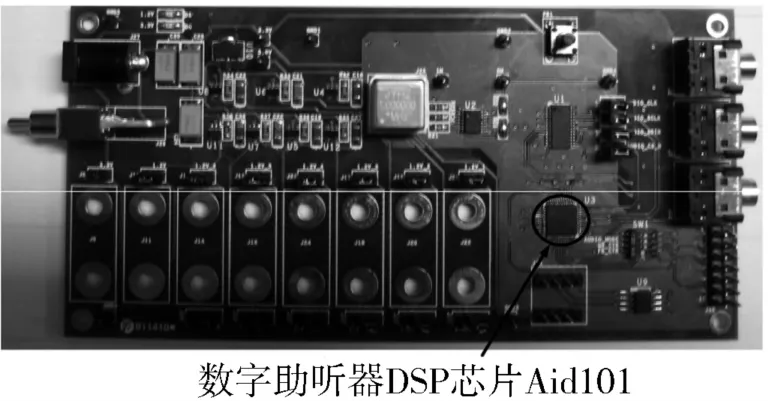

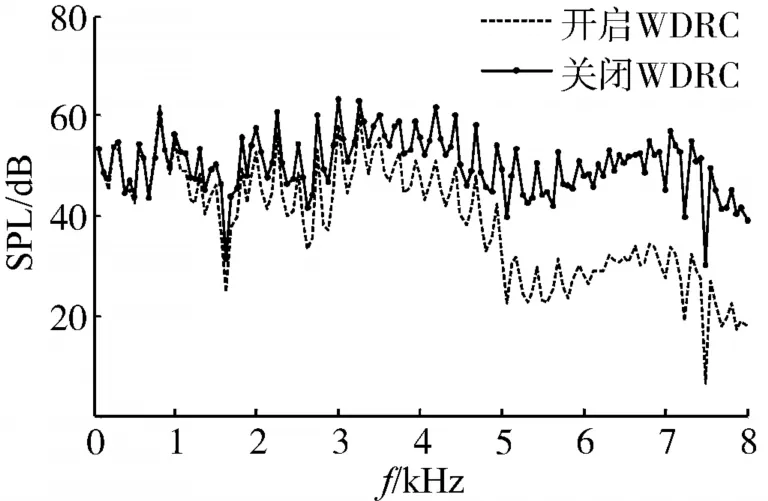

图9为Aid101芯片的板级测试系统.经过测试,该系统能较好的实现数字助听功能.图10是多通道WDRC模块的性能测试结果(显示的是某时刻的频谱分析).从听力补偿功能开启与关闭状态下的语音处理结果的频谱曲线对比可知,该模块能在不同的频段根据听力损失和SPL的不同,对信号能量进行不同程度的补偿,同时很好的保持了频谱原有的形状.最后,在1.3 V内核工作电压和2.3 MHz的系统工作频率下,所设计的32通道WDRC听力补偿模块的功耗仅为19.2μW.

图9 Aid101芯片的PCB测试系统Fig.9 PCB testing system for Aid101

图10 WDRC功能测试结果Fig.10 Testing result of WDRC

4 结论

在分析了数字助听器多通道WDRC算法中声压级检测特点的基础上,提出一种基于查表法的低功耗硬件实现方法.

1)该方法实现了输入信号的平均能量和线性刻度的WDRC增益之间的直接映射,同时采用合适的表格区间划分和对查表结果进行递归平滑的方法,可以保证较小的查表误差和较小的增益波动.与中已有方法相比,该方法完全避免了非线性运算,在计算开销方面优势明显;另外,在不增加控制复杂度以及存储和计算开销的前提下,可实现比较灵活的I/O曲线配置.

2)由于每个通道需要存储64个增益参数,尽管可以采用通道组合的方法,但是仍需要较多的存储器开销,这是该方法的一个主要缺点.

3)在SMIC的0.13μm工艺条件下,基于该实现方法,完成了数字助听器 DSP芯片中32通道WDRC模块的低功耗VLSI设计,并进行了流片.实测结果表明,该模块能很好地实现听力补偿的功能,并且正常工作的功耗仅为19.2μW.现[D].北京:清华大学,2010:1-18.WENG Haibo.Study on digital hearing aid algorithm with dual microphone inputs and its embedded implementation[D].Beijing:Tsinghua University,2010:1-18.

[1]翁海波.双麦克风输入的数字助听算法研究与嵌入式实

[2]JAMESM K.Digital hearing aids[M].Oxfordshire:Plural Publishing,2008:1-16,221-262.

[3]WILILIAM E Y,CHRISTINA M R,HELEN J S,et al.Acclimatization in wide dynamic range multichannel compression and linear amplication hearing aids[J].Journal of Rehabilitation Research & Development,2006,43(4):517-536.

[4]GARININ.Compression techniques for digital hearing aids[D].Patras:University of Patras,2009:1-19.

[5]KUO Yu,LIN Tayi,CHANGW.Complexity-effective auditory compensation for digital hearing aids[C]//IEEE International Symposium on Circuits and Systems(ISCAS).Washington DC,USA,2008:1472-1475.

[6]KIM N,SIMON D,ANN S,et al.An integrated approach for noise reduction and dynamic range compression in hearing aids[C]//16th European Signal Processing Conference(EUSIPCO).Lausanne,Switzerland,2008.

[7]WEI Chengwen,KUO Yuting,CHANG Kuochiang,et al.A low-power mandarin-specific hearing aid chip[C]//IEEE Asian Solid-State Circuits Conference. Beijing,China,2010.

[8]NEERAJM,SANMATIK,FRANK L,et al.Development and fixed-point implementation of a multiband dynamic range compression(MDRC)algorithm[C]//Proc ACSSC.Pacific Grove,California,USA,2000.

[9]CHANG K,KUO Y,LIN T,et al.Complexity-effective dynamic range compression for digital hearing aids[C]//IEEE International Symposium on Circuits and Systems(ISCAS).Paris,France,2010.

[10]王青云,赵力,赵立业,等.一种数字助听器多通道响度补偿方法[J].电子与信息学报,2009,31(4):832-835.WANG Qingyun,ZHAO Li,ZHAO Liye,et al.A multichannel loudness compensation method for digital hearing aids[J].Journal of Electronics& Information Technology,2009,31(4):832-835.

[11]BRIAN D P.Dynamic compression in a hearing aid[P].USA:US 7305100 B2,2007.

[12]SHIL F.Effect of dynamic compression characteristics on aided perception of reverberant speech[D].Syracuse:Syracuse University,2006:1-114.

——一个解释欧姆表刻度不均匀的好方法