一种基于偏移源的频率合成技术分析

陈焕东,牛 旭,刘立青

(中国电子科技集团公司第五十四研究所,河北石家庄 050081)

0 引言

频率合成技术有超过60年的发展历史,各种频率合成技术层出不穷。据报道,美国Phase Matrix公司在2009年发布了一种新的基于偏移源的频率合成技术开发的频率合成器[1],该频率合成器相位噪声和杂散信号指标都非常出色,使得基于偏移源的频率合成技术在近几年逐渐成为一个研究热点。

分析基于偏移源的频率合成技术的相位噪声和杂散信号产生原理,并通过实际应用加以验证,对设计低相位噪声和低杂散信号的频率合成器有重要意义。

1 相位噪声分析

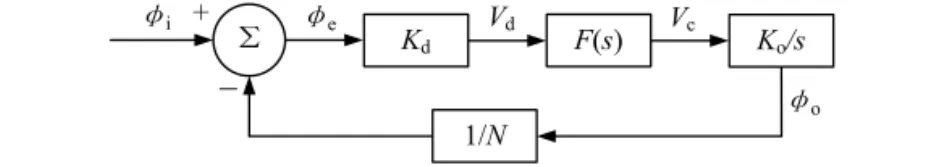

1.1 PLL线性模型

PLL已经成为使用最广泛的频率合成技术之一,几乎所有的频率合成器都使用PLL。PLL是一种负反馈系统,锁定后鉴相器的2个输入信号的相位φo/N和φi之间保持一个恒定的相位差φe。在锁定后,可认为PLL是线性的,其线性模型如图1所示。

图1 PLL线性模型

PLL闭环传递函数可表示为:

实际应用中,常用估算公式如下:

式中,ωn为PLL自然角频率。

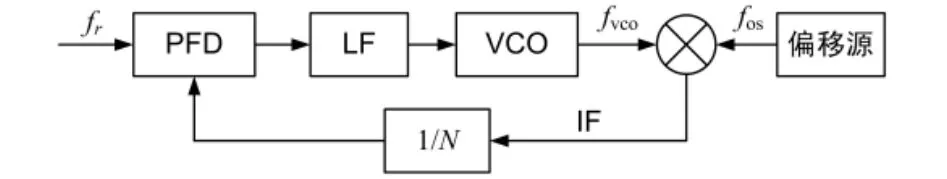

1.2 基于偏移源的PLL相位噪声

如图2所示,在PLL反馈支路中加入偏移源和混频器构成一种基于偏移源的PLL。除了偏移源,其他部分称为主环。

图2中PFD为鉴频鉴相器,LF为环路滤波器。VCO信号fVCO、偏移源信号fos和鉴相信号fr之间的频率关系为:

图2 带偏移源的PLL

假设PLL中各个部分为理想无噪声,加入等效噪声源建立相位噪声模型[1],对其进行相位噪声分析,如图3所示。

图3 加入偏移源的PLL相位噪声模型

图3中,Δφo为系统输出相位抖动;Δφos为偏移源fos的相位抖动;Δφi为参考源相位抖动;VnPD为PD引入的噪声电压;ΔφVCO、Δφnd分别为VCO和N分频器的相位抖动。

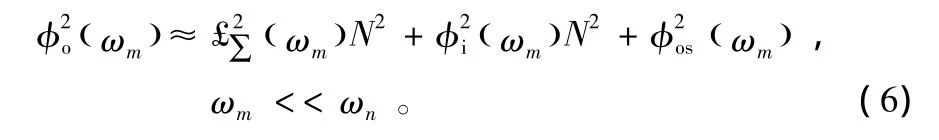

由式(6)可以看出,经过闭环响应后,系统固有相位噪声基底(ωm)恶化20lgN dB;加入偏移源后,偏移源相位噪声(ωm)和环路分频比N没有关系。系统环路带宽内的相位噪声由系统固有噪底、参考源相位噪声、分频比N和偏移源相位噪声共同决定决定。

根据式(4),如果fos和fVCO频率非常接近,那么分频比N就很小。根据式(6),减小分频比N后,系统固有相位噪声基底就不再是决定系统相位噪声的主要因素,偏移源相位噪声成为决定系统相位噪声的主要因素。

2 杂散信号分析

2.1 偏移源引入的杂散信号

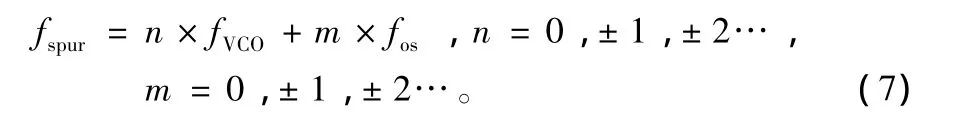

频率合成器中存在诸多非线性电路,如混频器、分频器和鉴相器等。当多种频率信号通过非线性电路时会发生交调响应,产生许多杂散信号,当杂散信号落入PLL环路带宽内时,杂散信号会恶化。

令杂散信号fspur为:

当n和m的绝对值越小,并且fspur小于环路带宽时,杂散信号越恶劣。通常杂散信号出现在fVCO±fspur频率上。

这种杂散信号主要是由于混频器端口间隔离度有限,造成fVCO信号和fos信号在偏移源内部发生交调响应而产生杂散信号。当这种杂散信号在VCO输出频率距离偏移源的鉴相频率整数倍频率非常近的时候尤为明显。在混频器和偏移源之间加入一个反向隔离度高的放大器是降低这种杂散信号比较好的方法。此外,偏移源和主环在空间布局和电源方面也要采取严格的隔离措施,以减小相互间的干扰。

2.2 DDS引入的杂散信号

为获得微小频率步进,往往要使用DDS。由于相位截断,有限字长和DAC非线性等因素造成DDS杂散信号输出的不确定性,因此在一些PLL+DDS的方案中,DDS杂散信号是一个困扰设计师的难题。将DDS输出作为PFD的参考输入,根据式(6)可知,DDS引入的杂散信号经过闭环相应后要恶化20lgN dB。采用偏移源后,环路分频比得到大大减小,甚至为1,所以由DDS引入的杂散信号经过闭环响应后恶化很小或者是无恶化。DDS远端杂散信号可以很轻松地被环路滤波器滤除。

3 关键技术

3.1 偏移源合成技术

偏移源可以是单一信号输出或者是有一定带宽的信号输出。根据不同应用偏移源的合成方式有很多种,可以采用PLL和梳状谱发生器等。目的是获得尽可能低的相位噪声。

如果偏移源采用数字PLL,可以提高鉴相频率,增大频率步进,以降低环路分频比,从而获得低相位噪声。要获得更低的相位噪声,可以采用模拟PLL。但无论是数字PLL还是模拟PLL在低相位噪声和带宽上相互制约,要获得低相位噪声往往难于实现较宽的带宽。

采用梳状谱发生器可以很轻松地获得倍频程的频谱带宽[3]和极低的相位噪声。比如,使用梳状谱发生器将100 MHz OCXO倍频到4~8 GHz,倍频次数40~80,相位噪声理论恶化32 ~38 dB;OCXO在偏离载波100 kHz处相位噪声为-170 dBc/Hz,所以经过倍频后8 GHz信号在偏离载波100 kHz处相位噪声小于-130 dBc/Hz。

3.2 主环合成技术

因为主环的分频比很小,噪底非常低,相位噪声和杂散信号不再是主环要解决的主要问题。其参考输入可用微小频率步进对偏移源频率间隔进行“填充”,从而连续覆盖所需的输出带宽,实现宽带小步进。鉴相器采用低噪底的 PLL芯片,例如ADF4002。混频器采用宽带高隔离度的混频器,以提高主环和偏移源之间的隔离度。在一些情况下,还必须加入D/A转换进行频率预选,避免发生错锁。要特别注意式(4)中主环和偏移源频率之间的关系,正确设置主环的鉴相极性。

4 工程应用

结合工程实践,介绍一种基于偏移源的频率合成技术设计的C频段频率合成器,主要指标要求如下:

输出频率范围:4.6 ~5.4 GHz;

频率步进:1 kHz;

相位噪声:

≤-65 dBc/Hz(偏离载波0.1 kHz处);

≤-75 dBc/Hz(偏离载波1 kHz处);

≤-85 dBc/Hz(偏离载波10 kHz处);

≤-95 dBc/Hz(偏离载波100 kHz处);

杂散信号:≤-70 dBc。

C频段频率合成器方案如图4所示。将10 MHz参考源分2路,一路5倍频后作为偏移源的参考;另一路作为1 GHz DDS时钟源的参考。偏移源信号和2.3~2.7 GHz的VCO输出信号进行下混频,混频器使用HMC213,射频端口和本振端口的隔离度大于40 dB。混频后的中频信号IF先经过一个低通滤波器LPF,滤除远端的杂散信号,LPF采用LTCC低通滤波器LFCN-1800;然后IF信号和DDS输出信号fdds在ADF4002内部进行锁相。最后经2倍频和滤波后输出。由式(4)可得各频率间关系:fVCO=fos±fdds× N 。fos取2.4 GHz或2.5 GHz;fDDS取50~100 MHz;当N的取值为1时,中频IF为50~100 MHz;当 N的取值为2时,中频 IF为100~200 MHz。

图4 C频段频率合成器方案

如果环路带宽取3 MHz,最终主环频率合成后在0.1~100 kHz处的相位噪声(ωm)主要由fos的相位噪声(ωm),fdds的相位噪声(ωm)N2和主环噪底(ωm)N2三部分相迭加而成。

偏移源采用低噪底PLL芯片ADF4106去锁一个2.4~2.5 GHz的低相位噪声 CRO,鉴相频率取50 MHz,环路带宽取20 kHz。偏移源的实测相位噪声( ωm)如表1所 示,其中( ωm)N2为 -135 dBc/Hz。

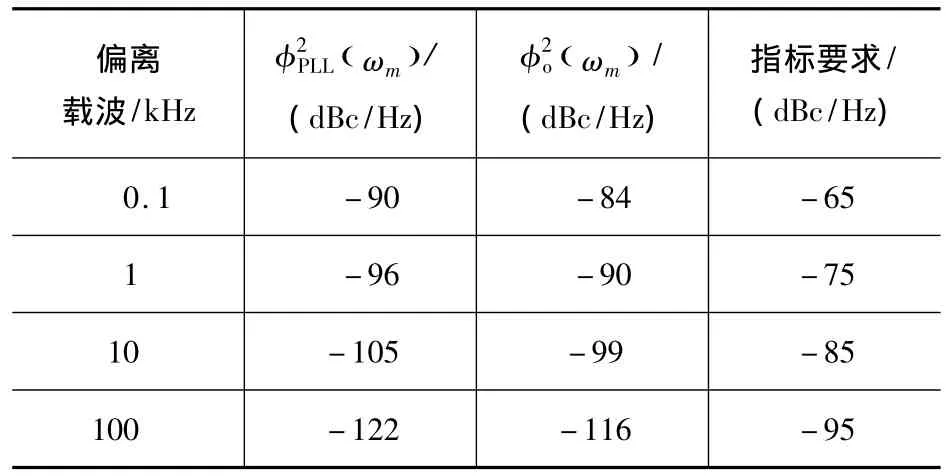

表1 C频段频率合成器各部分相位噪声理论迭加

主环采用低噪底PLL芯片ADF4002,其噪底为-222 dBc/Hz;当环路分频比N为2,鉴相频率为100 MHz时,主环噪底(ωm)N2为:

DDS窄带输出无杂散信号动态范围(SFDR)小于 -90 dBc[2],主环分频比最大为 2,所以 DDS 杂散信号对系统的影响可以忽略;分别在混频器和偏移源之间,混频器和 VCO之间加入一级放大器HMC308,其增益为18 dB,输出压缩点大于17 dBm,反向隔离度为35 dB;一方面可以将fVCO信号放大至混频器本振信号要求的信号强度,另一方面很容易提高主环和偏移源间的隔离度;此外对主环和偏移源之间从空间布局和PCB布局上进行严格的分腔隔离设计,以减小相互间的干扰,实测杂散信号≤ -70 dBc。

5 性能测试结果分析

完成调试后对C频段频率合成器进行测试,实测主环输出相位噪声(ωm)的结果如表2所示。

表2 C频段频率合成器相位噪声对比

可以看出实测结果和理论迭加结果一致,这表明采用偏移源的频率合成方案,系统噪底非常低,在这种情况下系统噪底不再是决定相位噪声的主要因素,其相位噪声主要由偏移源相位噪声决定。2倍频后系统输出相位噪声(ωm)如表2所示,系统输出相位噪声测试结果远优于指标要求。此外,杂散信号≤-70 dBc。采用基于偏移源的频率合成技术实现了低相位噪声,低杂散信号设计。

6 结束语

采用基于偏移源的频率合成技术,可以大大降低主环的环路分频比,从而降低主环的噪底,这是该技术的核心。在毫米波段,偏移源采用取样脉冲锁相技术,在偏离载波100 kHz处相位噪声已经做到-105 dBc/Hz。综上所述,采用基于偏移源的频率合成技在低相位噪声和低杂散设计上有明显的优势。 ■

[1]QuickSynTM Microwave Frequency Synthesizer. Phase Matrix Inc[S],2009.

[2]AD9912 Datasheet.Analog Device Inc[S],2007.

[3]杨新功,宋庆辉.超宽带低相位噪声频率合成器的实现[J].无线电通信技术,2006,32(3):39 -41.

[4]白居宪.低噪声频率合成[M].西安:西安交通大学出版社,1995.

[5]胡丽格,杨志国,闵 洁.一种L波段的小步进频率合成器[J].无线电工程,2007,37(6):60-61.

[6]温明艳.多环频率合成器抗干扰研究[J].无线电通信技术,2002,28(5):29-31.