一种新型数字化中频调制解调器设计

李 勇,刘 洋

(中国电子科技集团公司第五十四研究所,河北石家庄 050081)

0 引言

近年来随着软件无线电技术的快速发展,结合高性能的模数转换器(ADC)、数模转换器(DAC)和大容量现场可编程门阵列(FPGA)器件的应用,使得体积小、功耗低、重量轻的调制解调器实现成为可能。该方案设计了一种新型的采用数字化中频架构的调制解调硬件平台,减小了模拟中频部分的电路规模和设计难度,采用模块化设计,便于各部件升级维护。在保证技术指标的前提下,尽量减小设备体积和功耗,从而实现了一个小型化的具有高度灵活性的卫星调制解调器开发平台。

1 总体设计

调制解调器是一种全双工通信设备,包含调制器和解调器2个相互独立的功能单元。为满足某型卫星通信便携站的设计使用需求,采用数字化中频架构的硬件方案,通过采用大规模FPGA芯片及高集成度的模拟器件使得硬件平台体积这一重要指标符合整机要求。

软件采用重加载方式完成多种通信模式的灵活实现。在FPGA中对中频采样后数据完成解调前的数据预处理。通过设计传输帧结构的方式解决应用低密度奇偶校验码(Low Density Parity Check,LDPC)编译码时的低门限解调问题。

设备的软硬件设计均充分考虑通用化、模块化和标准化的“三化”要求。

1.1 硬件设计

对中低数据速率调制解调而言,传统设计方案多采用零中频调制解调技术。其调制解调均使用模拟电路器件实现,优点是基带部分算法实现简单,实现时所需的FPGA资源较少,对FPGA容量要求较低。缺点是中频电路复杂,中频模块的体积与功耗均较大,同时其杂散、相位噪声和载漏等指标不易调整。零中频方案中频模块的调试需要基带调制解调单元板卡提供测试输入信号来配合,不利于设备批量生产。

软件无线电技术的快速发展以及电子元器件性能和集成度水平的迅猛发展为数字化中频方案的实施提供了较好的基础。

基于数字化中频技术的调制解调器实现方案构成框图如图1所示。

图1 数字化中频调制解调器

由图1可见,经由接口转换后的数据经过信道编码后再送至中频调制模块,直接调制到中频频率f1,中频调制模块包含星座映射、基带数字成形滤波器和数字重采样模块等处理单元。频率为f1的信号再经由变频模块变换至需要的频率范围。在接收端,中频输入信号首先经由变频模块变换至固定频率f2,在f2频率直接进行中频采样,采样后数字信号在FPGA内进行后续处理。其中预处理模块包含数字下变频、自动增益控制(AGC)、数字重采样和匹配滤波等处理。基带解调算法(定时恢复、载波恢复)和信道译码等处理与零中频方案类似。

该数字化中频调制解调硬件实现方案主要优点有:

①可靠性、一致性好。中频采样使得中频单元只需要进行变频处理。数字化处理不需要模拟器件在中频上进行正交调制解调,有效避免了模拟器件不一致带来的正交两路信号幅度不平衡的问题。

②集成度、灵活性高。中频模块减少了正交调制解调电路后,体积大幅缩减。信号处理完全由高集成度的FPGA实现,针对不同传输体制,实现算法可以进行灵活配置。同时便于系统更新升级。

③模块化设计便于测试生产。中频变频模块为独立处理模块。输入输出指标易于测试,基带调制解调电路与中频变频模块可以单独调试。有利于硬件故障的分离及大规模批量生产。

1.2 软件设计

软件设计首要问题是解决软件架构的设计问题。

以调制解调器中常用的编译码为例,其编译码方式包括卷积编码、维特比(Viterbi)译码、里德-所罗门(Reed-Solomon,RS)编码和LDPC等。各种编码方式中LDPC占用的FPGA资源最多,其次为卷积编码Viterbi译码、RS编译码。当设计要求同时具备上述3种编码功能时,将3种编译方式同时在单片FPGA中实现时会出现芯片逻辑资源不够用的情况。

配合LDPC使用的低门限解调算法与配合RS编译码使用的解调程序也不相同,整合这2套解调程序在单片FPGA中实现时也会出现芯片逻辑资源不够用的情况。这时采用重加载的方式可以较好地解决该问题。

重加载是指设备根据监控设置参数不同而自动加载相应FPGA程序的过程。重加载时的不同程序可以并行设计和调试,程序之间不会互相影响。应用程序重装载技术时需重点解决不同模式切换时的监控控制问题。由一种模式切换到另外一种模式时,程序重加载完成后,速率、频率、编码和调制等参数均为未接收命令的初始状态。解决方法为设计监控协议的帧结构,使得监控单元可以检测到各个单元的命令参数接收情况,当检测到程序重加载后自动重置相应的参数。

2 需解决的问题

在应用数字化中频方案后,ADC和DAC芯片均工作于较高的时钟频率,DAC的工作时钟频率可能会达到800 MHz。时钟信号的质量直接影响整机的杂散和相位噪声等中频指标和误码率指标。考虑到某些应用时收发中频信号需外馈10 MHz时钟信号,还需设计专门的时钟分路电路。解决高质量时钟设计问题是数字化中频方案实施的重要前提。

中频采样技术为数字化中频方案的关键技术之一。中频采样技术的性能会直接影响解调器的误码率指标。

在卫星通信中,降低解调门限具有重要的意义。卫星通信中采用低门限解调技术和LDPC等高效编码技术后,不但可以采用高阶调制提高卫星转发器的带宽利用率、增加链路余量以提高传输链路的抗干扰能力,还可以在传输速率一定的情况下,支持更小的用户站型,提高站型的机动能力。LDPC能够在极低Eb/N0值情况下实现准无误码的性能。这就要求解调器必须在低信噪比条件下捕获和跟踪信号,这对解调器的解调同步设计提出了严峻的挑战。

3 关键技术

3.1 时钟设计

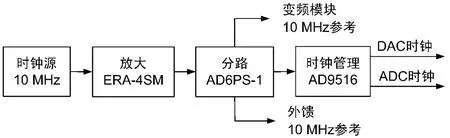

对时钟设计可分为10 MHz源设计、采样时钟电路设计和采用时钟频率设计3个方面。时钟电路设计框图如图2所示。

图2 时钟电路设计

10 MHz源设计时器件选择恒温晶振,时钟稳定度要求优于2×10-8。10 MHz信号经过先放大后分路后分别为时钟管理芯片和变频模块提供参考时钟源,分路后的时钟信号可为 L或者 S频段外馈10 MHz时钟信号。对时钟的放大电路需格外谨慎,通过采取合理设计并切割PCB的电源层和地层,在放大器周围布置耦合接地过孔等措施避免放大器自激。

由于直接进行中频采样,ADC和DAC的采样时钟频率均较高,采样时钟的性能对解调器影响较大。时钟抖动和相位噪声的恶化会引起整个ADC的信噪比的下降。该方案选用稳定度较高的时钟源配合专用时钟管理芯片来产生驱动ADC和DAC的采样时钟。所选的AD9516时钟管理芯片可以提供多路低抖动、低相位噪声的时钟信号。

时钟设计的架构确定后,通过配置时钟管理芯片可以分别调整DAC和ADC的采样时钟频率。确定采样时钟频率后即可确定f1和f2的具体数值。为了保证设备整体的性能指标达到设计要求,例如要求输出杂散优于-50 dBc/4kHz,必须保证在f1频率的信号杂散优于-50 dBc/4kHz并留有一定裕量。f1和f2频率的选择还需要与变频模块统筹考虑,以70 MHz设备的发送端为例,确定输入频率f1和输出的频率范围52~88 MHz后即可确定变频模块的本振频率范围,这时需要计算并确保其7次以内的组合频率干扰落在带外。

3.2 中频采样技术

中频采样技术除了使得设备中频模块体积大幅缩小外,突出优点还包括可灵活对信号进行处理。可对36 MHz带宽进行中频采样,采样后的数据在FPGA内部可对36 MHz带宽内的多个载波信号同时并行处理。

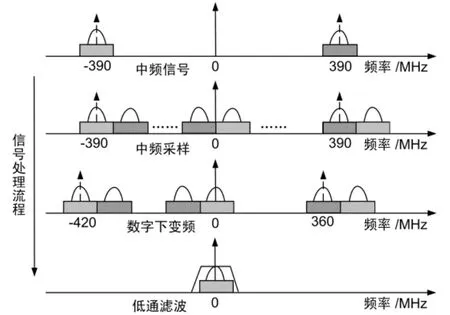

解调器f2为390 MHz时中频采样处理的信号处理原理框图如图2所示。

图3中采样时钟固定为120 MHz,中频采样后的信号经过数字下变频和低通滤波后,变换至零中频。之后需要使用数字重采样技术实现固定的ADC采样时钟和随符号率变化的符号时钟2个时钟域的数据转换。转换后数据的定时恢复和载波恢复等后续信号处理与零中频方案处理方式类似。在调制端同样会用到数字重采样技术。通过合理设计内插同步环路的参数及内插处理精度可以将数字重采样误差对系统的影响控制在允许的范围内。

图3 中频采样实现

总体上看,数字化中频方案是以适当提高软件复杂度为代价大幅降低硬件复杂度。不同性能的数字重采样算法占用的FPGA资源情况不同,串行架构的重采样算法占用FPGA逻辑资源较少,同时能达到的吞吐率也较低,并行架构的重采样算法吞吐率大幅提高但占用的FPGA逻辑资源较多。应用中需要结合具体指标要求在系统性能和硬件资源开销之间进行平衡。

3.3 低门限解调技术

在LDPC性能所决定的低信噪比情况下,载波的直接捕获和跟踪会变得非常困难(相位检测增益变得很小),因此一般采用辅助捕获跟踪的技术手段达到可接受的解调器性能。如DVB-S2规范中为解决8PSK在低信噪比情况下的相位检测增加了一个特殊符号来帮助解调器捕获和跟踪。这种方式使调制器和解调器的设计上都会变得复杂。采用高阶调制方式时,需要通过设计辅助捕获跟踪手段及改进解调捕获跟踪算法来解决低门限解调问题。

在该方案中采用串行导频辅助的方式来解决低门限的解调问题。传输帧结构中插入串行导频会导致符号速率的变化,因此会增加硬件实现的复杂度(主要是时钟处理部分)。该方案在设计串行导频的帧结构时综合考虑了下列原则:

①由于插入信息造成符号速率变化的比率便于时钟锁相环的设计;

②对不同调制方式,帧格式通用;

③插入的导频信息可用于快速傅里叶变换(FFT)频率校正和载波环路跟踪;

④设计的帧结构考虑一定的可扩展性;

⑤由于插入组帧信息带来的性能损失控制到0.3 dB以内。

4 性能测试结果分析

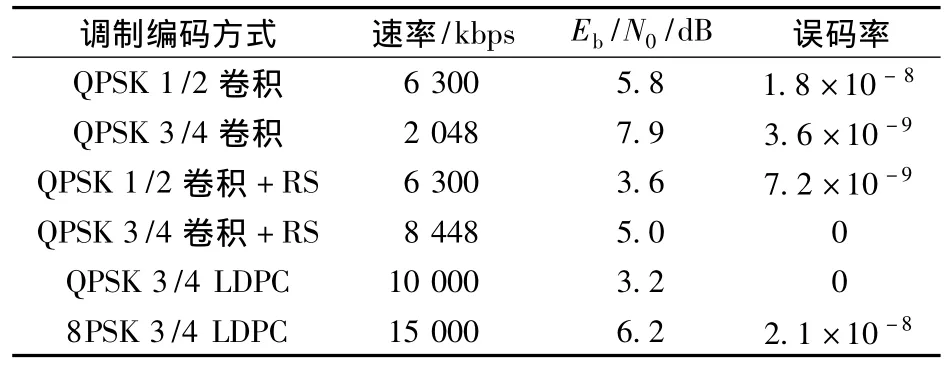

应用该数字化中频方案的调制解调器模块尺寸为宽16 cm,长23 cm,重量小于0.6 kg,功耗小于20 W。该模块支持卷积编码、RS编译码和LDPC等编译码方式。经过测试典型参数下的误码率测试结果如表1所示。

表1 典型参数下误码率测试结果

与零中频实现方案相比,数字化中频实现方案体积大幅缩小,同时重量、功耗等指标也都较适合高度集成化的使用要求。测试结果表明其各种模式下误码率性能均满足设备指标要求。

5 结束语

上述数字化中频调制解调器硬件设计较零中频方案大幅简化。中频采样使得多路载波同时处理成为可能,大规模FPGA的应用也为更灵活有效的算法实现提供了硬件基础。该方案另一突出优势在于其性能一致性较好,后期调试工作量较小更适合批量生产。

采用该方案设计的L频段调制解调器模块已经成功应用于某型卫星通信便携站的研制,有效降低了便携站的体积与重量。 ■

[1]杨小牛,楼才义.软件无线电原理与应用[M].北京:电子工业出版社,2001:115-121.

[2]塔特尔比.软件无线电技术与实现[M].北京:电子工业出版社,2004:46-57.

[3]吴继华,王 诚.ALTERA FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2005:21-22.

[4]张丽娜,潘申富.数字重采样误差对解调性能的影响分析[J].无线电工程,2011,41(2):19 -20.

[5]CORP A.Cyclone III Device Handbook[M].USA:Altera Corp.,2008:224 -226.

[6]陈敬乔,潘申富.低信噪比环境下QPSK调制解调器的设计[J].无线电工程,2007,37(1):51-52.