一种数字无线收发系统设计

方 勉,文继国

(成都信息工程学院 电子工程学院,四川 成都 610225)

由于无线信息传输有着方便、低成本等诸多优点,近年来各种无线通信系统逐渐成为通信市场和研究的热点,其中具有数字中频的无线通信系统因为结构开放,易于升级等特点,成为了热点中的热点。无线收发系统中,采用可编程数字芯片,把模拟电路简单化,成为现在的主流趋势。数字滤波器、DDC、DDS广泛的应用于无线收发系统中。该无线收发系统中,调制与解调算法并不复杂,所以不需要DSP进行算法处理,只采用FPGA进行数字频率合成与数字解调。不仅使得电路设计简单化,同时可以节约成本。

1 系统硬件结构

无线收发系统由两部分组成:发射机和接收机。发射机将频率较低的信号通过上变频、滤波、放大等操作,得到具有一定功率的信号,发射到自由空间并较好地传播。接收机的主要功能是从空间中接收到微弱的信号,放大后下变频到中频或基带由解调器解调,实现中频频信号到基带信号的转换。

1.1 发射机系统结构

射频发射系统的构架一般来说主要有两种拓扑结构,一种是调试和上变频集成在一起的直接上变频结构;另一种是调制和混频两个步骤分离的两级结构,这种结构先进行调制再通过混频器频谱搬移到载波频率。两级结构因为发射频率和本振频率相隔较远,通过混频器后的滤波器可以很好地隔离反射信号,保证了本振信号的纯净,虽然与直接上变频相比较,两级结构会产生其他频率信号,但是由于与所需要的信号相隔较远,依靠滤波器也可以比较容易的滤除。该发射系统采用两级结构,将采集到的外部语音信号(模拟或数字信号)通过ADC输入到FPGA内部,进行FM调制后由DAC输出携带语音信息的10.7 MHz中频信号,将10.7 MHz中频信号与本振信号混频产生433 M的射频信号,再经过放大器模块,得到具有一定功率的信号(500 mW)并有效发射。主要由A/D、D/A转换,FPGA数字中频,滤波器模块、混频器模块、放大器模块和天线组成。

图1 发射系统结构框图Fig.1 Structure diagram of the wireless transmission system

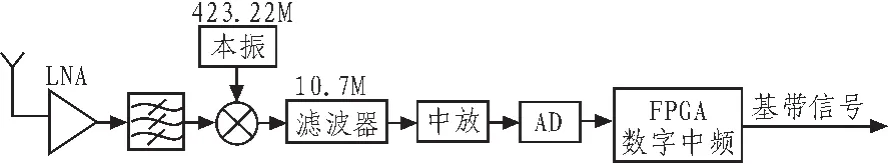

1.2 接收机系统结构

接收机采用低中频接收机结构[1],低中频接收机(Low IF Receivers)是从零中频接收机发展而来的。射频信号经过正交下变频,经过低通滤波器输出两路低中频的I/Q信号,如果所需信号为高边带,则将Q路信号90°移相相加后即可得到高边信号,抑制低边镜像;反之,若所需信号为低边带,则I路信号-90°移相后与Q路信号相加或I路信号90°移相后与Q路信号相减后得到低边带信号,抑制高边镜像[5]。由于下变频后信号不再处于基带,这样就消除了直流偏移和散射噪声的影响。天线将接收到得433.9 MHz的信号经过低噪声放大器(LNA)放大后,通过433 MHz声表面滤波器(SAW),选出所需信号并抑制镜像信号,然后经过混频器下变频,得到10.7 MHz中频信号,经过中频滤波器进入带自动增益控制(AGC)的中频放大器,得到功率要求足够的中频,通过模数转换(ADC),进入FPGA中频处理器进行解调,输出基带信号。

图2 接收系统结构框图Fig.2 Structure diagram of the wireless receiver system

2 系统电路设计

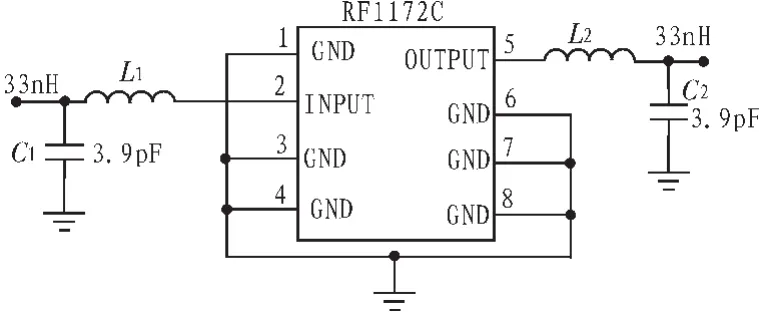

2.1 滤波器

系统所需滤波器,一种是10.7 MHz带通滤波器,此滤波器使用陶瓷晶体滤波器可以达到要求;另一种是在低噪声放大器和混频器后滤除若干不需要的信号带通滤波器,混频后产生的频率除了需要的433 M信号外,还有本振信号、412.52 MHz镜像频率以及其他交调信号和杂散信号等不需要的信号。由于频率很接近,滤波器要具体好的频率选择性,声表面滤波器具有优良的频率选择性、传输损耗小、EMI性能好、可靠性高等特点,RF1172C一款低损耗经济声表面波(SAW)滤波器,专为需要选择433.92 MHz频率的 10.7 MHz中频无线系统设计,外部匹配电路简单。通过smith圆图匹配输入输出阻抗,可达到系统要求。

图3 SAW滤波器电路图Fig.3 Circuit diagram of SAW filter

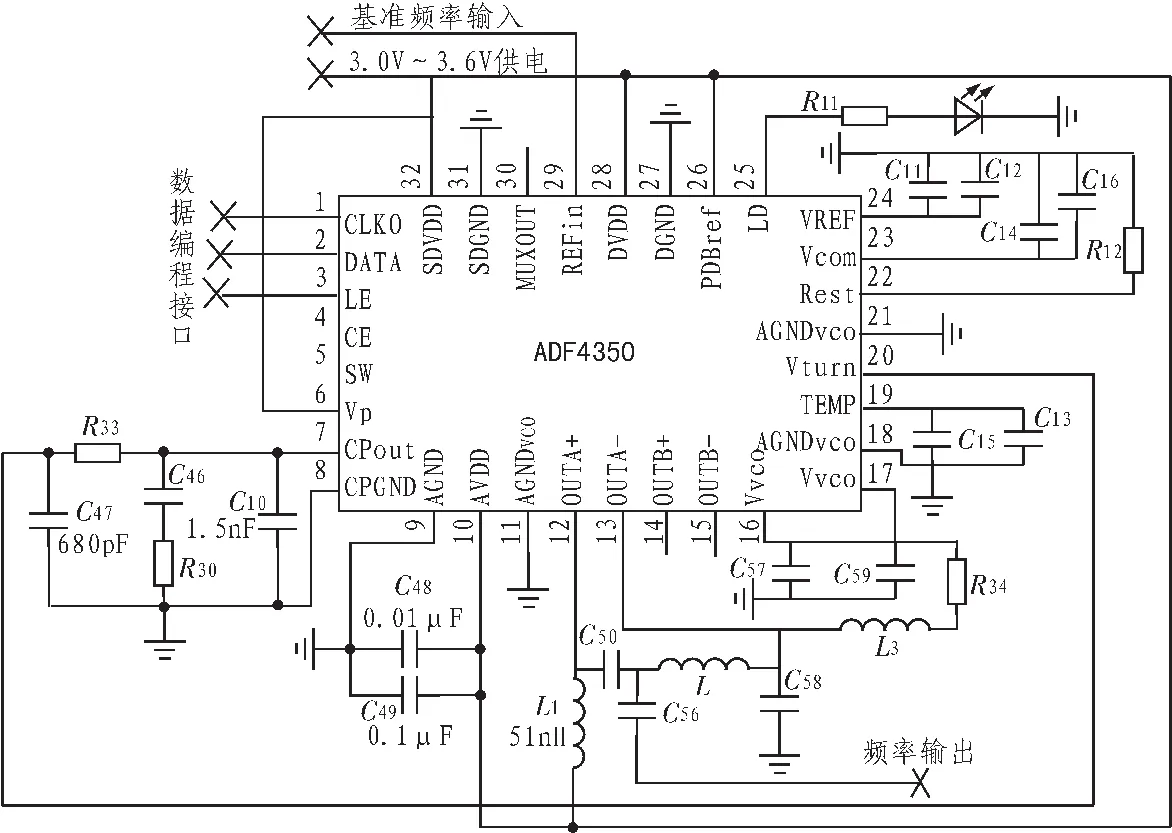

2.2 本 振

收发系统中频率源为混频器提供本振信号,要求频率源输出频率稳定度高。ADF4350是ADI公司的集成VCO(压控振荡器)宽带频率合成器,输出频率范围137.5~4 400 MHz。ADF4350需结合外部参考源以及环路滤波器使用,可实现小数N分频或整数N分频。片内寄存器均通过简单的三线借口进行控制。参考源频率由16 M晶振提供,选择合适的分频参数,通过单片机对寄存器进行操作,ADS软件进行环路滤波器仿真后得到422.2 M的本振频率。电路图如图4所示。

图4 ADF4350电路结构图Fig.4 Circuit diagram of ADF4350

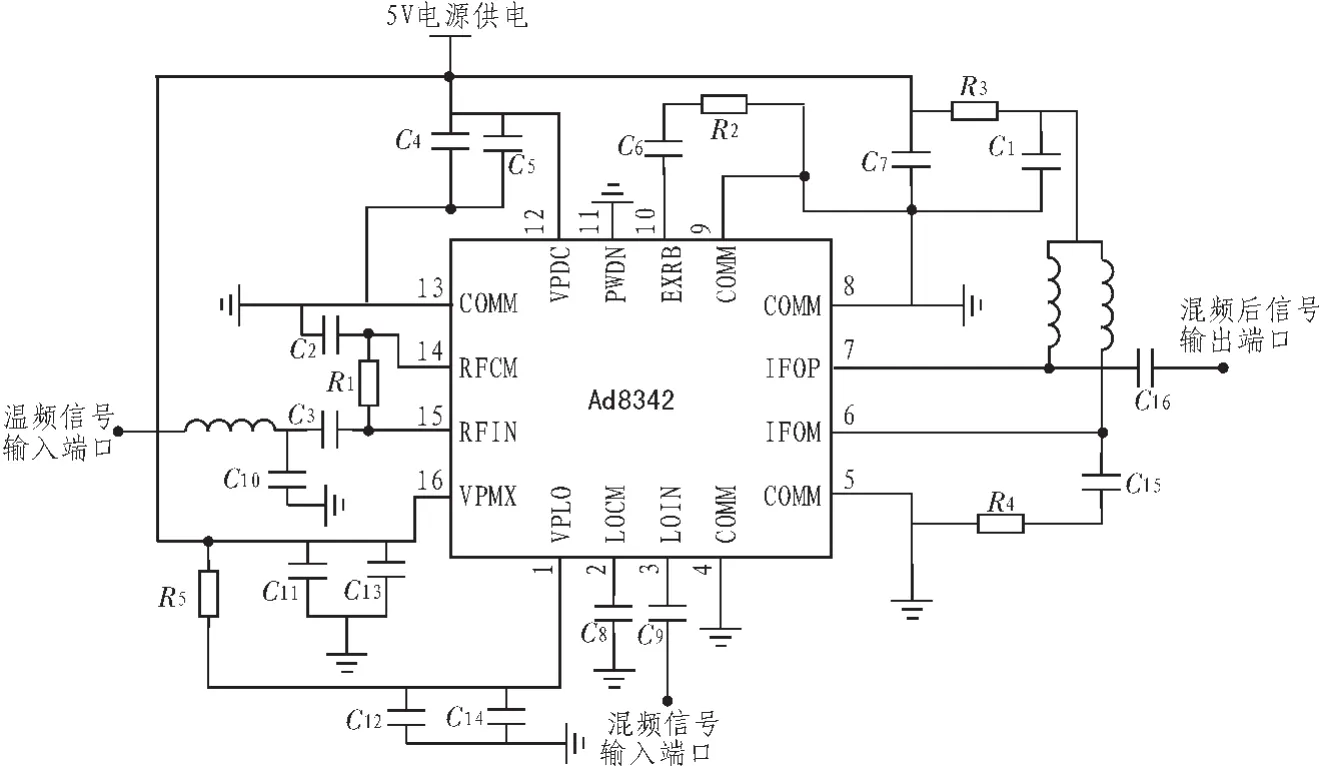

2.3 混频器

输出信号频率等于两输入信号频率之和、差或为两者其他组合的电路。ADI公司生产的AD8342芯片是一款集成有源宽带混频芯片,各个信号端口的输入输出频率范围都能够达到LF-3 GHz,中频(IF)端为差分输出,单端阻抗为 50 Ω,电路图如图5所示。

2.4 放大器模块

图5 混频器电路结构图Fig.5 Circuit diagram of mixture

在发射系统中,在混频器经过滤波后的放大器,将混频器输出的功率较小的433.92 MHz信号放大到适当功率,使后面的功放工作在最佳状态。输出功率的设计指标(500 mW)末级功放需要首先被确定,末级功放使用了高线性度的中功率功放AH102,增益约为12 dB,输出功率27 dBm,而混频器的输出功率约为0 dBm,所以放大器的增益要求要高于15 dB,输出1 dB压缩点高于15 dBm,才能保证输出功率。SGA-4586是RFMD生产的一款HBT可级联增益组件,其工作频率范围为DC-4000 MH。工作在433 M时,增益大于25 dB,放大器内部已为输入输出端口做了50 Ω匹配,外围只要连接必要的供电电路、RFC电路、隔直电路即可正常工作。另一个是射频功率放大器 (RFPA),经过前级SGA-4586放大器放大后,再输入到末级功率放大器,获得足够的射频功率以后,才能馈送到天线上辐射出去。设计中要求末级输出功率要达到500 mW,所以功放的选择要选择最大输出功率大于500 mW,即OP-1 dB要大于27 dBm,工作频率覆盖433.92 MHz,增益足够大的芯片。AH102的工作频段为350~3 000 MHz,供电电压为8.5 V时,电流大小为260 mA,功率2.21 W,此时输出功率537 mW(27.3 dBm),所以功放热损耗为1.67 W,功放模块必须加装散热片,保证功放芯片的温度不至于过高。

在接收系统中的低噪声放大器(LNA),一种位于放大链路输入端,针对给定的增益要求,引入尽可能小的内部噪声,并在输出端得到最大可能的信噪比而设计的放大器。接收机接入的LNA是为了对天线接收的微弱信号进行放大,再对信号做相应的处理。SPF-5043是RFMD公司生产的高性能晶体管单片微波集成电路低噪声放大器,应用频率50~4 000 MHz。当工作在433 M时,增益大于18 dB。噪声系数低于0.8 dB。输入输出端口皆有内部匹配,接上耦合电容即可。

3 数字中频处理器

与传统的超外差接收机相比,数字中频结构,在发送端,基带信号经过内插、滤波,I/Q调制后,进行D/A变换,变成中频模拟信号。在接收端ADC直接对中频信号进行采样,采样后由数字下变频进行I/Q解调、抽取、滤波、然后送往基带处理。

3.1 FM调制

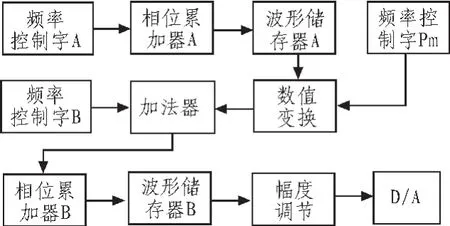

如图6所示为FM信号发生器在FPGA中的实现框图[2],频率控制字A控制调制信号频率,B控制载波中心频率。相位累加器由加法器和寄存器组成,总的调制原理就是,周期变化的调制信号作用于控制载波频率的相位累加器B原本固定的步长,是总的步长产生周期性变化,从而实现载波频率在中心频率附近的周期变化,得到FM 信号。表达式:y(t)=sin[(2πPfclk/2N)(Δ+2NPmsinωt/2πPfclk)]t,其中 fclk为输入时钟频率,锁相环频率系数为P,计数器位数N。只需要把产生信号频率为 fc的基础上把步长 Δ 改变为 Δ+2NPmsinωt/2πPfclk,把2NPmsinωt/2πPfclk整体进行查表处理,同时频偏控制字Pm的计算,Pm=2π×Δ fmax,其中 Δ fmax为允许的最大频偏。

图6 FM调制框图Fig.6 Structure diagram of FM

3.2 FM解调

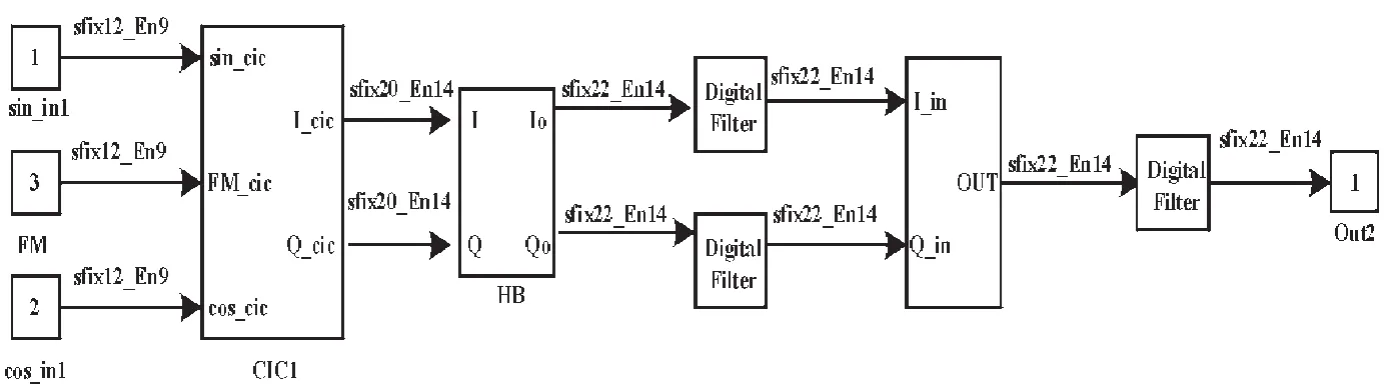

在接收端,对中频信号采用正交解调[3]和欠抽样[4],将AD采集信号同步化,然后分别与数控振荡器(NOC)产生的正、余弦同频信号相乘,即为数字下变频模块,通过后级数字滤波器滤除相乘后的高频的分量滤除,得到搬运后的信号。根据软件无线电的流程、正交解调与通带采样原理[2],可在MATLAB下的SIMULINK中搭建模型进行接收机的原理性仿真,模型如图7所示。

正交解调模型在FM_QIDECODER_10.7M中,如图8所示,在模型中,通过FM Modulator Passband产生中心频率为10.7 MHz,频偏为75 kHz的调制信号,经过采样率转换后,信号传输给解调模块进行解调。FM_DECODER模块中先和产生的正弦余弦信号混频,产生IQ两路信号,然后通过梳状滤波器(CIC),半带滤波器(HB),以及 FIR低通滤波器,最后通过鉴频模块后,进入后级滤波器输出解调信号。

图7 接收机SIMULINK模型Fig.7 SIMULINK model of receiver

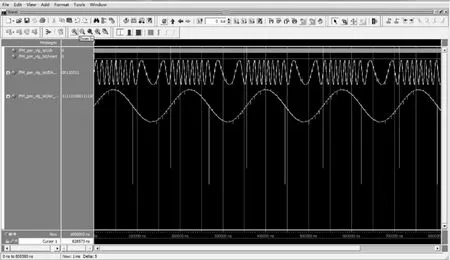

编写整个接收机程序后,通过QUARTUS II产生仿真文件,并使用modeslim进行功能性仿真,结果如图 9,clk为系统时钟,reset为复位引脚,DA_data为调制波信号,sin_data为原信号。 其中 fc=100 kHz, Δfmax=75 kHz, fin=10 kHz,由图可见波形符合理论研究,满足设计要求。

3.3 中频数字软件处理

图8 正交解调模型Fig.8 Model of quadrature demodulation

图9 发射机FM调制波形Fig.9 FM modulation waveform of transmitter

无线收发系统的程序采用Verilog HDL编写,顶层文件用BDF原理图,文件直观的表示出来。发射机程序软件系统中,由按键选择原信号为外部AD信号,或者是内部ROM表产生。当由内部ROM表产生时,即用上述相位累加器原理,在 ROM 表中存储 sin(2πfoutt)*1 000*228/160 000 000(输入时钟频率为160 M,锁相环频率系数为1,计数器位数为28)产生频率为fout=fclk/2N的原信号,然后与频偏fmax/1 000相乘,在通过加法器与载波中心频率控制字相加,得调制波的控制字,然后通过相位累加器,产生调制波信号,通过DA输出。当由串行16位AD采集外部音频信号时,舍去数据低四位只保留12位数据,乘上小数0.8,再与频偏fmax/1 000相乘,与载波中心频率控制字相加,得到调制波控制字,通过相位累加器产生调制波信号,通过DA输出。

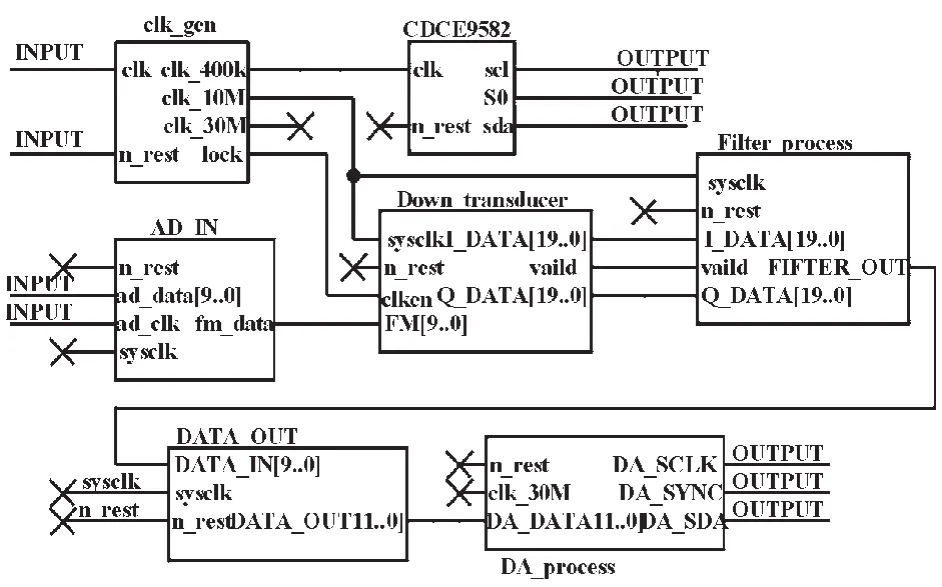

在接收机程序软件系统中,通过FIFO将AD采集信号同步化,然后分别与NOC产生的正、余弦同频信号相乘,即为数字下变频模块,通过后级数字滤波器滤波,将相乘后的高频分量滤除,得到搬运后的信号。由于采样率为10 MHz,因此必须在滤波器中加入抽取部分,采用3级滤波。为保证频谱在抽取后不发生频率混叠,采样率抽取后必须大于两倍信号带宽,即4倍频偏,FM信号最大频偏为75 kHz,因此最多抽取20倍。在程序中先由5阶CIC滤波器5倍抽取,得到2 MHz的采样信号,再由10阶HB滤波器2倍抽取,得到1 MHz采样信号,由于HB滤波器在通带有相应的损耗,所以后级加入一级FIR滤波器,进行补偿。最后采用15阶FIR低通滤波器进行2倍抽取,得到500 kHz的采样信号后,送入鉴频模块,得到原信号。 原信号为音频信号,采样率最多只有20 kHz,500 kHz的采样率依然可以进行抽样。在后级DATA_OUT模块中,通过一级CIC滤波器和两级FIR滤波器,最后将信号还原,送入DA输出。

图10 发射机BDF原理图Fig.10 Transmitter BDF functional diagram

采用CDCE925模块为AD,DA的外部时钟驱动芯片的驱动程序,采用IIC协议编写。DA_process为外部音频时钟的程序驱动,其余模块按照上述原理性框图编写

在硬件实现上,主控芯片采用ALTERA公司的EP3C10E144T,晶振采用20M有源晶振,串行AD采用音频ADTLC4541,串行DA采用DAC7513,使用 DAC902E输出中频信号,AD9215采集中频信号。考虑到FPGA管脚输出的时钟抖动过大,因此采用CDCE925可编程时钟合成器给高速AD/DA提供时钟。经试验发射机的频率分辨率为0.596 Hz,接收机的中频采样频率为10.7 MHz。

4 结 论

该设计采用FPGA作为数字中频处理器,搭建收发系统,对原理及软硬件实现方法进行了简要说明。经测试表明,系统简单可靠,收发效果好。其中使用FPGA数字中频处理部分,在发射机和接收机上都体现了其方便高效的特点,具有广泛的应用。

图11 接收机BDF原理图Fig.11 Receiver BDF functional diagram

[1]Mirabbasi S,Martin K.Classical and modern receiver architectures[J].IEEE Communications Magazine,2000,38(11):132-139.

[2]戈立军,吴红,司敏山.基于DDS技术的FM信号发生器的设计及其FPGA实现[J].南开大学学报,2007,40(6):95-99.

GE Li-jun,WU Hong,SI Min-shan.Design of FM signal generator based on DDS technique and implementation with FPGA [J]. Acta Scientiarum Naturallum:Universitatis Nakaiensis,2007,40(6):95-99.

[3]祝林啸,吴嗣亮.一种调频信号数字正交解调方法[J].电讯技术,2005(4):120-123.

ZHU Lin-xiao,WU Si-liang.A digital quadrature demodulation method for FM signals[J].Telecommunication Engineering,2005(4):120-123.

[4]蒋华,王书相.带通欠采样定理在软件无线电中的应用[J].西安科技大学学报,2004,24(4):492-495.

JIANG Hua,WANG Shu-xiang.Application of bandpass undersampling principle in software radio[J].Journal of Xi’an University of Science and Technology,2004,24(4):492-495.

[5]张泽,吴嗣亮,王旭.列控系统多音频信号的全数字解调方法[J].军民两用技术与产品,2004(4):46-48.

ZHANG Ze,WU Si-liang,WANG Xu. FM wave demodulation for train control system using digital method[J].Dual Use Technologies&Products,2004(4):46-48.

[6]Pozar D M.Microwave Engineering.[M].Third Edition.北京:电子工业出版社,2011.

[7]杨小牛.软件无线电原理及应用[M].北京:电子工业出版社,2001.