基于AXI总线的DMA 控制器的设计与实现

蒲 杰,李贵勇

(重庆邮电大学,重庆 400065)

0 引言

直接内存存取(direct memory access,DMA)是一种快速传输数据的机制,数据存取时不需要经过处理器进行干预,数据直接在源地址和目的地址之间进行传输,从而提高数据传输速率。DMA控制器是片上系统 (system on a chip,SoC)中重要的组成部分。本文通过分析高级扩展接口(advanced extensible interface,AXI)总线协议,利用 Verilog HDL实现了符合该规范的DMA控制器IP核,并在SMIC(中芯国际)65 nm标准单元工艺库下对模型进行了综合和优化。

1 AXI总线简介

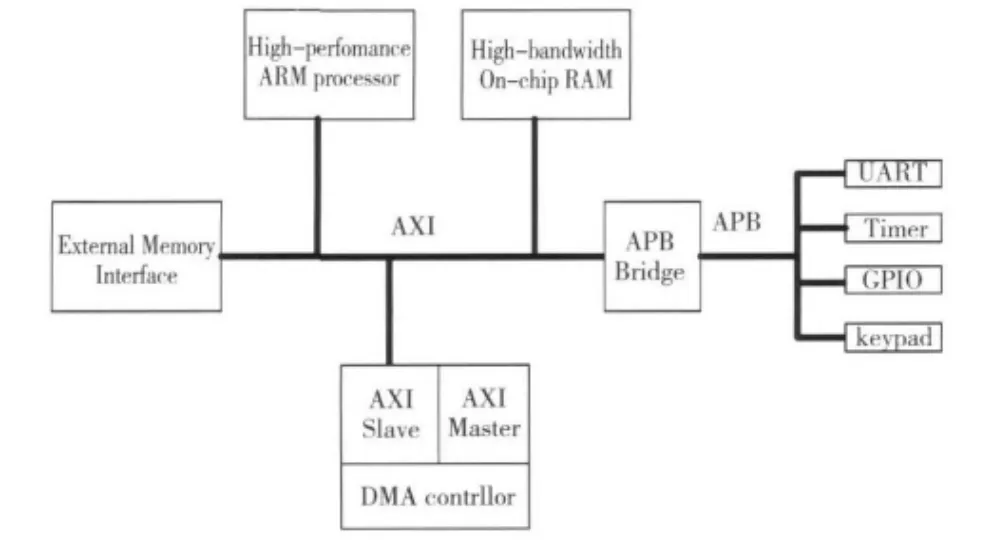

目前有很多种总线规范,其中,由ARM Limited公司推出的高级微控制器总线架构(advanced micro-controller bus architecture,AMBA)on-chip bus 片上总线规范,是芯片总线的主流标准。AXI总线协议是AMBA3.0协议中最重要的部分,是一种面向高性能、高带宽、低延时的片内总线,并且能够后向兼容现存的高级高速总线(advanced high performance bus,AHB)和高级外围总线(advanced peripheral bus,APB)接口,其关键特征为分离的地址、控制和数据通道,采用字节选通的方式支持不对齐数据的传输,基于burst transaction的数据传输,主机只需提供首地址,分离的读写数据通道,能支持低功耗的DMA,支持outstanding transaction,支持乱序 transaction,易于通过添加寄存器达到时序收敛[1]。典型的AMBA架构的片上系统如图1所示。AXI由Master,Slave和Infrastructure 3部分组成。当DMAC进行数据传输时,它作为AXI总线上的一个MASTER;当对DMAC进行配置时,它作为AXI总线上的一个Slave。

图1 典型的AMBA架构Fig.1 Typical AMBA architecture

2 DMA控制器设计与实现

DMA设计方法遵从AMBA AXI的64位AXI系统总线,传输速度快,效率高,可以广泛应用于ASIC设计中。本文提出的DMA控制器的工作原理如下:首先,ARM对DMAC的配置寄存器做初始化操作,将配置信息写入 DMAC中;然后,DMAC根据DMA请求信号做出适当的反应,若要进行数据传输,则按照之前的配置进行;最后,在数据传输完毕后,DMAC发出中断信号,释放AXI总线。

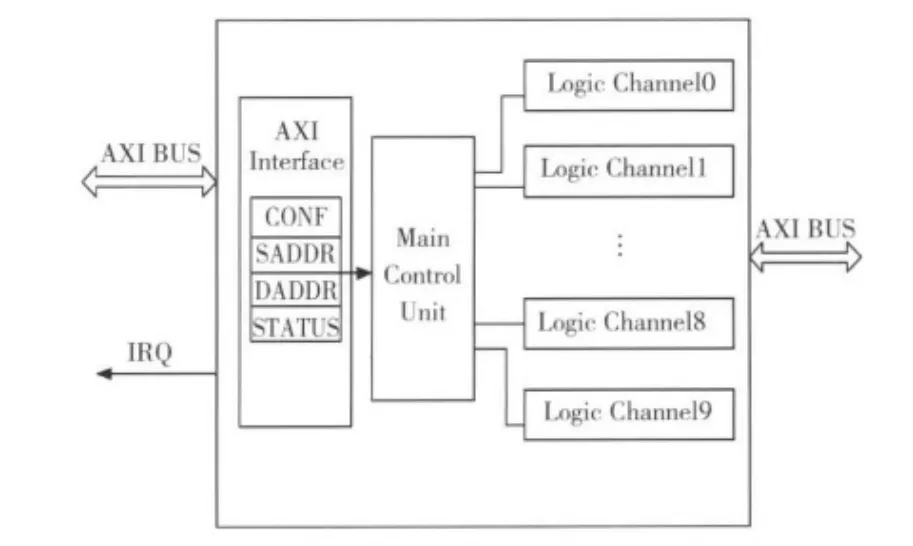

在接口单元的设计上,出于对DMAC功能的考虑,本设计由AXI slave接口单元、逻辑通信控制单元、DMA请求响应单元,中断请求单元[2]、AXImaster单元等几部分组成。其结构如图2所示。

2.1 AXI slave接口单元

图2 DMA控制器功能结构图Fig.2 Structure of DMAC

AXI slave接口模块(AXI Interface)实现DMAC与ARM的AXI总线相连,DMA控制器作为一个slave挂在AXI总线上[3]。通过该模块,ARM 可以对相应寄存器进行读写,从而实现对配置寄存器的初始化。其中,包括各通道的配置寄存器、延迟寄存器、中断分配寄存器、源地址寄存器、目的地址寄存器、数据长度寄存器、周期传输长度寄存器和状态寄存器。其读写时序按照AXI总线读写时序。在本设计中,共有10个逻辑通道,10个通道分别采用不同的配置寄存器来进行初始化操作。

2.2 逻辑通道控制单元

逻辑通道控制单元的寄存器同样通过slave接口单元来进行初始化设置操作。其中,包括的寄存器有:源地址寄存器、目的地址寄存器、延迟寄存器、传输总长度寄存器、周期长度寄存器、通道中断状态寄存器。

DMAC在数据传输前,将源地址和目的地址写入配置寄存器中,在普通传输的过程中不能改变这2个寄存器的值;若采用中断传输方式,且源地址和目的地址不固定,则在每个周期长度数据传输完毕后会更新这2个寄存器的值。

延迟寄存器用于指定相邻2次普通传输之间的延迟,以防止DMAC长期占用总线[4]。

传输总长度寄存器用于指定当前需要传输的数据总数,每完成一个数据的传输,该寄存器的值就执行减1操作,当减到0时,表示当前传输完成。

周期传输长度寄存器用来指示一次传输的数据个数,在中断传输模式中,可设为对方2次中断请求之间所申请传输的数据个数。本设计中的传输支持burst(突发)操作,在实际操作中,一个周期长度可能由很多个 burst长度的数据组成,也可能不是burst的整数倍。

通道中断分配状态寄存器用于在中断传输方式中指示该通道响应哪些中断源的中断请求,只有外部中断请求与寄存器的值相同时才进行数据通道分配。

通道状态寄存器用来指示当前的传输是否完成,是否有错,本通道是否处于传输状态。

2.3 DMAC中断请求单元

在本通道传输完成一个周期长度的数据后,DMAC中断请求单元通知DMA master接口单元释放总线,交还总线控制权,由下一个优先级高的通道来控制总线并进行一个周期长度的数据传输,之后依次轮询。在某个通道完成全部数据传输后,DMAC中断请求单元发出中断给ARM,同时通知DMA master接口单元释放总线。

2.4 DMA请求/响应单元

外设使用DMA请求信号进行一次数据传输请求,DMAC根据适当的优先级算法,决定哪个外设可以进行数据传输,并给出一个响应信号,表示当前的某个外设的初始化完毕并开始进行传输。

2.5 DMAC master接口单元

当DMAC希望执行传输的时候,就必须通过master单元发出对总线的请求信号,当获得arbiter的允许后,DMAC掌控总线,实施数据传输操作。

DMAC在没有工作时,master接口单元处于空闲状态,开始工作后首先由外设发送请求信号并提供地址和数据,随后接口单元向arbiter发送总线请求信号并等待获得批准[5]。一旦获得批准,master接口单元立即进入忙状态,并开始读写操作。由于AXI总线读写通道分开,因此,读写操作可同时进行。对于中断传输模式,当所有通道的数据传输完成后,则释放AXI总线控制权。对于普通传输模式,所有通道完成一个周期长度的数据传输后就释放AXI总线控制权,等待一段时间后,DMA再进行下一周期长度的传输。在数据传输的过程中,每次传输都会检测RESP信号,并根据此信号采取不同的响应。

本设计的DMA共有10个逻辑通道,每个通道都有2种传输方式可选:普通传输和中断触发传输。对于普通传输方式,设置完对应逻辑通道的源地址、目的地址、数据长度寄存器之后,启动配置寄存器的启动位,DMA就发出请求总线信号,得到授权后,就开始读写传输;对于同步中断触发传输方式,配置好寄存器的值,并启动配置寄存器的启动位之后,传输并不立即进行,只有和此逻辑通道配置对应的中断触发到来之后,才完成一次数据长度为周期长度寄存器值的数据传输。本次传输完毕后,更新源地址、目的地址、数据长度寄存器。当数据长度寄存器的值为0之后,本通道就不再响应新的中断触发。在配置寄存器中还设置了一个强制传输选择,若配置了该位,则在外设申请到该通道后,可立即进行一个周期长度的数据传输,传完一个周期长度后,该比特位自动清零,然后再开始等待和该逻辑通道对应的中断触发到来后,再进行下一次周期长度的数据传输。

DMA进行传输时,可以配置为字节(8 bit),半字(16 bit),字(32 bit),双字(64 bit)等数据传输类型,每次数据总线上传输的有效比特位可由wstrb或rstrb决定。此外,本设计的DMAC还支持AXI协议的4种突发传输方式。

3 功能验证与综合

在功能验证和测试时,我们使用ARM公司的RVDS软件进行ARM工程的编译和调试,以及Synopsys公司的VCS软件进行仿真,该软件许可在PC、Linux平台上使用,支持 Verilog硬件描述语言(HDL)仿真。

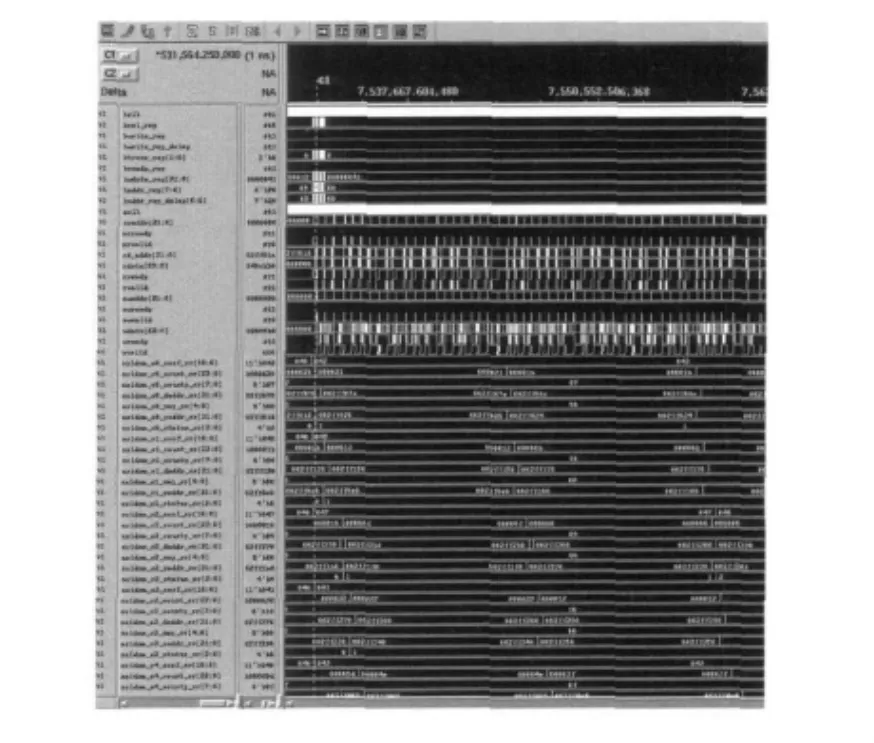

在测试时,将几个带有DMA接口的外设和本AXIDMA控制器连接,每个外设对应不同的中断源[6]。在满足AXI总线的时序后,对各个逻辑通道寄存器进行配置,配置各个通道为中断触发方式,且强制传输。得到的仿真波形如图3所示。

图3 功能仿真图Fig.3 Simulation wave of DMAC

从图3中可以看到,在第一次强制传输后,各个通道在对应的中断到来之后,进行一个周期长度的数据传输。每个逻辑通道在完成一个周期长度的数据传输后,由下一个优先级高的通道占用总线,并进行一次周期长度的数据传输。当某个通道完成全部数据的传输后,该通道释放总线,若要再进行传输,则需对该通道寄存器进行重新配置。

对各种配置进行仿真完毕后,利用目前业界最流行的综合工具——Synopsys公司的Design Compiler[7-8]对其综合。经过对Script脚本约束的设定,通过DC将控制器的时序和面积进行优化,工作频率满足我们的手机基带芯片频率要求。且对比以前的基于AHB总线的DMA控制器设计,其工作频率和总线效率得到了很大了提升。

最后,进行了 FPGA验证,测试结果表明,该DMAC完全符合手机基带芯片的要求。

4 结论

本文探讨了一种基于AXI总线的DMA控制器的实现方法,并结合仿真和综合工具进行寄存器传输级(register transfer level,RTL)级仿真和综合。DMA控制器可以快速的搬移大量数据,减轻了CPU的工作压力,在当今越来越高速的芯片设计中扮演着不可或缺的角色。本文中所提出的方法已经应用于LTE-TD系统基带芯片中,取得了很好的效果。由于是在AMBA总线协议上实现的设计,故可以搬移到很多其他芯片的设计中,得到更为广泛地应用,实现IP复用。

[1]ARM Limited Inc.AMBA AXI Protocol specification,REV1.0[EB/OL].(1999-05-13)[2008-11-18].http//www.arm.com.

[2]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2004:5-176.XIA Yu-wen.Verilog Digital System Design Tutorial[M].Beijing:Beijing University Press,2004:5-176.

[3]OLUGBON A,KHAWAM S,ARSLAN T,et al.AMBA AHB-based reconfigurable SoC architecture using multiplicity of dedicated flyby DMA blocks[C]//Proc of the ASP-DAC.Asia and South Pacific:IEEE Press,2005:1256-1259.

[4]MA Guo-liang,HE Hu.Design and implementation of an advanced DMA controller on AMBA-based SoC[C]//Proc of ASICON'09.IEEE 8th International Conference,ASIC.Changsha,China:IEEE Press,2009:419-422.

[5]唐平.DMA控制器的实现与应用[J].数字通信,2010,2(1):90-93.TANG Ping.Implementation and application of DMA controller based on AHB bus[J].Digital Communication,2010,2(1):90-93.

[6]程野.IIS控制器的ASIC设计与实现[J].重庆邮电大学学报:自然科学版,2009,21(5):584-586.CHENG Ye.ASIC design and implementation of IIS controller[J].Journal of Chongqing University of Posts and Telecommunications:Natural Science Edition,2009,21(5):584-586.

[7]Design Compiler Reference Manual:Constraints and timing[EB/OL].(2007-03-12)[2009-05-20].http://www.ee.bgu.ac.il/~ hadaryan/logic/…/design_compiler_ref.

[8]SYNOPSYS Inc.Design Compiler Reference Manual:Constraints and Timing[EB/OL].[2008-11-18].http://www.synopsys.com/Pages/results.aspx?k=Constraints%20and%20timing%20,2007.