数字ATE上内部示波器的实现

李 杰, 刘林生

(北京自动测试技术研究所, 北京 100088)

0 引言

内部示波器是ATE测试设备上的一个调试工具模块,在大多数进口ATE设备上都配备了这个模块。内部示波器的主要功能就是可以动态地显示ATE被测芯片某个输出管脚的实时波形,它极大丰富了ATE设备的调试手段、降低了测试成本、缩短了编程和调试的周期,是ATE测试设备进入中高端市场必备的一个模块。

1 内部示波器

内部示波器从主要功能上看与我们现在使用的外部示波器没有本质的区别,一些基本的示波器功能它都可以提供。但对于测试工程师来说,在编写测试程序或者调试测试程序时,相对于外部示波器来说,内部示波器的优点是非常明显的。首先,内部示波器相对外部示波器最大的优点在于采样点的不同,外部示波器的采样点一般都在芯片的管脚上,内部示波器的采样点在管脚电路驱动/比较器的输出端,这就决定了内部示波器能更精确地显示输出的波形;其次,外部示波器即使内阻再大在某些情况也是不能被忽视的,这就导致了测试准确度的下降,而内部示波器是不涉及内阻问题的;第三,在某些特殊场合,比如中测的时候,看不到被测的圆片,所以根本没有条件使用外部示波器,这也是内部示波器的优势;综上所述,内部示波器对于中高端ATE设备来说是一个必不可少的模块。

2 内部示波器的实现原理

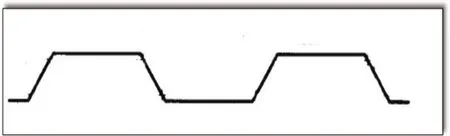

对于数字ATE设备来说,它没有配备波形采集的模块,那要如何实现对被测芯片输出波形的采集呢?我们看图1所示的一个波形,它看起来虽然是连续的,但我们同样可以把它看成是由无数个点组成的,把这些点连起来就成了连续的图形了。而数字ATE设备对输出管脚的输出电压是可以采集到的,所以在一个测试周期内,每间隔一定的时间对输出管脚采集一次输出电压,并把这些采集到的电压值进行作图处理,只要间隔时间足够小,那么最终做出的就是该管脚的连续输出波形了。

图1 典型输出波形

数字ATE设备采集输出管脚电压值有两种常见的方法,一种方法是通过直流参数测试,对输出管脚加流测压测得输出电压值。这种方法显然不适合用于此处,因为直流参数测试加流测压的方法实际上是对输出管脚加入负载的情况下测得的输出电压值,这个电压值是和负载有关的,不能准确地反映输出管脚的波形情况。另一种方法是功能测试得到管脚输出电压值,通过对输出高/低电平比较电压的设置,以及功能测试是否通过来得到管脚输出电压的值。这个电压值是和负载无关的,能够准确地反映输出波形。

3 内部示波器在测试仪上的实现

下面以我所研制的BC3192V50数字集成电路测试系统为例,详细说明内部示波器模块的实现方法以及需要解决的一些技术难点。

首先来看一下如何用功能测试的方法来采集输出管脚的输出电压。对于一个芯片的输出管脚来说,输出波形与功能测试的测试图形是一一对应的,如图2所示,测试图形的每一拍对应输出波形的一个周期,右图所示的波形在测试图形文件上显示的就是“LHLHL”,功能测试实际上就是检验输出管脚的输出状态是否正确。如果在测试图形文件上某输出管脚的内容是“LHLHL”,功能测试又显示“通过”,则可判断该管脚的输出波形如图2所示。ATE上的“H”和“L”是由输出高/低比较电平(VOH/VOL)这两个参数决定的,管脚输出电压大于VOH,ATE判定为“H”状态,小于VOL判定为“L”状态,这就不难看出,如果把VOH和VOL设定为同一个电压值,并且从0V(或者VCC)开始以一个很小的1V递增(或递减),每次都进行功能测试,则在功能测试结果变化的那个点对应的VOH和VOL的电压值就是输出管脚此刻的输出电压值。

图2 典型输出波形详解

通过上面的介绍可以看出,要得出输出电压值,必须在功能测试结果变化的跳变点上才可以,那么问题又出现了,功能测试是对所有输出管脚做判断的,如何才能得到所需输出管脚的功能跳变点呢?常规方法是对功能测试的测试图形做屏蔽处理,也就是说将所有无关输出管脚的测试图形文件内容改为“X”(输出不关心状态),这就保证了只对关心的输出管脚做功能测试。但这种方法既麻烦又费时,还容易产生错误,这里我们采用BC3192测试系统自带的失效存储器来完成这个操作。失效存储器在每次功能测试结束后自动存储,它存储的内容是所有输出管脚功能测试的结果,失效为“1”,通过为“0”,我们要判断某个管脚在测试图形某一拍的功能测试结果,只需读出失效存储器对应位的内容就可以了。图3显示了BC3192失效存储器的内容,该测试图形有8拍,前14拍是流水。

图3 失效存储器内容

通过BC3192测试系统的VOH和VOL电平的设定以及失效存储器内容的读取,我们现在可以采集到输出管脚在时钟周期某一点上的输出电压了,但如何在整个时钟周期的不同点上采集输出电压呢?数字ATE设备上驱动/响应格式化器是必不可少的模块,而响应格式化器的功能之一就是让用户自行决定在一个时钟周期内何时进行功能比较,它一般提供两种比较方——沿比较和窗口比较。窗口比较需要设定一个时间窗口,比如时钟周期100 ns,窗口设定为【60 ns,80 ns】,则功能测试会在【60 ns,80 ns】这个窗口内对输出电平进行比较,只要出现了正确的电平,就判断功能测试通过。而沿比较只需要设定一个比较沿,比如时钟周期100 ns,比较沿设定为80 ns,则功能测试会在80 ns时对输出电平进行比较,80ns时的输出电平正确功能测试才会判断通过。BC3192测试系统响应沿的分辨率为1 ns,所以只需要使用沿比较的方式进行功能测试,每间隔1 ns采集一次输出管脚的输出电压,就可以在整个时钟周期内采集到足够多的输出电压值了。

通过上面的分析,我们使用软件编程,把周期数作为第一循环,采样时间作为第二循环,VOH和VOL电压值作为第三循环,对芯片进行功能测试,把得到的输出电压值作图就可以得到输出波形了。但这并不是实际的波形,它和实际波形还有一定的差距,下面我们来讨论内部示波器实现中的一些难点和波形优化的问题。

首先我们不能忽视的一点是所关心输出管脚的测试图形文件上如果出现了“X”(输出不关心)和“T”(输出三态)这两个状态,在VOH和VOL相等的情况下,功能测试是不会出现跳变点的,这就导致输出电平采集的失败。为了避免这种状态的产生,在电压采集之前,对测试图形文件还要进行一定的处理,将文件中的“X”和“T”状态任意改为“H”或者“L”,以保证功能测试跳变点的出现,从而能顺利地采集到输出电压值。

其次对于内部示波器模块来说,采集时间是个敏感问题,从原理来看,3个循环嵌套,1 ns的分辨率,电压步进值如果也很小的话,整个的采集时间是很长的,如何能优化这个采集时间也是一个难点。要对VOH和VOL电压循环优化,我们可以首先先确定每个时钟周期内输出波形的预期值,这可以通过测试图形文件得到,预期值为低,则循环从VCC开始,预期值为高,则循环从0V开始,这就能有效减少给循环的次数,同时还可以采取半值比较的方法,比如循环从VCC开始,下一个点检测VCC/2,如跳变点没产生,则检测VCC/4,如产生了检测3VCC/4,以此类推,可大大缩短VOH和VOL电压循环的次数,减少采集时间。对采集时间循环的优化可根据测试周期决定,保持该循环最大循环100次较为适宜,也就是说周期大于100 ns的时候,可以相应增加采集时间间隔,保证循环次数不会太大。

对所得到的输出管脚波形进行优化和平滑是必需的,最主要的原因就是该波形存在过冲问题。过冲一般会出现在输出波形变化的时候,也就是波形从低变高或者从高变低的时候,过冲的电压值一般都很高,有可能达到VCC,但它不是真实的,这主要是由采集时间接近0 ns的时候,功能测试结果不稳定造成的。根据这种情况,把采集的前5-10个点进行优化,可以得到比较真实的波形。波形的平滑也是必须的,因为即使是1 ns采集间隔,在作图的时候间隔也是很大的,如果不进行平滑,做出的波形锐度会很大,看起来很不舒服。我们可以通过软件的计算,在两个间隔点之间再取100个点,每个点的增量为间隔的1%,这样再画出的波形就较为真实了。

4 结论

内部示波器 作为一个非常实用的调试模块,越来越受到测试工程师的欢迎,国产设备配备该模块是大势所趋,也必然是国产设备进入中高端市场的必备软件模块。

[1]逄珊.ATE软件系统测试方法研究[J].中国测试,2009,35(1).

[2]叶海明,周绍磊,徐俊彦.通用测试系统模型化技术研究[J].计算机测量与控制,2009,17(9).

[3]申莉,沈士团.通用自动测试系统模型化设计[J].北京航空航天大学学报,2009,35(7).

[4]逄珊.ATE软件系统测试方法研究[J].中国测试,2009,35(1).

[5]成孝刚,刘国庆,姜华.ATE测控平台的研究与应用[J].微计算机信息,2009,25(7).

[6]叶海明,周绍磊,徐俊彦.通用测试系统模型化技术研究[J].计算机测量与控制,2009,17(9).

[7]樊寅逸,何海光.AT45DB081B在数据采集系统中的应用[J].电子元器件应用,2007(3).

[8]岳丽华,韦鹏,钟诚.一种自适应的复合多路flash存储结构[J].中国科学技术大学学报,2008(7).