DSP Builder在软件无线电实验平台的应用

党小宇,朱秋明,陈小敏,陶 静

(南京航空航天大学电子信息工程学院,江苏南京 210016)

0 引言

软件无线电(Software Radio)是一种实现无线通信的新手段和新方法,它的出现使得无线通信的发展经历了由固定到移动,由模拟到数字,由硬件到软件的三次变革。其核心思想是在具有标准化和模块化的通用开放硬件平台上,将无线电通信中的多种功能用软件来实现,并使宽带A/D和D/A转换器尽可能靠近中频或射频天线[1]。

软件无线电的基本概念是由J.Mitola首次在1992年5月美国通信系统会议上提出的[2]。不久美国防部高级研究局(DARPA)便提出了基于软件无线电的“易通话”(Speakeasy)计划。到了21世纪,软件无线电已经从军事领域转向民用领域,成为第三代移动通信的应用基础[3]。

软件无线电传统的开发首先采用Matlab算法仿真验证,再选择主流的 Altera或者Xilinx的硬件平台,编写硬件描述语言,然后综合、实现、生成下载文件并下载到硬件。这一过程需要熟练掌握Matlab语言和硬件描述语言Verilog或者VHDL。

我们在“软件无线电”课程实验教学中感到,有必要开发一套简化通用的开发平台软件。让学生可以在计算机上利用DSP Builder操作平台搭建实验模型,然后进行调试、仿真和下载,并快速完成所需波形的绘制与验证。学生对实验仿真结果与传统开发提供的参考波形标准进行比对,提高了他们的调试能力和对软件无线电理论开发的理解。

1 设计平台的介绍和设计流程

1.1 设计平台介绍

DSP Builder是一个连接系统级(SL)和寄存器传输级(RTL)两个层面的设计工具。它可作为一个模块库嵌入在Matlab/Simulink中,方便我们在Simulink/DSP Builder环境中进行图形化设计和仿真验证,同时又可通过Signal Compiler模块把 Matlab/Simulink的设计文件(.mdl)转换成相应的硬件描述语言VHDL设计文件(.vhd),并生成用于控制综合与编译的TCL脚本。该TCL脚本可以由Altera公司的 FPGA/CPLD开发工具 Quartus II来处理完成[4]。

DSP Builder平台的设计目的是采用图形化界面,方便学生通过搭建Simulink/DSP Builder模块从而实现硬件下载的功能。

考虑到系统的稳定性和软件的兼容性,我们选用的设计环境由Matlab 2008a,Altera DSP Builder 8.1,ModelSim Altera Edition 8.1,Quartus II 8.1 组成,学生只需要熟悉Matlab/Simulink的界面和常见模块的功能,就可以快速进入DSP Builder的设计中。

1.2 设计流程

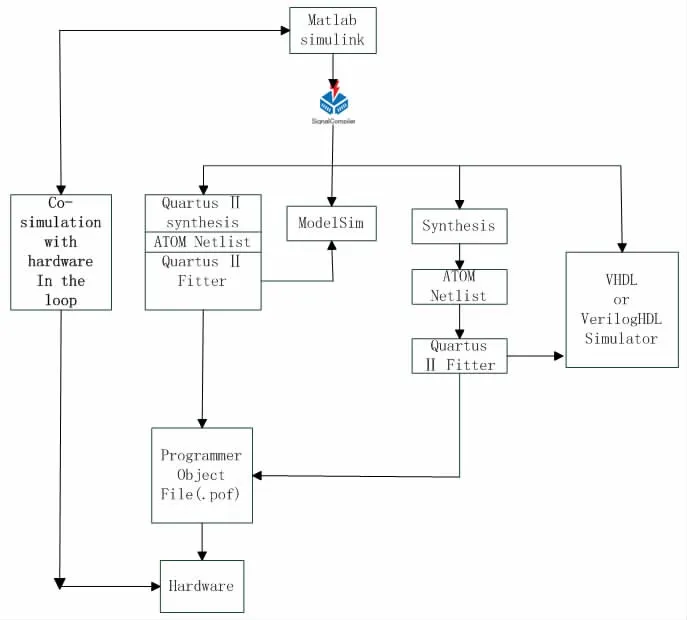

DSP Builder系统级设计流程如图1所示。

图1 DSP Builder系统级设计流程

设计流程包括如下三个部分。

1)搭建系统模型

(1)在 Matlab/Simulink2008a软件下生成由Simulink与DSP Builder模块组合的.mdl模型文件;

(2)在Simulink中,使用Scope模块观测仿真结果,并进行验证和评估。

2)编译和综合

(1)运行Signal Compiler模块进行RTL仿真和综合;

(2)执行RTL仿真,DSP Builder支持带有TCL脚本的ModelSim自动化仿真流程;

(3)使用由DSP Builder Signal Compiler模块生成的输出文件来执行RTL综合。对于带有TCL脚本的 Quartus II,Synthesis,Precision RTL Synthesis或LeonardoSpectrum软件,DSP Builder支持自动化综合流程。作为选择,还可以使用其它的综合工具,手工综合 VHDL 文件[5];

(4)在Altera的Quartus II软件中编译设计。

3)下载并测试

(1)采用JTAG方式下载到硬件开发平台上;

(2)测试和验证系统功能。

2 测试平台软件设计

2.1 利用DSP Builder设计AM调制

用DSP Builder搭建的AM调制模块如图2所示。该设计模块简单,系统直观,易于学习。

图2 DSP Builder AM调制模块

其主要设计模块由如下六个部分组成[6]。

(1)Signal Compiler模块,用于进行RTL仿真和综合;

(2)时钟模块和分频模块,时钟模块默认的频率是50MHz,分频模块将时种频率进行5分频得到10MHz的系统时钟;

(3)正弦波发生模块产生两个频率分别为10MHz和10KHz的正弦波,幅度为127;

(4)常数模块和加法器模块,常数模块设置参数为127,完成100%调幅,加法器模块设置输入参数为2,模式选择为加法模式;

(5)乘法器模块的两个输入信号分别是高频载波和低频调制信号;

(6)Scope模块用于观测输出的信号波形。

2.2 与编写Verilog实现的AM调制对比

本课程传统实验中AM调制是在Xilinx ISE平台上用Verilog编写实现的,如图3所示。对比DSP Builder的设计,用Verilog编写语言较为复杂,除了顶层文件的编写,还需要添加三个IP核。学生不仅要熟练掌握Verilog,还要熟悉如何调用IP核,进行参数设置。同时,由于要理解时钟时序,需要近一周的时间专门学习硬件语言,花费时间太长。

图3 Verilog AM调制

3 实验结果及分析

调制信号采用频率为10kHz的正弦波,幅度为127,载波采用10MHz的正弦波,可以得到调制度为100%AM调制信号。分别采用2.1和2.2两种方法,借助ModelSim仿真,结果对比采用如图4所示。

图4 仿真得到的调幅波形

图4(a)是利用Altera的DSP Builder平台搭建模块,采用ModelSim仿真得到的AM调制波形。图4(b)是采用Xilinx的ISE平台,编写Verilog代码,利用测试文件,在ModelSim仿真得到的AM调制波形,两者调制效果完全一样。比较上述两种方法,DSP Builder平台采用模块、图形化界面,其学习快,效率高。

4 结语

综上所述,本文所介绍的采用图形化编程工具DSP Builder,可让设计者先在Matlab中完成算法设计,在Simuink中完成系流集成仿真。用它来开发软件无线电测试平台软件,具有快速入门、编程效率高,且设计界面美观友好的优点。利用该软件进行实验,可以提高实验教学的效率。该系统已经使用于软件无线电的实验项目中,取得了良好的效果。

[1] 杨小牛,楼才义,徐建良.软件无线电技术与应用[M].北京:北京理工大学出版社.2010.4

[2] Mitola Joe.Software radio architecture[J].IEEE Communication-Magazine,NewYork,May 1995:6-38

[3] Buracchini Joe.Software Radio Concept[J] .IEEE Communication,NewYork,Sep.2000:138-143

[4] 潘松.现代DSP技术[M].西安:西安电子科技大学出版社,2003

[5] Tu Ya,Zhou Runjing,Zhang Guanying.Design of Electrotherapeutical Signal Generator Based on DSP Builder.Information Technology and Applications in Biomedicine,2008.30-31

[6] Guohai Xiong,Xuejun Zhou,Peirong Ji.Implementation of the Quadrature Waveform Generator Based on DSP Builder.Intelligent Information Technology Application Workshops,2008,21-22