基于FPGA和DSP的数据流转换系统设计

阳代华, 徐家品

(四川大学 电子信息学院,四川 成都 610065)

0 引言

随着现代通信技术和网络技术的不断发展,电信传输网和数字数据网之间的关系越来越密切,用电信网承载数据网络的业务,或者用数据网承载话音业务。E1系统是中国和欧洲国家电信传输网一次群使用的传输系统,E1信号由32个64 Kb/s的PCM话路经过时分多路复用形成,速率为2.048 Mb/s[1]。将E1信息流与以太网进行无缝连接,是三网融合大环境下发展的必然趋势。

1 系统硬件

1.1 硬件的选择

FPGA具有体系结构和逻辑单元灵活、集成度高以及适用范围宽等特点。该设计FPGA芯片采用的是Xilinx公司的 Spartan 3E 系列的 XC3S1200E[2]芯片,完成采集、缓存、收发TDM窄带E1数据。FPGA器件外接E1电缆,只负责数据的采集,可达到非常理想的采样效果。数据采集模块与DSP数据处理模块通过EMIF接口通信。DSP器件采用TI公司的DSP芯片TMS320VC5509[3]作为系统的数据流处理器, 实现对采集来的数据进行格式处理,并重新打包。设计有以RTL8019AS芯片为核心的以太网接口电路,方便了以太网的连接,实现数据流转换后在以太网上传输。电源采用5 V供电,3.3 V,1.8 V等电源采用二次电源芯片获得。

1.2 系统硬件平台的搭建

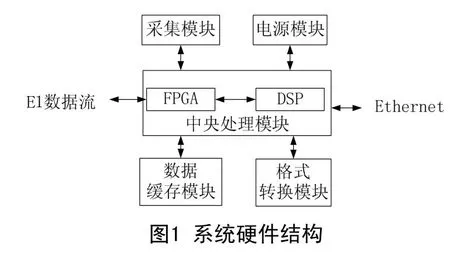

数据流转换的硬件组成如图1所示。

1.3 器件接口配置

这里设计时采用E1电缆连接FPGA差分信号输入端,并采用电平转换芯片将差分信号转为LVTTL标准的单端电平再由FPGA采样。DSP的EMIF接口资源[4],使用16位模式,EMIF的CE0空间为RTL8019,通过此片选配置RTL8019以及从以太网口收发数据;EMIF的CE1空间连接FPGA,通过CE1片选访问FPGA的状态寄存器,环回测试寄存器以及E1数据缓存器。对16 bit宽的外部存储器,作16 bit数据访问时的数据传输时,EMIF的外部地址线A[21:1]对应于内部数据地址的bit21-1。数据线D[15:0]在DSP和外部存储器之间传输数据。在一次访问期间,BE3和BE2始终保持高电平(无效),BE1和BE0被拉低。

2 系统软件的设计

2.1 FPGA采样

DSP采样属于软采样,需要定时去判断输入的信号,由于TDM系统需要严格的时钟同步关系,否则会产生滑码错误,但是FPGA采样属于硬件采样,相当于一个只因E1输入信号变化而变化的逻辑,不受芯片其他部分程序的影响。由于可编程逻辑器件FPGA内部拥有强大的可编程资源,很多控制功能都可以集成在FPGA的内部[5]。因而本设计通过Verilog HDL语言配置产生一个8.192 MHz的精确时钟,本地晶振的时钟作为参考时钟,在每个8 MHz时钟的上升沿采样,如果采样到1则采样计数器加1,在2 MHz时钟的上升沿判断是否有3次或者4次采样到1,如果是,则采样数据为1,否则采样数据为0,并清零采样计数器,循环重复进行下一次采样计数。

在 E1信道中,8 bit组成一个时隙(TS),由32个时隙组成了一个帧(F),在一个帧中,TS0 主要用于传送帧定位信号(FAS)、CRC-4(循环冗余校验)和对端告警指示,TS16主要传送随路信令(CAS)、复帧定位信号和复帧对端告警指示,TS1至TS15和TS17至TS31共30个时隙传送话音或数据等信息。其中TS0为x0011011时定义为一帧的开始,否则视为E1线路上没有信息传送。

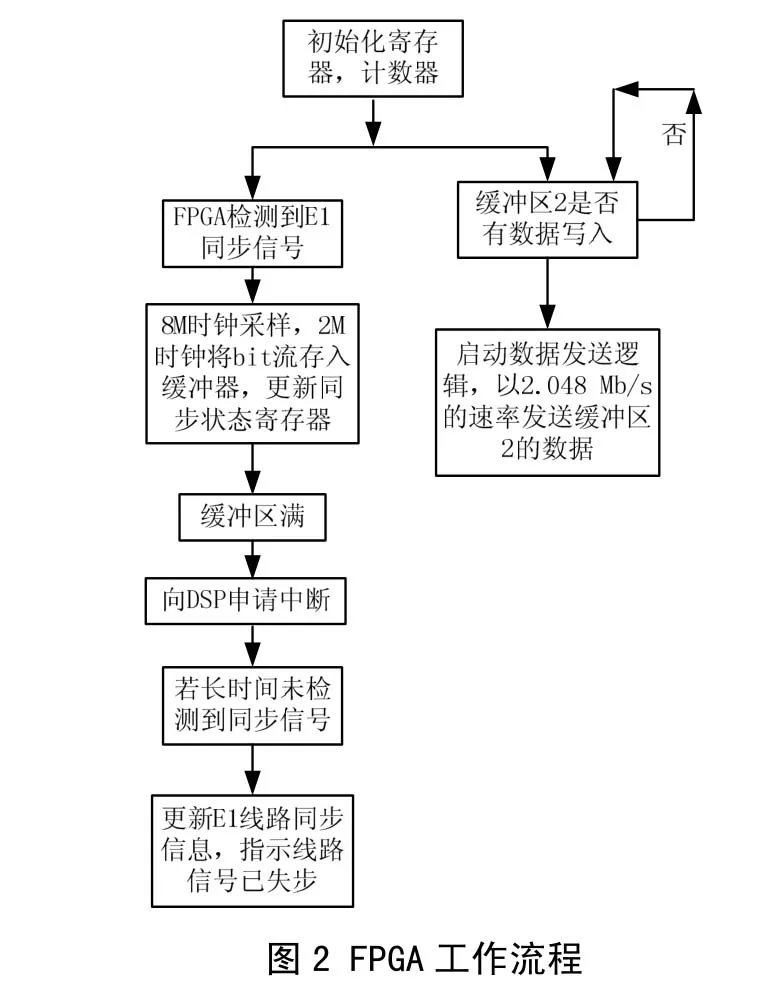

当FPGA检测到E1同步TS0信号时,采样数据,存入PCM数据缓冲寄存器并更新状态寄存器,当缓冲区满则向DSP发出中断请求,申请DSP取走数据。外部中断1用于FPGA的中断申请,当收到FPGA的中断申请时,从FPGA的缓存中读取32帧即1KB的数据,通过EMIF口传递给DSP;数据缓冲器2用于接收DSP侧传来的数据,当FPGA检测到缓冲器有数据写入时,启动数据发送逻辑将数据以2.048 Mb/s的速率将数据发送到E1线路上。并通过指示灯LED的闪烁频率指示处理UDP包的速度。具体工作流程如图2所示。

2.2 DSP数据处理流程

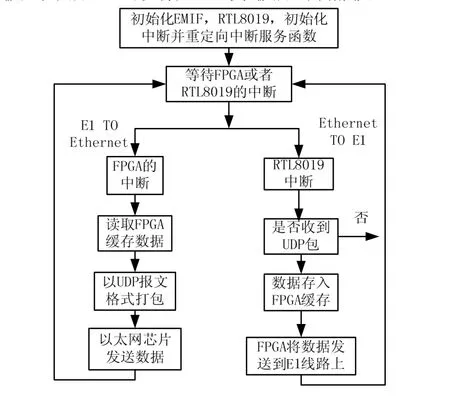

数据流从E1到达以太网的处理流程,当FPGA采集到数据,通过外部中断INT1申请DSP取走数据,DSP通过EMIF口取走数据。然后DSP对数据进行报文头组装,包括组装IP报头和UDP报头[6],重新封装后通过以太网将数据发送出去。数据流经以太网传到E1线路的处理流程,当RTL8019收到UDP数据包,通过中断INT0申请中断。外部中断0用于处理以太网PHY芯片RTL8019的中断请求,当收到中断时,DSP调用中断服务程序,从网络端接收到的 RTP 数据解包成DSP可识别的PCM 数据包[7],并封装成E1的帧格式写入FPGA的缓存。具体流程参见图3示。

3 实验结果分析

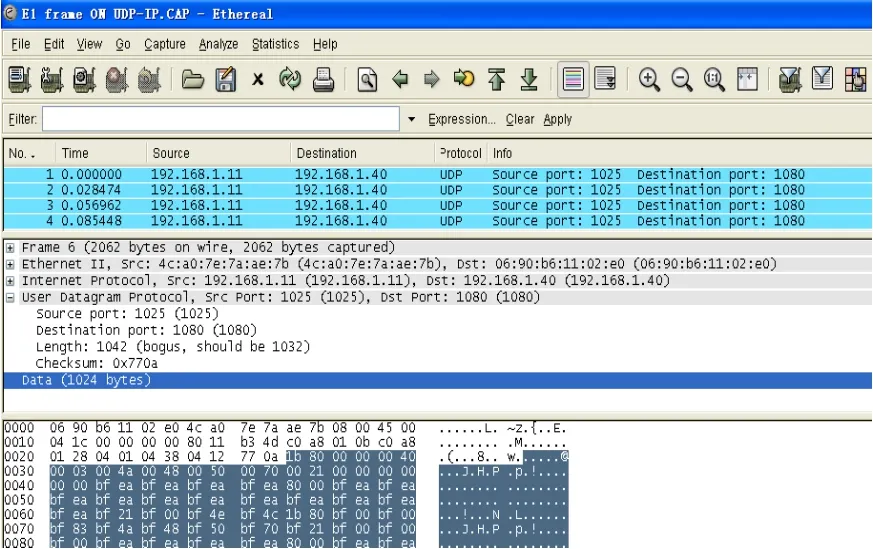

程序调试成功后,可以通过JTAG将编译好的文件系统下载到开发板,启动开发板即可进行E1数据流的传输。该设计采用一路E1数据流传输,分别将原端IP和目标端IP配置为{0xA8C0,0x0B01}和{0xA8C0,0x2801},并调用1025、1080端口[6],在PC机上运行Ethereal软件抓包可分析数据包的正确性。由图4可见,从E1电缆传来的信号经本方案设计,成功被封装成UDP数据包,并被成功捕获。

图3 DSP数据处理流程

图4 UDP数据包截图

4 结语

通过使用FPGA采样缓存E1线路信号,并以UDP报文形式从以太网口抓包确认数据的正确性,为TDM的E1信息与包形式传输的UDP报文2种不同的媒体流之间,提供了一种可实现的转换。并且可以此为基础,进一步实现G.711、G.726、G.729等不同速率的媒体流在以太网上传输[8]。在通信网络从传统的TDM电路交换演化到以以太网为基础的包交换的过程中,可节约已有的投资,实现网络的平滑过渡。

[1] 吴小艨.E1 线路接口设计与保护[J].信息安全与通信保密,2006(10):76-78.

[2] XILINX. Spartan-3E FPGA Family [DB/OL].(2008-04-18)[2012-03-20].http://china. xilinx.com/support/documentation/datasheets.

[3] TEXAS Instruments. TMS320VC5509 Fixed-Point Digital Signal Processor [DB/OL].(2008-01-22)[2012-03-20]. http://www.ti. com.cn/product/cn/tms320vc5509a.

[4] Texas Instruments Incorporated. TMS320VC55X系列DSP的CPU与外设[M].北京:清华大学出版社,2005:191-217.

[5] 雷明,马游春,李锦明.基于FPGA的多通道图像采集存储系统设计[J].通信技术,2010,43(04):204-207.

[6] 谢希仁.计算机网络[M]. 北京:电子工业出版社,2008:184-186.

[7] 李浩,蔡德林,王古.基于DSP 和FPGA的 Roip网关的设计与实现[J].通信技术,2010,43(05):143-144.

[8] 章波焕,朱健军,孟利民,等.基于FPGA 技术的以太网远程网桥的实现[J].电子技术,2003(02):19-21.